За более чем десятилетний срок работы с ПЛИС, мне довелось работать с продукцией четырех разных производителей. При таком разнообразии невольно обращаешь внимание как на общие черты процесса разработки, так и на особенности, присущие той или иной компании. И вот, пару месяцев назад мне неожиданно представилась уникальная возможность близко познакомиться с новым семейством ПЛИС, производимым небольшой, но амбициозной компанией из Калифорнии. Я говорю сейчас о самом молодом производителе ПЛИС – компании Акроникс (Achronix) и выпускаемой ею ПЛИС Speedster22i HD1000.

С момента своего создания (2004 г.), эта молодая компания смогла разработать ПЛИС сегмента HI-End, обладающие оригинальной архитектурой и уникальными характеристиками. Более того, компания первой среди всех производителей ПЛИС заключила стратегический союз с корпорацией Интел и с тех пор производит свои микросхемы (размер которых, как видно из рисунка, уже давно вышел за рамки “микро”) на самой совершенной технологической базе Intel на заводах, расположенных непосредственно в США. Сейчас серия Speedster выпускается по технологии 3D Tri-Gate 22нм. Программа развития серии предусматривает в недалеком будущем переход на 14нм и 10нм техпроцессы (по мере их освоения на заводах Интел).

В этой обзорной статье я хочу кратко описать, с одной стороны, те продукты которые используются для работы с ПЛИС Speedster, а с другой – свой опыт (включая эмоции) работы с этими продуктами на примере очень простого, но реально выполненного проекта. Итак …

“Железо” и средства разработки

Пожалуй, единственный на сегодняшний день способ ознакомиться с ПЛИС Speedster22i в работе – это купить (получить в подарок, арендовать, взять в лизинг …) отладочный набор Speedster22i HD1000 Development Kit, что мы и сделали. В процессе ожидания доставки была проделана подготовительная работа: закуплен мощный компьютер с водяным охлаждением, 32GB ОЗУ и двумя мониторами. Для того, чтобы получить средства разработки, пришлось зарегистрироваться на сайте Achronix (http://www.achronix.com/company/contact-us.html) и получить пользовательский аккаунт. Пользовательский аккаунт открывает доступ в зону сайта, содержащую необходимое для работы программное обеспечение, а так же демонстрационные и ссылочные дизайны. В чем между ними разница? Ссылочные дизайны (reference designs) поставляются с исходными кодами для ПЛИС, в то время как демонстрационные (demodesigns) как правило, содержат только загрузочные файлы для ПЛИС.

Подтверждение регистрации заняло пару дней и завершилось получением письма, содержащего логин и пароль. После этого появилась возможность скачать необходимые для начала работы средства – собственную оболочку компании Achronix под названием ACE и синтезатор Synplify. Но для того, чтобы эти программы заработали, к ним необходимы еще файлы лицензии. Для этого требуется заполнить еще одну форму и указать MAC-адрес сетевой карты. Файлы лицензии присылаются по электронной почте. Их подключение тоже не вызвало никаких проблем, кроме того, этот процесс подробно описан в документации. На моем компьютере установлена ОС Windows, но средства разработки имеются и для Rad Hat Linux.

Оставшееся до прибытия платы время было посвящено изучению архитектуры ПЛИС Speedster22i HD1000, освоению средств проектирования и написанию простого дизайна.

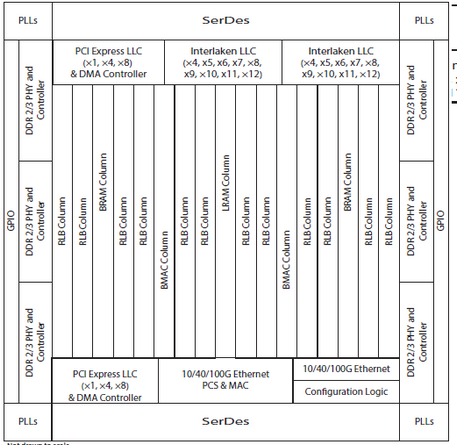

Чем интересна серия Speedster22i? Что отличает ее от изделий других компаний? ПЛИС Speedster22i имеет свою “изюминку” – аппаратные IP-ядра, ориентированные на высокоскоростные коммуникационные задачи. По наборам таких ядер ПЛИС Achronix до сих пор вне конкуренции. Номенклатура ядер: DDR-3 – 6 шт., PCI Express Gen1/2/3 x1, x4, x8 – 2 шт., Ethernet MAC до 100G – 2 шт, Interlaken – 2 шт.. При этом обеспечивается суммарная пропускная способность свыше 400 Gb/s, что, безусловно, позволяет отнести ПЛИС серии Speedster22i к категории HI-END.

В остальном, рассматриваемые ПЛИС по своей структуре не сильно отличаются от продукции других производителей: они состоят из логических кластеров (на основе 4х-входовых LUT), блочной и распределенной памяти, а так же арифметических блоков, включающих мощные 56-битные умножители. Все это имеется в достаточных количествах для достижения самой сложной функциональности. Скоростные характеристики так же впечатляют: память, например, имеет максимальную рабочую частоту 750 МГц. Основные характеристики ПЛИС серии Speedster22i приведены в нижеследуюющей таблице:

| Параметры | HD680 | HD1000 | HD1500 |

| Объем логики, включая аппаратные контроллеры (эффективных ячеек LUT) | 660000 | 1045000 | 1725000 |

| Объем программируемой логики (в LUT) | 400000 | 700000 | 1100000 |

| Количество модулей BRAM | 600 | 1026 | 1728 |

| Количество модулей LRAM | 4320 | 6156 | 10368 |

| Объем 80-и килобитных BRAM (всего Kбит) | 48000 | 82080 | 138240 |

| Объем 640-битных LRAM (всего Kбит) | 2765 | 3940 | 6636 |

| Умножителей (28×28) | 240 | 756 | 864 |

| Количество линий SerDes 12.75 гб/с (Гигабит/с) | 40 | 64 | 48 |

| Количество линий SerDes 28 гб/с (Гигабит/с) | - | - | 16 |

| Аппаратных контроллеров Ethernet (MAC-уровень) 10/40/100 Гигабит/с | 2 | 2 | 4 |

| Контроллеров Interlaken LLC | 1 | 2 | 4 |

| Контроллеров PCI Express LLC | 1 | 2 | 2 |

| Контроллеров DDR2/DDR3 | 4 | 6 | 6 |

| Количество PLL | 16 | 16 | 16 |

| Количество выводов, корпус FBGA2601 52.5×52.5 (12G,28G,GPIO) | - | 64,0,960 | 48,16,960 |

| Количество выводов, корпус FBGA1936 45×45 (12G,28G,GPIO) | 40,0,684 | 40,0,684 | 20,4,684 |

| Количество выводов, корпус FBGA1520 40×40 (12G,28G,GPIO) | 18,0,684 | - | - |

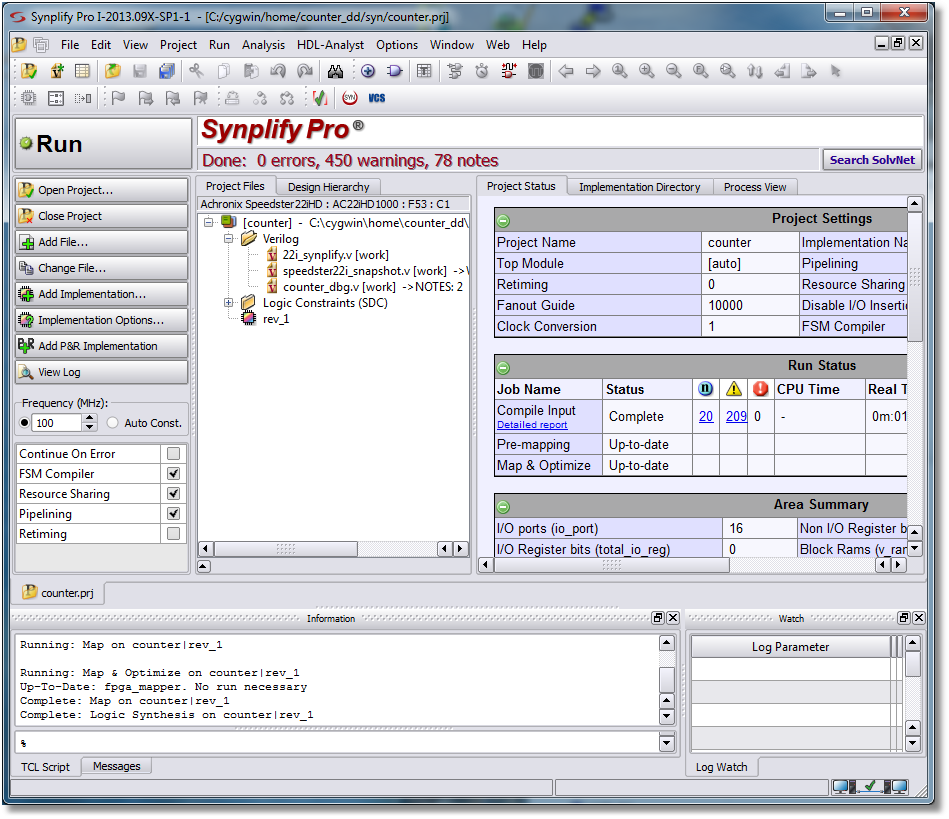

Минимально необходимый набор средств разработки включает в себя две программы – оболочку ACE и синтезатор Synplify. Собственная разработка компании — оболочка ACE включает в себя средства размещения и разводки, конфигурирования ядер, загрузки и отладки. В качестве синтезатора используется программа Synplify от Synopsys. Подход, заключающийся в использовании набора отдельных программ вместо единой интегрированной среды, характерен для небольших компаний. Он менее удобен для начинающих разработчиков, но для опытных инженеров дает большую гибкость и лучшее качество выполнения каждого этапа. Если же необходима более глубокая интеграция, все требуемые программные средства можно объединить, например, посредством оболочки HDL-designer от MentorGraphics.

К указанным программам желательно добавить какую-либо программу-симулятор. Пакет Achronix содержит библиотеки для самых популярных программ-симуляторов, но сами эти программы в комплект поставки не входят и приобретаются отдельно.

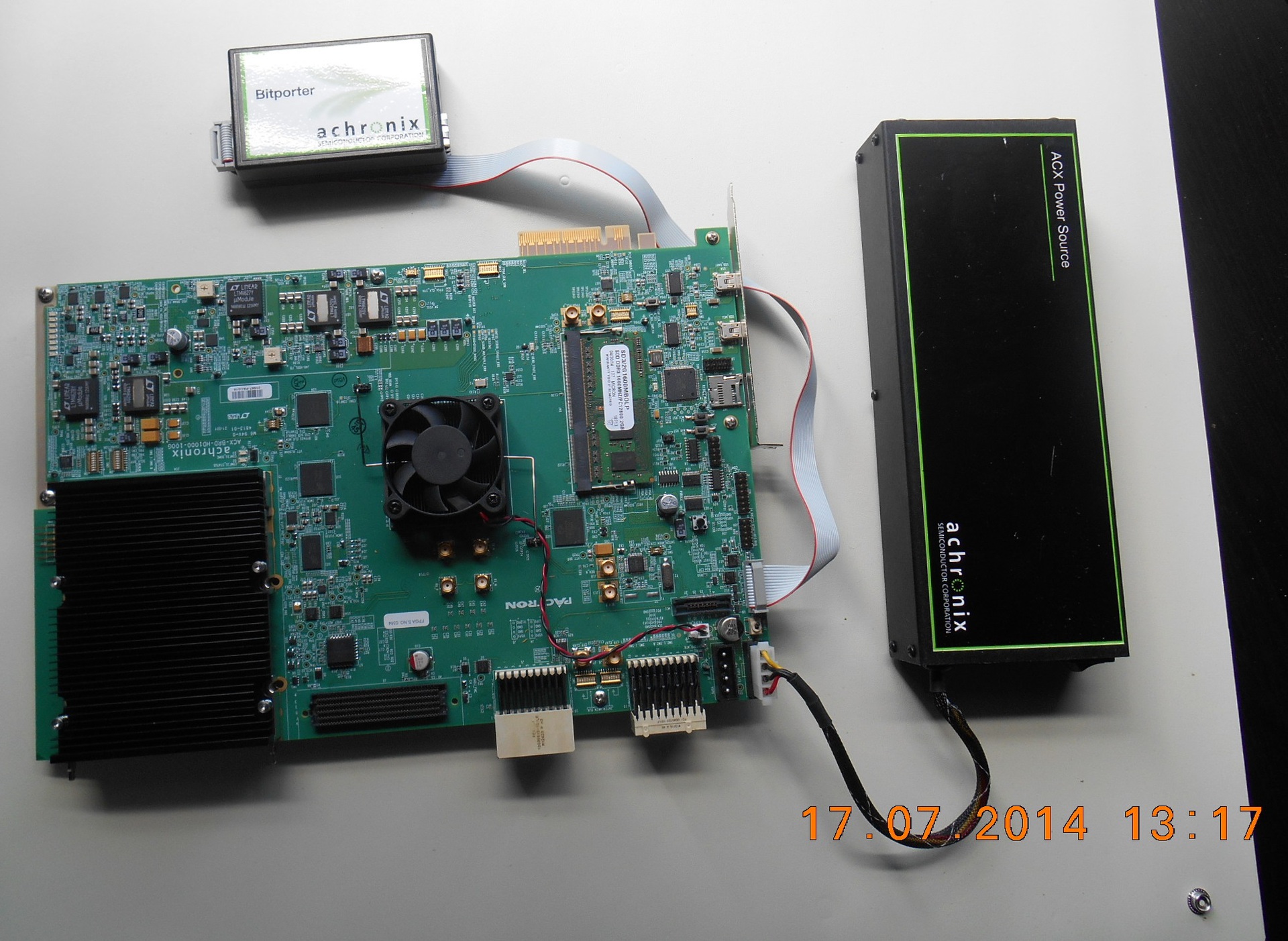

И вот, наконец, долгожданная плата прибыла в наш офис!

Дрожащими от волнения руками (а как не волноваться, когда цена у платы как у недорогого импортного кроссовера! ), плата была распакована, перенесена на свое “штатное” место – на антистатический коврик на моем рабочем столе и с интересом рассмотрена.

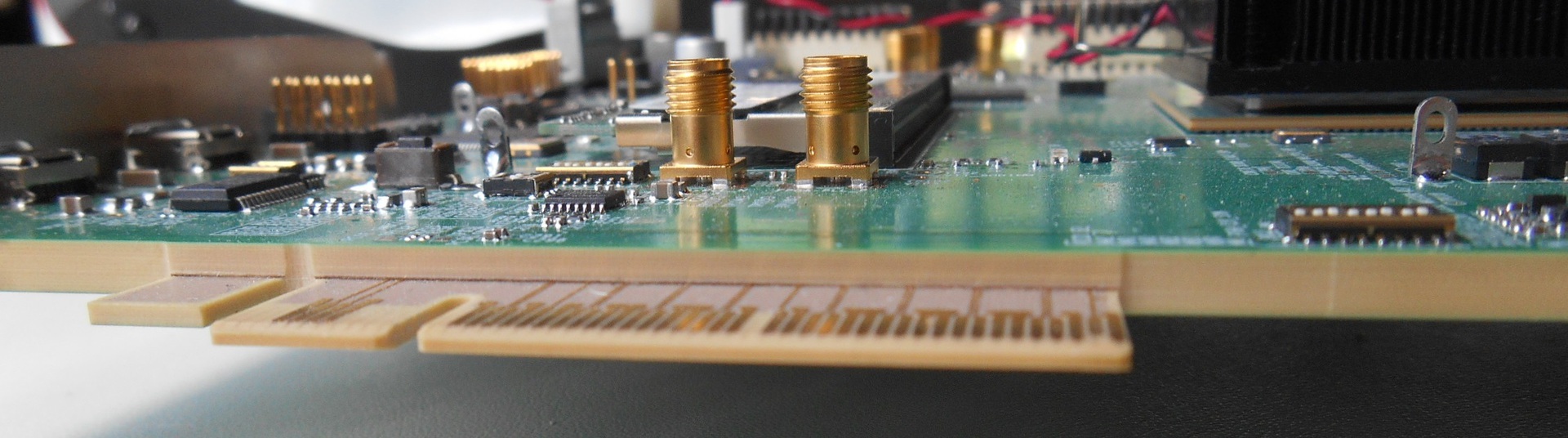

Как видно, сама плата представляет собой сложное и многофункциональное изделие. Одна только электрическая схема занимает 90 страниц! Поэтому не удивительно, что плата позволяет разрабатывать и отлаживать, не побоюсь этого слова, уникальные проекты, например, создавать оборудование для сетей Ethernet 100G, для чего имеется разъем для модуля CFP (“черный квадрат” в нижнем левом углу на фото вверху ). Два интерфейса Interlaken выведены на разъемы AirMax.

Больше всего поразила толщина печатной платы. Сколько же здесь слоев? 20? 30? 40? Вопрос так и остался невыясненным.

Плата имеет разъем PCI-express (Gen 3 x8, 64 Gb/s) и может работать в качестве периферийного устройства в составе компьютера. Все вместе это выглядит вот так:

В комплект поставки входит JTAG-кабель, выполняющий функции загрузчика и отладчика. Особенностью этого кабеля является возможность работать через USB-порт, либо через Ethernet. В последнем случае можно организовать удаленный доступ к устройству. При работе через Ethernet требуется внешний источник питания (входит в комплект поставки). Так же в комплект поставки входят мощный источник питания для самой платы и модуль DDR-3 RAM на 2GB.

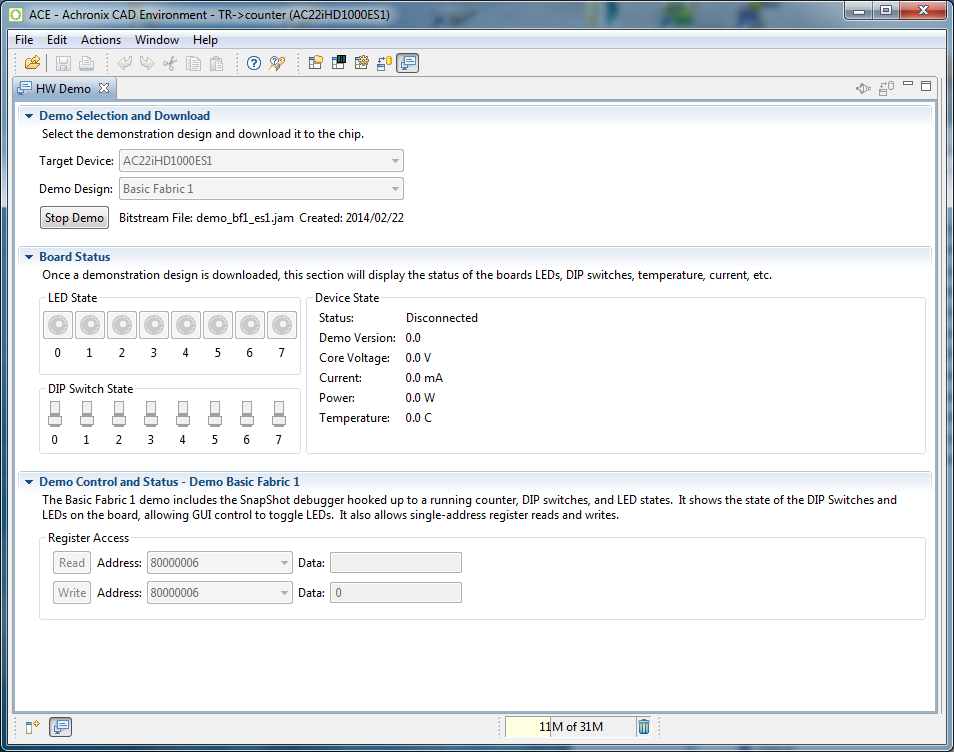

Проверка работоспособности

Проверить, что плата функционирует оказалось очень просто, т.к. в оболочку ACE уже встроен для нее тест. Поэтому вся проверка, по сути, сводится к нажатию одной кнопки для загрузки тестовой прошивки. После этого можно поиграть переключателями, включая и выключая светодиоды и протестировать блоки внутренней памяти. Плата при этом должна быть соединена USB-кабелем с компьютером.

Разработка

А теперь – о том, как я делал свой первый проект для ПЛИС Achronix. В качестве такового был выбран наипростейший вариант – счетчик с выводом старших разрядов на светодиоды. Конечно, такой простой проект не произведет впечатление на профессионалов, но он позволяет изучить базовую функциональность применяемых для работы с ПЛИС Achronix средств разработки и освоить маршрут проектирования. В будущих публикациях я планирую рассказать о более сложных вещах, таких как конфигурирование и использование аппаратных ядер и реализацию систем на кристалле с использованием процессорного ядра ARM.

Структура проекта

Каждый проект я размещаю в отдельном каталоге, содержащем, как минимум, 3 подкаталога:

- Src – для исходных текстов

- Syn – для синтеза

- TR – для имплементации

Практика показала, что в каталоге Syn лучше ничего лишнего не держать, ибо размещенные там файлы синтезатор может затереть. Поэтому исходные тексты (предпочитаю работать на языке Verilog) я храню в каталоге Src, а все скрипты – в каталоге TR

Исходные тексты

Исходный код модуля совершенно незамысловатый:

module counter #( parameter CNT_WIDTH = 32 ) // 8 <= CNT_WIDTH

(

input wire clk,

input wire rstn,

output wire [7:0] leds

);

wire rst;

reg [CNT_WIDTH-1:0] cnt;

assign rst = ~rstn;

always @(posedge clk or posedge rst)

if (rst) cnt <= 'h0;

else cnt <= cnt+1;

assign leds[7:0] = cnt[CNT_WIDTH-1: CNT_WIDTH-8];

endmodule

Но для имплементации на демонстрационной плате его необходимо чуть-чуть модифицировать.

Во-первых, необходимо выбрать и правильно подключить источник тактового сигнала. Их на плате — несколько. После изучения был выбран источник частотой 100МГц, имеющий дифференциальный выход. Следовательно, необходимо было добавить во входную тактовую цепь дифференциальный буфер.

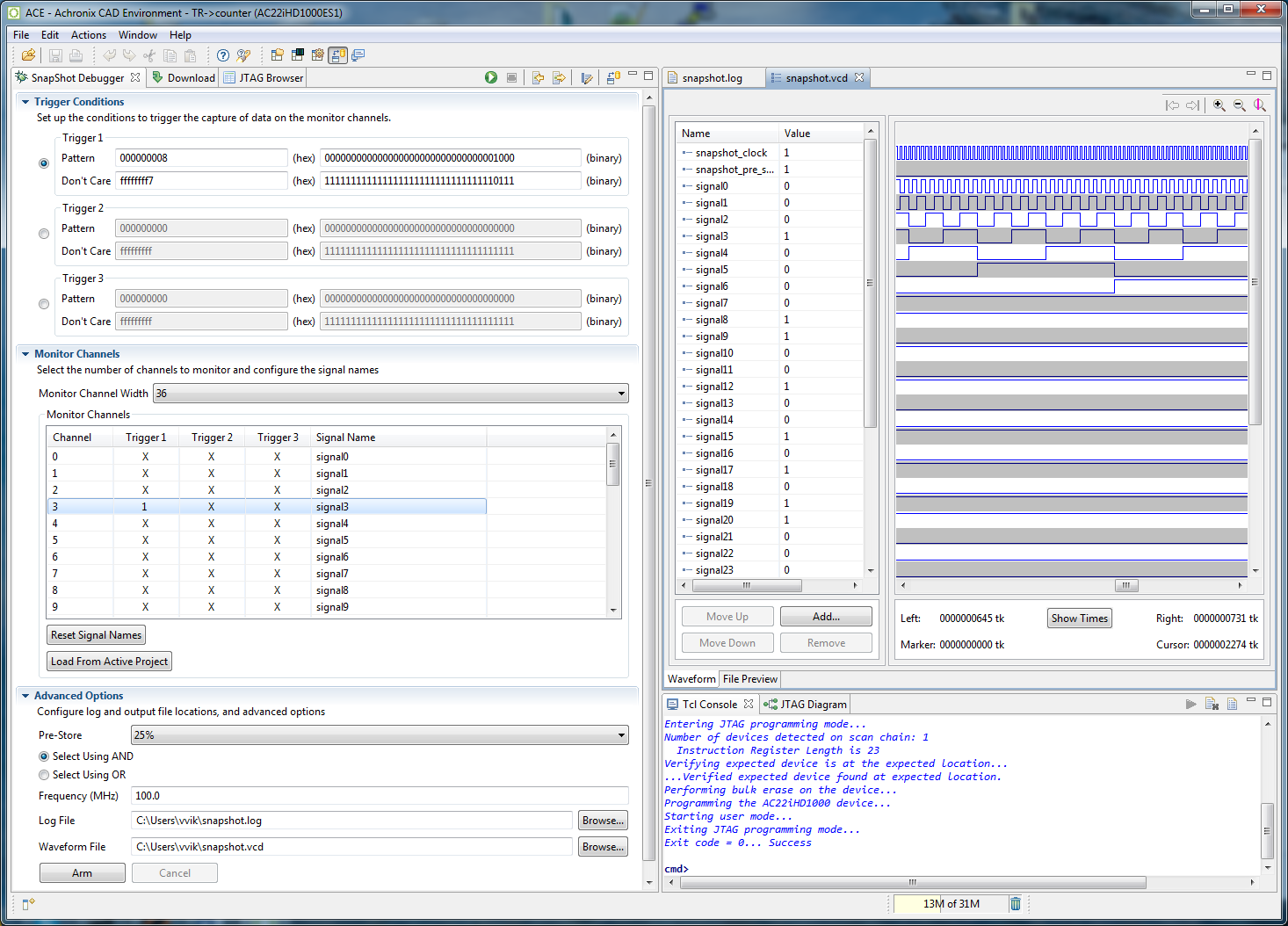

Во-вторых, хотелось бы увидеть внутренние сигналы в процессе работы. Такая возможность есть у всех производителей ПЛИС, имеется она и в ПЛИС Achronix. Внутренний анализатор сигналов называется SnapShot. В отличие от конкурентов, компонент SnapShot должен быть явно описан в дизайне. Это поначалу вызывало у меня неудобство, но затем я оценил преимущество такого подхода. Это преимущество заключается в полном контроле над тем, что ты делаешь. Кроме того, такой подход позволяет очень гибко настраивать триггеры для регистрации отслеживаемых событий.

Итак, в окончательном варианте у нас появляется дифференциальный тактовый вход и буфер для него, а так же компонент ShapShot для изучения внутренних сигналов. Окончательный текст на языке Verilog:

`define USE_SNAPSHOT

module counter #( parameter CNT_WIDTH = 30 ) // 8 <= CNT_WIDTH <= MNTR_WIDTH

(

`ifdef USE_SNAPSHOT

input wire tck,

input wire trstn,

input wire tms,

input wire tdi,

output wire tdo,

`endif

input wire clk_p,

input wire clk_n,

input wire rstn,

output wire [7:0] leds

);

//**********************************************

wire clk;

wire rst;

reg [CNT_WIDTH-1:0] cnt;

assign rst = ~rstn;

IPAD_DIFF #( .odt("on"), .termination("100") )

synth_clk_pad ( .pad(clk_p), .padn(clk_n), .dout(clk) );

always @(posedge clk or posedge rst)

if (rst) cnt <= 'h0;

else cnt <= cnt+1;

assign leds[7:0] = cnt[CNT_WIDTH-1: CNT_WIDTH-8];

//*********************************************

`ifdef USE_SNAPSHOT

localparam MNTR_WIDTH = 36;

wire [MNTR_WIDTH: 0] ss_zeroes; ///// Signals going to trigger-detector block to do pattern matching

wire ss_clk;

wire [MNTR_WIDTH-1 :0] ss_monitor_ch; /// Signals monitored in Snapshot

wire [MNTR_WIDTH-1: 0] ss_trigger_ch; ///// Signals going to trigger-detector block to do pattern matching

wire ss_rstn_out; ///// Active low user reset signal.

wire ss_Arm; ///// Indicates Snapshot activity.

wire [MNTR_WIDTH-1:0] ss_Stimuli; ///// User specified values for 3rd trigger pattern value

assign ss_clk = clk;

assign ss_zeroes = {MNTR_WIDTH+1{1'b0}}; ////

//////// Now Snapshot macro block instantiation ///////

ACX_SNAPSHOT #(.MNTR_WIDTH(MNTR_WIDTH) )

snapshot_0 (

.tck ( tck ),

.tms ( tms ),

.trstn ( trstn ),

.tdi ( tdi ),

.tdo ( tdo ),

.usr_clk ( ss_clk ),

.Monitor_ch ( ss_monitor_ch ),

.trigger_ch ( ss_trigger_ch ),

.Rstn_out ( ss_rstn_out ),

.Arm ( ss_Arm ),

.Stimuli ( ss_Stimuli )

);

assign ss_monitor_ch = { ss_zeroes[MNTR_WIDTH-1: CNT_WIDTH], cnt[CNT_WIDTH-1:0] };

assign ss_trigger_ch = ss_monitor_ch;

`endif

//**********************************************

endmodule

Синтез

Синтезатору Synplify для работы требуется кроме исходных текстов и ссылок на библиотеку элементов еще файл констрейнтов (обычно он имеет расширение .sdc). Хотя для такого простого дизайна он необязателен, все же его лучше указать. В таком простом случае, как у нас, требуется только указать имена тактового сигнала и их параметры.

# synplify_constraints.sdc

set_hierarchy_separator {/}

create_clock clk_p -period 10

create_clock tck -period 40

set_clock_groups -asynchronous -group { tck } -group { clk_p }

Далее создаем проект для Synplify, указываем требуемые для синтеза файлы и библиотеки и запускаем процесс. Если все сделано правильно, получаем выходной файл с расширением .vma. (“Гуру” FPGA-дизайна могут указать, что основным выходным форматом Synplify является edif. Но ACE принимает на входе только верилоговские нетлисты, которые как раз имеют расширение .vma)

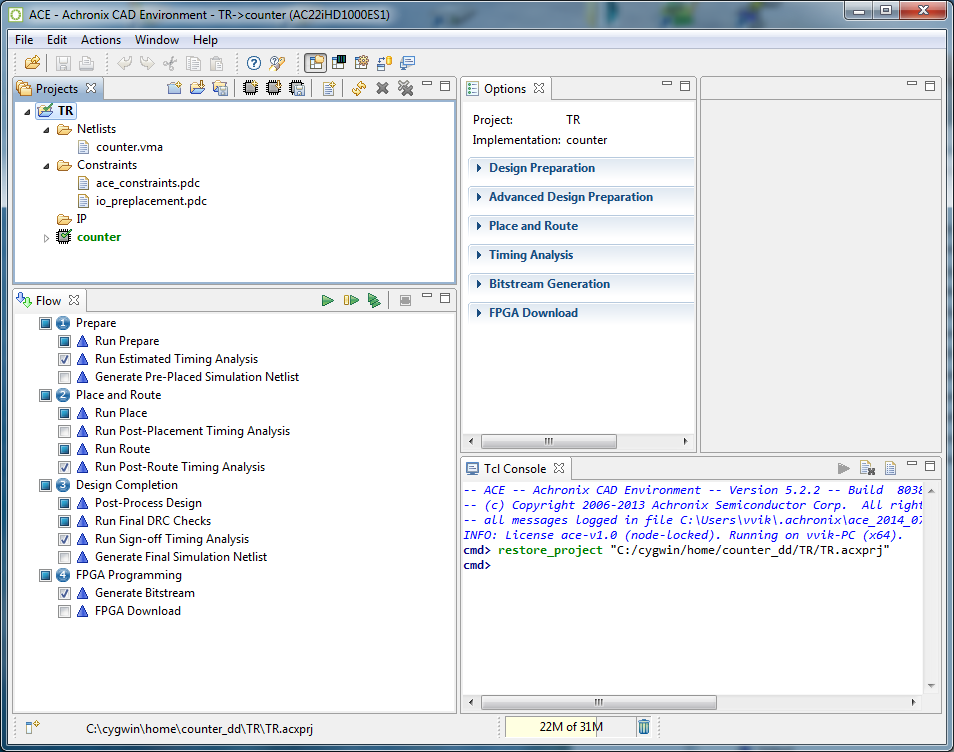

Имплементация

Собственно процесс имплементации осуществляется по стандартной схеме:

- Создаем проект для ACE

- Указываем в проекте файл результатов синтеза (с расширением .vma)

- Задаем констрейнты

- Запускаем процесс имплементации

- Получаем файл для загрузки в ПЛИС

Для имплементации необходимо подготовить два файла констрейнтов: для задания клоков и задания пинов. Их содержимое показано в таблице:

# Ace_constraints.pdc

create_clock clk_p -period 10

create_clock tck -period 40

set_clock_groups -asynchronous -group { tck } -group { clk_p }

# io_preplacement.pdc

set_placement -batch -fixed {p:clk_p} {b:P19}

set_placement -batch -fixed {p:clk_n} {b:P18}

set_placement -batch -fixed {p:rstn} {b:P17}

set_placement -batch -fixed {p:leds[0]} {b:AE47}

set_placement -batch -fixed {p:leds[1]} {b:AJ46}

set_placement -batch -fixed {p:leds[2]} {b:AC46}

set_placement -batch -fixed {p:leds[3]} {b:AF47}

set_placement -batch -fixed {p:leds[4]} {b:AF46}

set_placement -batch -fixed {p:leds[5]} {b:AJ47}

set_placement -batch -fixed {p:leds[6]} {b:AG46}

set_placement -batch -fixed {p:leds[7]} {b:AE46}

На компьютере этап имплементации выглядит следующим образом:

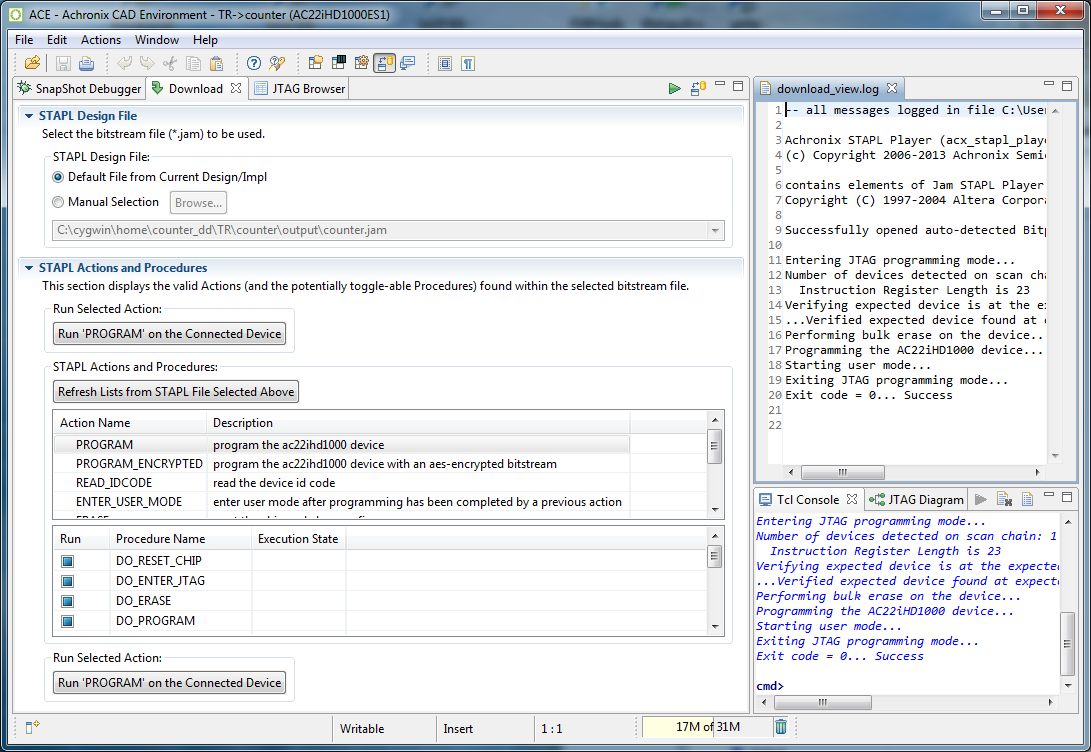

Загрузка дизайна и отладка

Чтобы загрузить созданный на предыдущем этапе файл прошивки, надо перейти в окно “Download”, нажать на кнопку “Run ‘Program’ ” и подождать пару минут.

После окончания загрузки ПЛИС сразу же начинает работать и мы можем наблюдать на плате линейку весело мигающих светодиодов.

Чтобы посмотреть внутренние сигналы, подключенные к модулю SnapShot, требуется открыть окно “Snapshot debugger”. В этом окне можно настроить режимы триггера захвата и другие параметры. Анализ запускается кнопкой “Arm”, после чего начинается отслеживание состояния триггера. После установки триггера, на экране (с небольшой задержкой) появляется временная диаграмма регистрируемых сигналов.

Заключение и выводы

За короткий срок компании Achronix удалось создать интересные, конкурентоспособные ПЛИС сегмента HI-END и средства разработки для них. Технология работы с ними не вызовет проблем даже у специалистов средней квалификации. Продукция компании Achronix уже доступна в России.

Ссылки

- Сайт Российского Представительства (“Лаборатория Высокопропускных СБИС”), url: www.achronix.ru

- Википедия, статья о компании Акроникс, url: ru.wikipedia.org/wiki/Achronix

- Семейство Speedster22i® HD, техническое описание, url: www.achronix.com/wp-content/uploads/docs/Speedster22iHD_FPGA_Family_DS004.pdf

- Руководство пользователя комплектом разработчика: Speedster22i HD1000 Development Kit User Guide, url: www.achronix.com/wp-content/uploads/docs/Speedster22i_DevelopmentKit_User_Guide_UG034.pdf

- Руководство пользователя отладчиком SnapShot: www.achronix.com/wp-content/uploads/docs/Speedster22i_Snapshot_User_Guide_UG016.pdf

- Схема электрическая принципиальная отладочной платы: 22iHD1000_Development_Board_Schematic.pdf

- Сайт компании Achronix (на английском языке), url: www.acronix.com

Автор: fpgaFAE

![Мой опыт собеседования в Google [оффер на L5] Мой опыт собеседования в Google [оффер на L5]](https://www.pvsm.ru/wp-content/plugins/contextual-related-posts/timthumb/timthumb.php?src=http%3A%2F%2Fwww.pvsm.ru%2Fimages%2F2023%2F12%2F05%2Fmoi-opyt-sobesedovaniya-v-Google-offer-na-L5.jpg&w=100&h=100&zc=1&q=75)