Вчера все отечественные сайты облетела новость о том, что в России Микроном разработана технология производства микросхем по нормам 65нм (или даже «В России выпущены первые 65-нм микросхемы»). Ранее Микрон имел лицензированную у STMicroelectronics технологию 90нм. Попробуем чуть детальнее разобраться, как там обстоят дела.

Вчера все отечественные сайты облетела новость о том, что в России Микроном разработана технология производства микросхем по нормам 65нм (или даже «В России выпущены первые 65-нм микросхемы»). Ранее Микрон имел лицензированную у STMicroelectronics технологию 90нм. Попробуем чуть детальнее разобраться, как там обстоят дела.

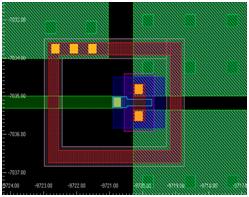

Микрон на этот раз на удивление опубликовал достаточно много информации. На фотографиях — разметка одного тестового транзистора и фотографии сделанные электронным микроскопом. Под катом — посмотрим, как это можно было сделать и сравним с Intel 65nm.

|

|

|

Сравнение техпроцессов

Микрон опубликовал таблицу с параметрами их техпроцесса. Для сравнения, я добавил техпроцесс Intel 65нм:

| Технология | Микрон 65нм | Микрон 90нм | Intel 65нм |

| Gate length | 45нм На фотографии 54нм |

65нм | 35-38нм +SiGe stress |

| Gate oxide thickness (electrical) | 2.2nm (n) / 2.2nm (p) | 2.2nm (n) / 2.2nm (p) | 1.2nm SiON |

| Interconnect | 9-Cu + 1-Al | 7-Cu + 1-Al | 8-Cu |

| Metal 1 pitch | 0.18µm | 0.24µm | 0.21µm |

| Inter-level dielectric | k = 2.9 | k = 2.9 | k=2.9 |

M1 pitch (шаг первого уровня металлизации) вызывает некоторое сомнение — при уменьшении шага металла M1 менее 0.2-0.3мкм резко падает скорость работы микросхемы из-за увеличения RC-константы, потому Intel и не стал его уменьшать менее 0.21-0.22мкм. Очередное напоминание, что именно межсоединения являются основным тормозом прогресса микроэлектроники.

Длина затвора и толщина подзатворного диэлектрика говорит о том, что это LP техпроцесс — с низким потреблением и меньшей скоростью работы. Так что сделать процессор, аналогичный первым Core2Duo на Микроне пока не выйдет, но и для LP техпроцессов есть масса применений.

Количество металлов позволяет реализовывать процессоры любой сложности.

В погоне за 65нм

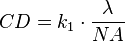

Как мы помним, разрешение оптической фотолитографии подчиняется критерию Релея:

На данный момент самая продвинутая установка фотолитографии на Микроне (сканер ASML PAS/1150C) имеет NA=0.75 и работает на длине волны 193нм. Параметр k — множитель используемых «ухищрений», позволяющих улучшить получаемое разрешение. k для фотолитографии без хитростей — 0.4. В случае Микроновских 90нм — k был уже 0.35. Чтобы с тем же сканером получить честные 65нм, k нужно было бы как-то снизить до 0.25 (т.е. добавить достаточно много хитростей).

Однако учитывая слова из пресс-релиза («были разработаны специальные алгоритмы внесения оптической коррекции фотолитографии»), обычной, классической топологии тестового транзистора (не используя «одномерные» структуры) и длину затвора на фотографии (54нм) — на данный момент похоже просто на текущем оборудовании без дополнительных хитростей сделали транзисторы с затвором меньшего размера для первых тестов (это резко увеличивает процент брака, но для тестовых транзисторов приемлемо) + отработали новые технологические шаги техпроцесса, отличающиеся от 90нм.

Говорят, в Марте 2014 года на Микроне ждут приход нового сканера — и там 65нм получится без дополнительных хитростей, а с хитростями — и более тонкие техпроцессы (45нм, ниже?). Вот тогда, к концу года — и выйдут первые полноценные микросхемы по технологии 65нм. Объем производства ожидается порядка 500 200мм пластин в месяц — это практически гарантирует, что производство получится очень дорогим, и доступным только для государства.

Наконец о возможных хитростях

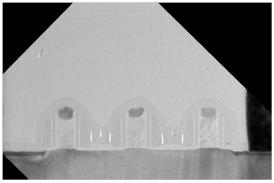

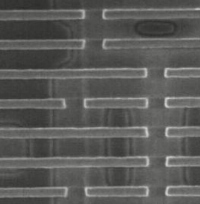

65нм можно было получить и на текущем оборудовании Микрона. Достаточно вспомнить про то, как Интел в 2007-м сделал 45нм техпроцесс на «сухой» фотолитографии используя сканер с апертурой 0.93 (у Микрона напомню 0.75): критические слои экспонировали в 2 захода: в первый заход экспонировали ряд горизонтальных линий (используя dipole illumination, поляризацию — так можно достичь большего разрешения, но только вдоль одной оси). Затем второй экспозицией нарезали линии на кусочки нужной формы. Результат на фотографии. Собственно, аналогичным образом получается разрешение 32нм и 22нм.

65нм можно было получить и на текущем оборудовании Микрона. Достаточно вспомнить про то, как Интел в 2007-м сделал 45нм техпроцесс на «сухой» фотолитографии используя сканер с апертурой 0.93 (у Микрона напомню 0.75): критические слои экспонировали в 2 захода: в первый заход экспонировали ряд горизонтальных линий (используя dipole illumination, поляризацию — так можно достичь большего разрешения, но только вдоль одной оси). Затем второй экспозицией нарезали линии на кусочки нужной формы. Результат на фотографии. Собственно, аналогичным образом получается разрешение 32нм и 22нм.

Этот подход позволяет получить k=0.21, и для Микроновского сканера это позволило бы получить 55нм техпроцесс. Но безусловно объем работ был бы весьма внушительным.

Резюме

- Говорить о «65нм микросхемах сделанных в России» пока преждевременно — это единичные тестовые транзисторы на существующем оборудовании.

- Технология LP (бОльшая длина затвора, более толстый подзатворный диэлектрик) — с низким потреблением и меньшей скоростью, ожидать процессоров аналогичных Intel 65nm (первые Core2Duo) не стоит.

- С новым оборудованием (в первую очередь сканер), которое должно заработать на Микроне в этом году — будут возможна как 65нм технология, так и более тонкие.

- Из-за очень маленького объема производства (500 пластин в месяц) себестоимость пластины обещает быть довольно высокой, завалить конкурентоспособной гражданской 65нм продукцией рынок не выйдет. Но этого и не требовалось.

Ссылки

Пресс-релиз Микрона

Новость CNews с некоторыми дополнениями

Обзор технологии Intel 65nm

Сравнительная таблица целой кучи технологий

Автор: BarsMonster