Каким образом повысить количество российских инженеров, которые были бы знакомы и с разработкой хардвера, и с разработкой софтвера, и могли бы строить системы, в которых часть функциональности находится в специализированном железе, а часть — в программном обеспечении, с соблюдением баланса между ними?

Для этого вовсе не обязательно выбрасывать несуразные деньги а-ля сделка Сколкова и MIT.

Есть масса дешевых и эффективных мер по апгрейду российской образовательной системы. Одна из них — широко ввести практические классы ПЛИС / ППВМ / FPGA среди старших школьников и студентов. Это то, на чем учатся и инженеры, которые потом разрабатывают микросхемы внутри Apple iPhone в Купертино, Калифорния.

ПЛИС — Программируемая логическая интегральная схема

ППВМ — Программируемая пользователем вентильная матрица

FPGA — Field Programmable Gate Array

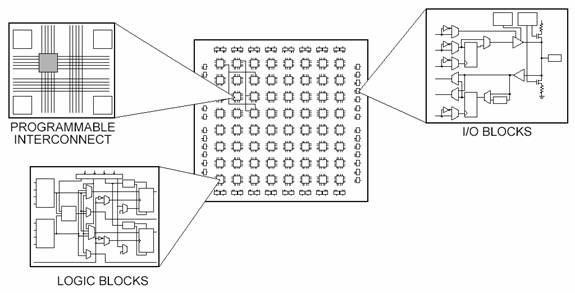

Так как ниже речь идет о платах, то у многих читателей тут же может возникнуть реакиция «а, это ардуино/raspberry pi/роботы — знаем!» Нет, это не ардуино, не имеет вообще никакого отношения к данному классу устройств. Еще раз повторяю: это не ардуино, потому что у ардуин стоит внутри основанный на микропроцессорном ядре микроконтроллер, а тут вообще никакого процессора нет — чистая матрица перепрограммируемых логических ячеек.

Так как ниже речь идет о платах, то у многих читателей тут же может возникнуть реакиция «а, это ардуино/raspberry pi/роботы — знаем!» Нет, это не ардуино, не имеет вообще никакого отношения к данному классу устройств. Еще раз повторяю: это не ардуино, потому что у ардуин стоит внутри основанный на микропроцессорном ядре микроконтроллер, а тут вообще никакого процессора нет — чистая матрица перепрограммируемых логических ячеек.

Пока американские школьники будут играться только с микроконтроллерами, российские школьники могут играться одновременно и с микроконтроллерами, и с FPGA, и тем самым получат технологическое преимущество за счет системного — понимания и программирования, и принципов разработки хардверной логики одновременно.

Одной из проблем использования FPGA для образования российских тинейджеров является нехватка литературы на русском языке. Довольно скоро должен выйти русский перевод книжки Digital Design and Computer Architecture, Second Edition, by David Harris and Sarah Harris, и эта проблема будет частично решена. Но помимо литературы, описывающей схемотехнику и разработку хардвера на уровне регистровых обменов (Register Transfer Level — RTL) используя языки описания аппаратуры (Hardware Description Languages — HDL), есть и другая проблема — для новичка работа со студенческими платами нетривиальна, а программная среда для разработки — недружелюбна.

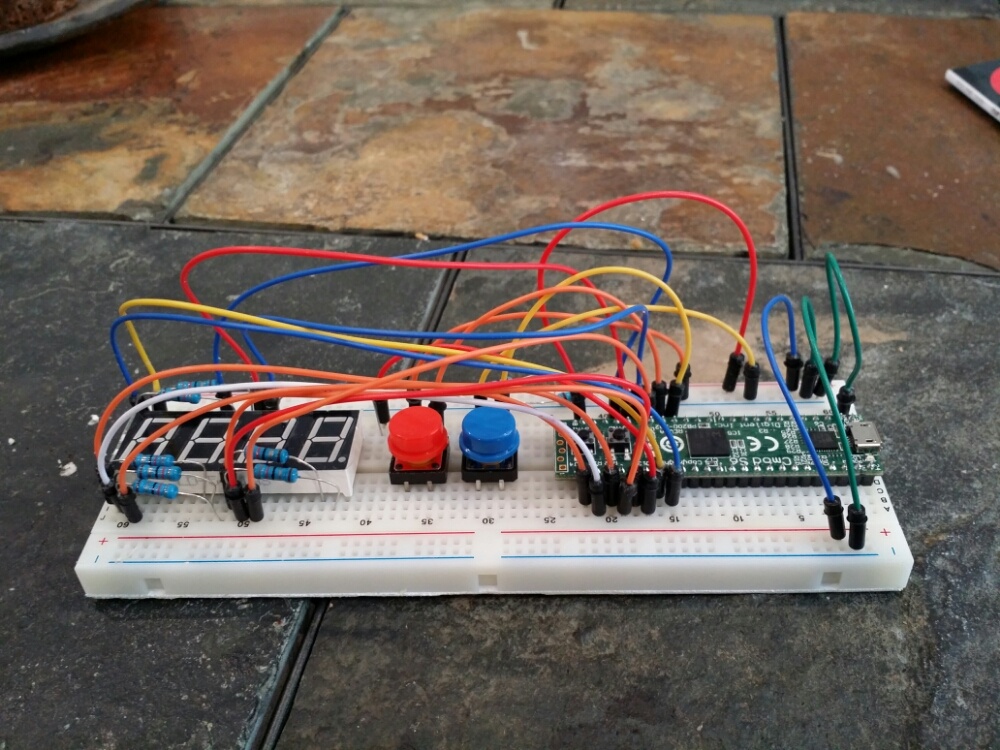

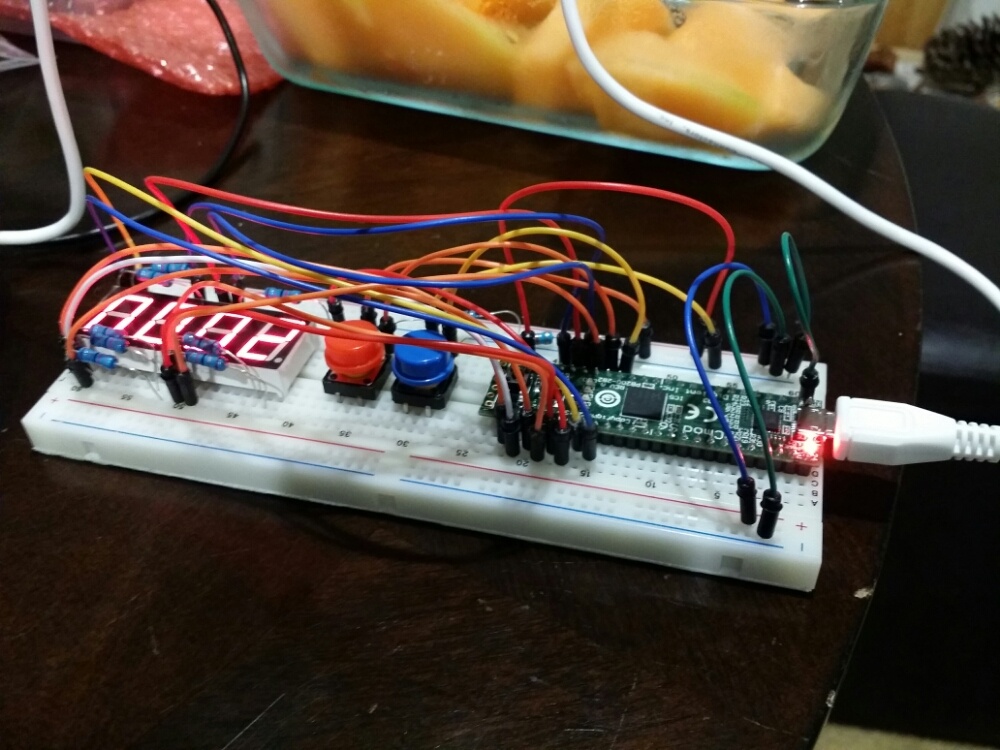

Поэтому я решил показать по шагам, как начать работать с одной из FPGA плат, которая удобна тем, что втыкается в макетную плату и может быть использована преподавателями кружков школьников наподобие тех, которые еще с 1970-х годов начинали введение в схемотехнику через микросхемы малой степени интеграции типа К155ЛА3 (TTL 7400, CMOS 4000). Втыкаемая в макетку FPGA плата является естественным продолжением таких курсов.

Вот так учили основам цифровой логики с начала 1970-х годов:

И вот к чему он может переходить после ознакомления школьников с базовыми понятиями логического элемента, триггера и сигнала тактовой частоты. Это то же самое, но на технологии 2010-х:

Дело в том, что внутри FPGA по сути находится конструктор из тысяч логических элементов наподобие элементов в K155ЛА3, но в FPGA их можно соединять не руками с помощью проводов, а меняя содержимое специальной памяти, биты которое соединены с мультиплексорами, которые меняют логические функции ячеек FPGA и соединения между ними:

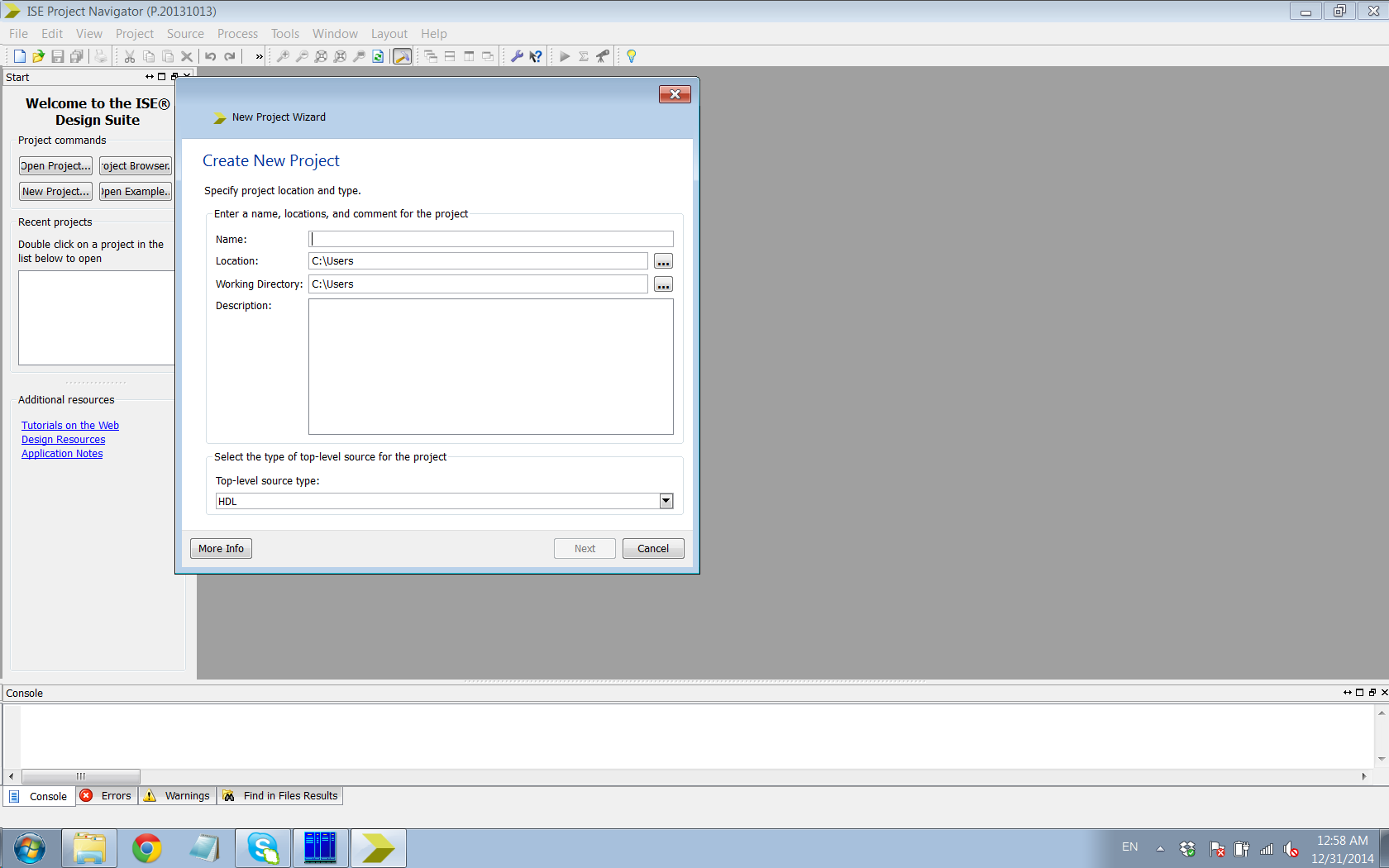

Где достать платы, софтвер для разработки и необходимые плагины, я расскажу в конце, а сейчас погрузимся непосредственно в создание простой схемы с помощью бесплатной среды разработки Xilinx ISE WebPACK:

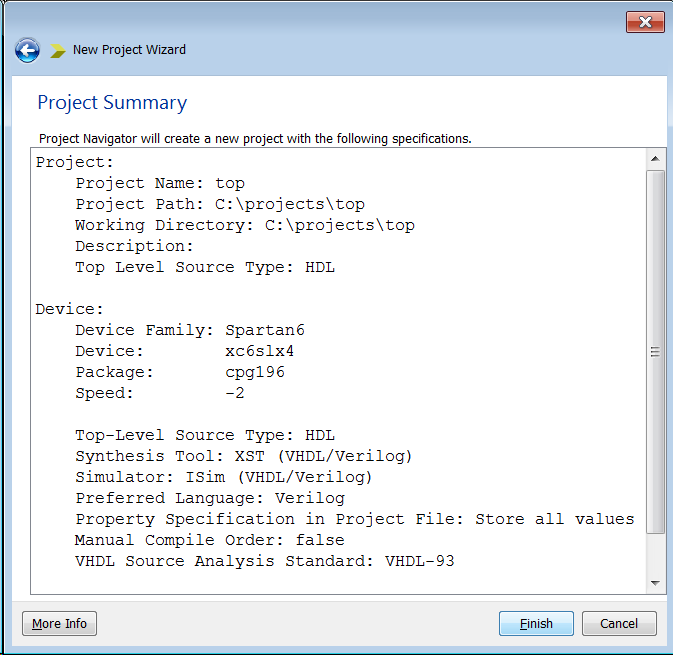

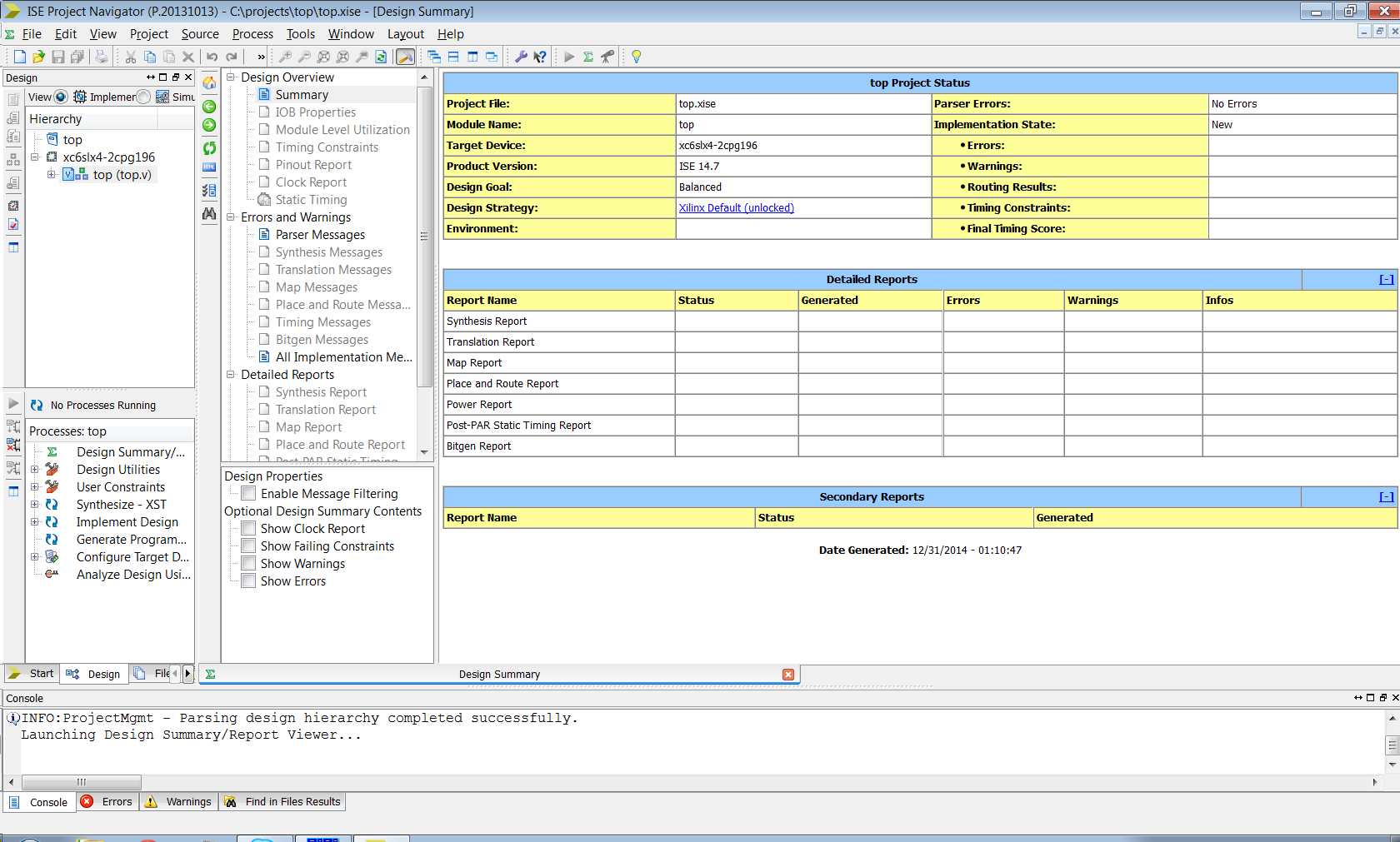

Входим и создаем новый проект:

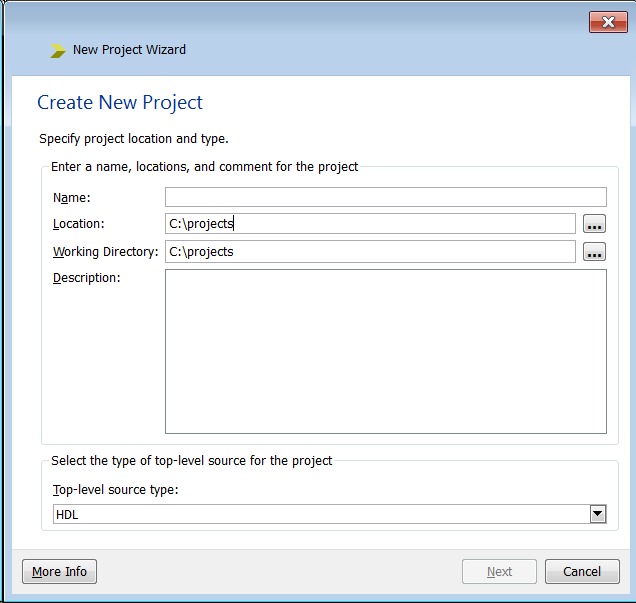

Важно выбрать отдельную директорию для проекта и не смешивать его с вашими исходными файлами, ибо синтезатор генерирует много всяких временных файлов и вы в них можете запутаться (все их можно удалить после использования):

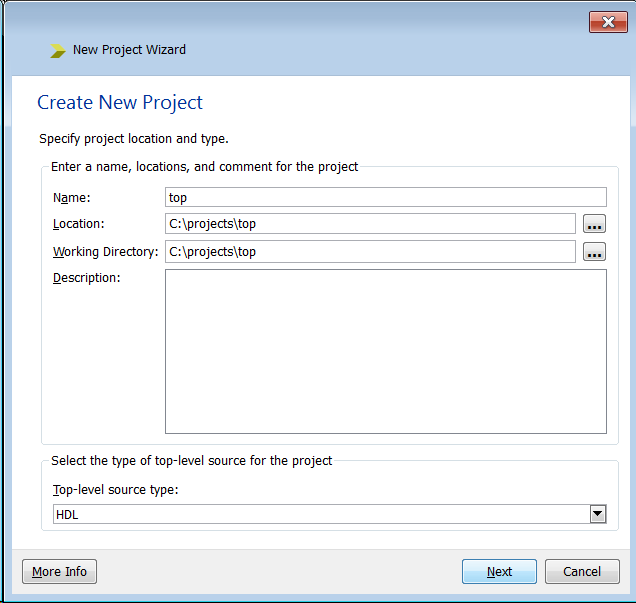

Вводим имя проекта. Это имя совпадает с именем главного модуля на Verilog-е (языке описания железа):

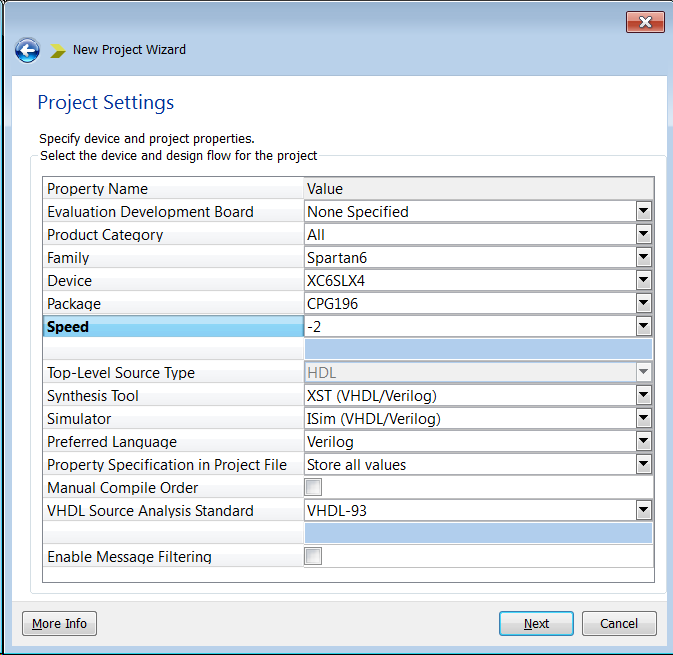

Вводим параметры FPGA: Family, Device, Package, Speed. Их нужно взять из документации по плате.

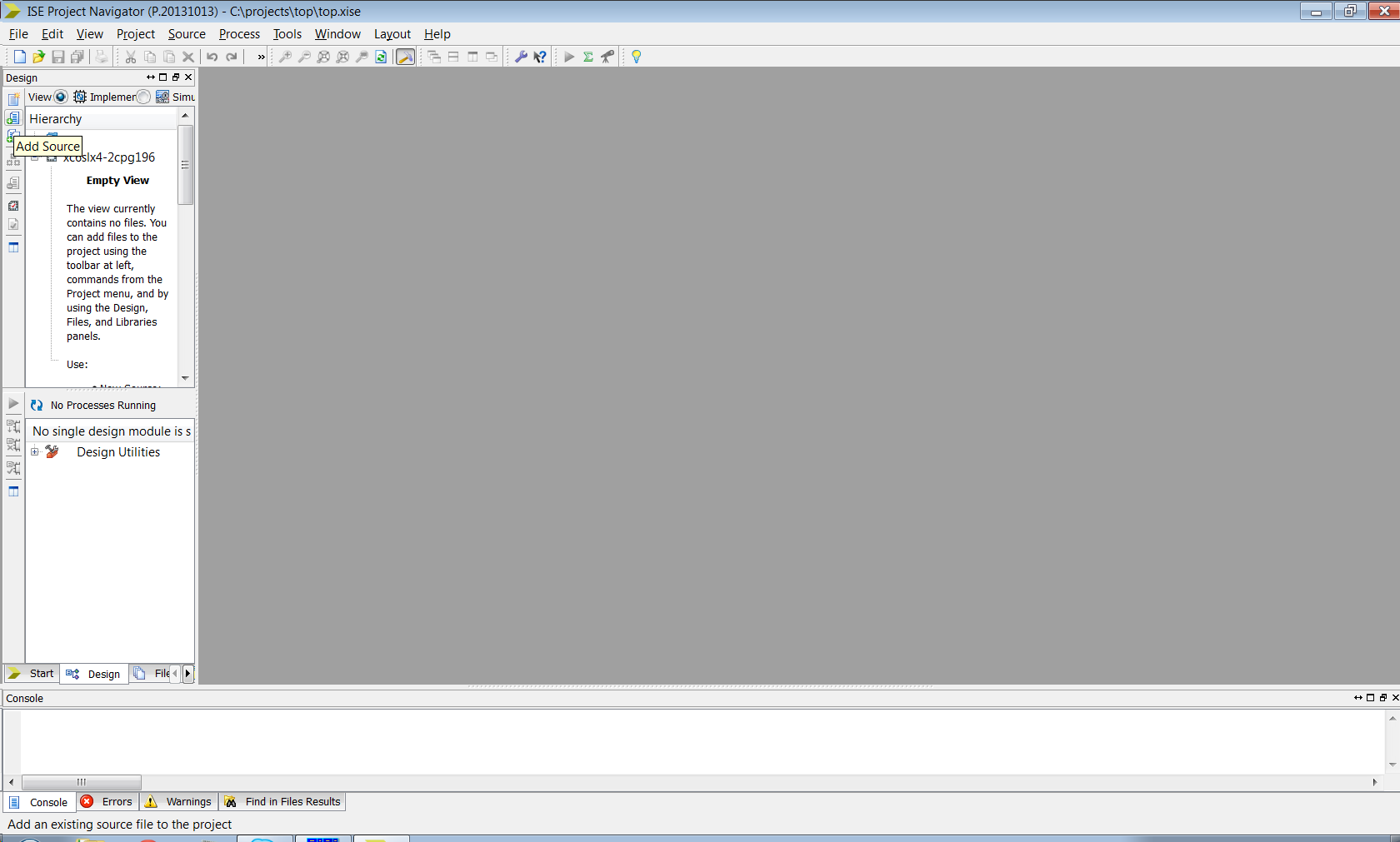

Проект создан:

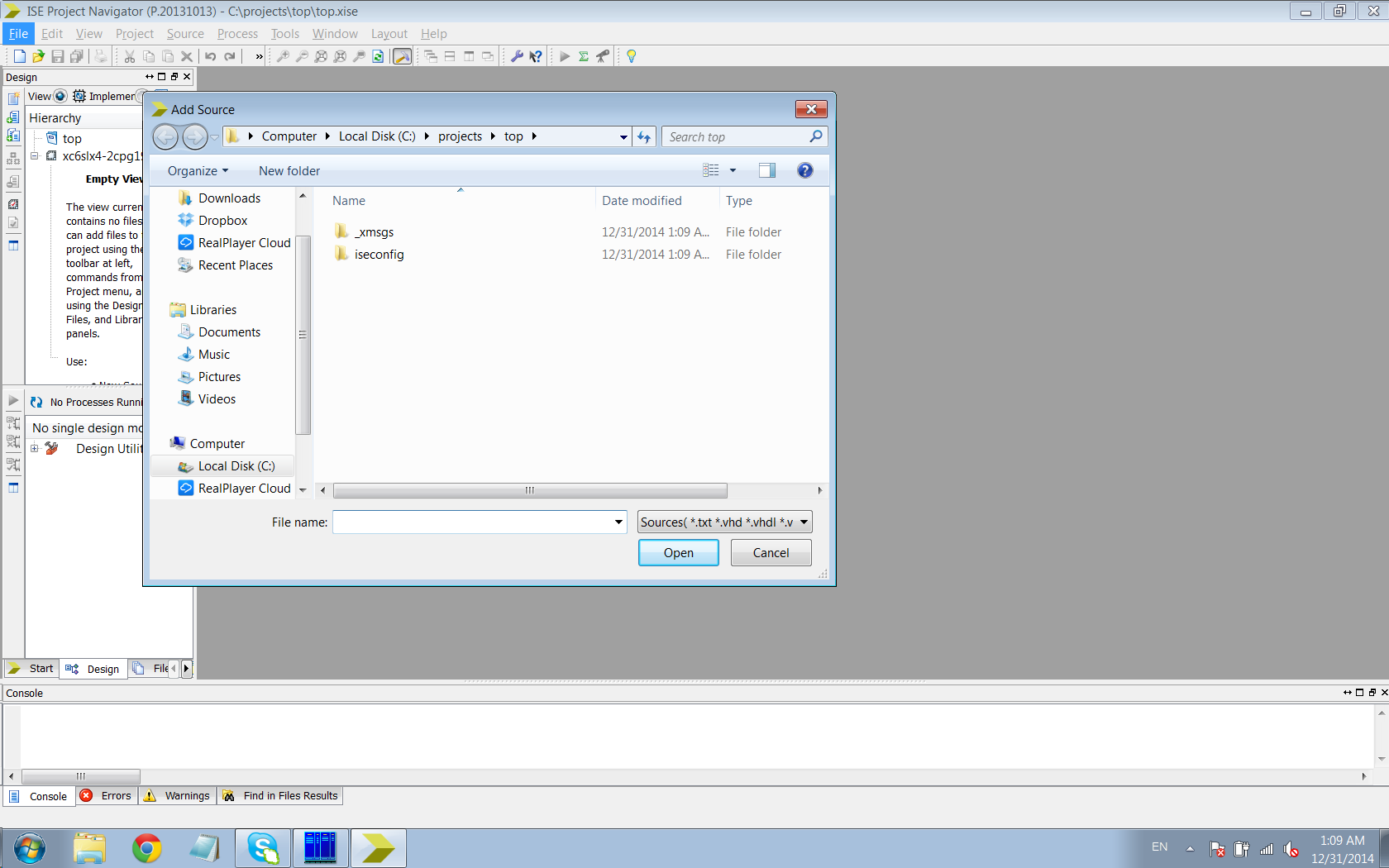

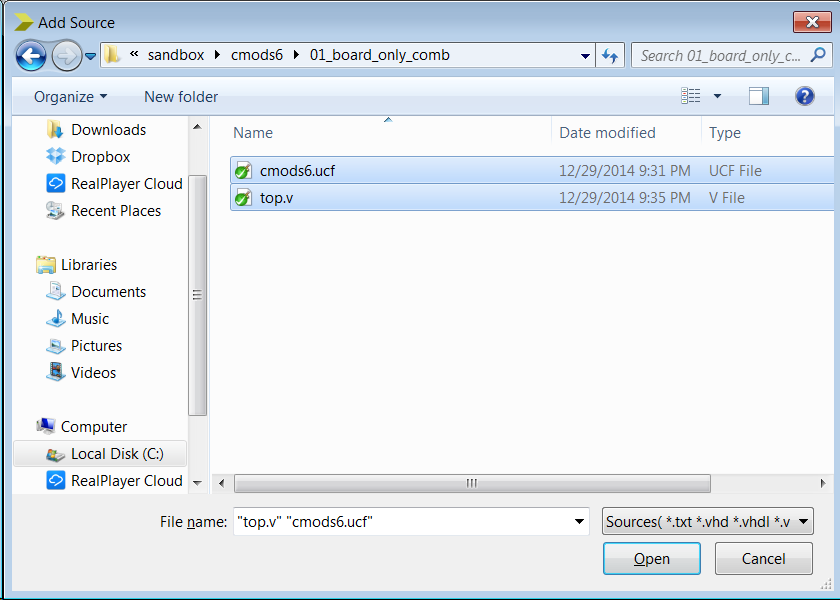

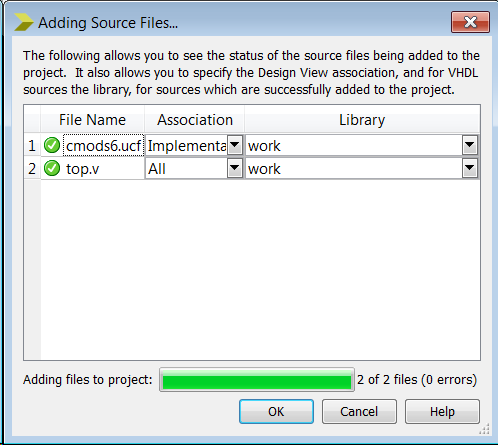

Добавляем исходные файлы на языке описания аппаратуры Verilog.

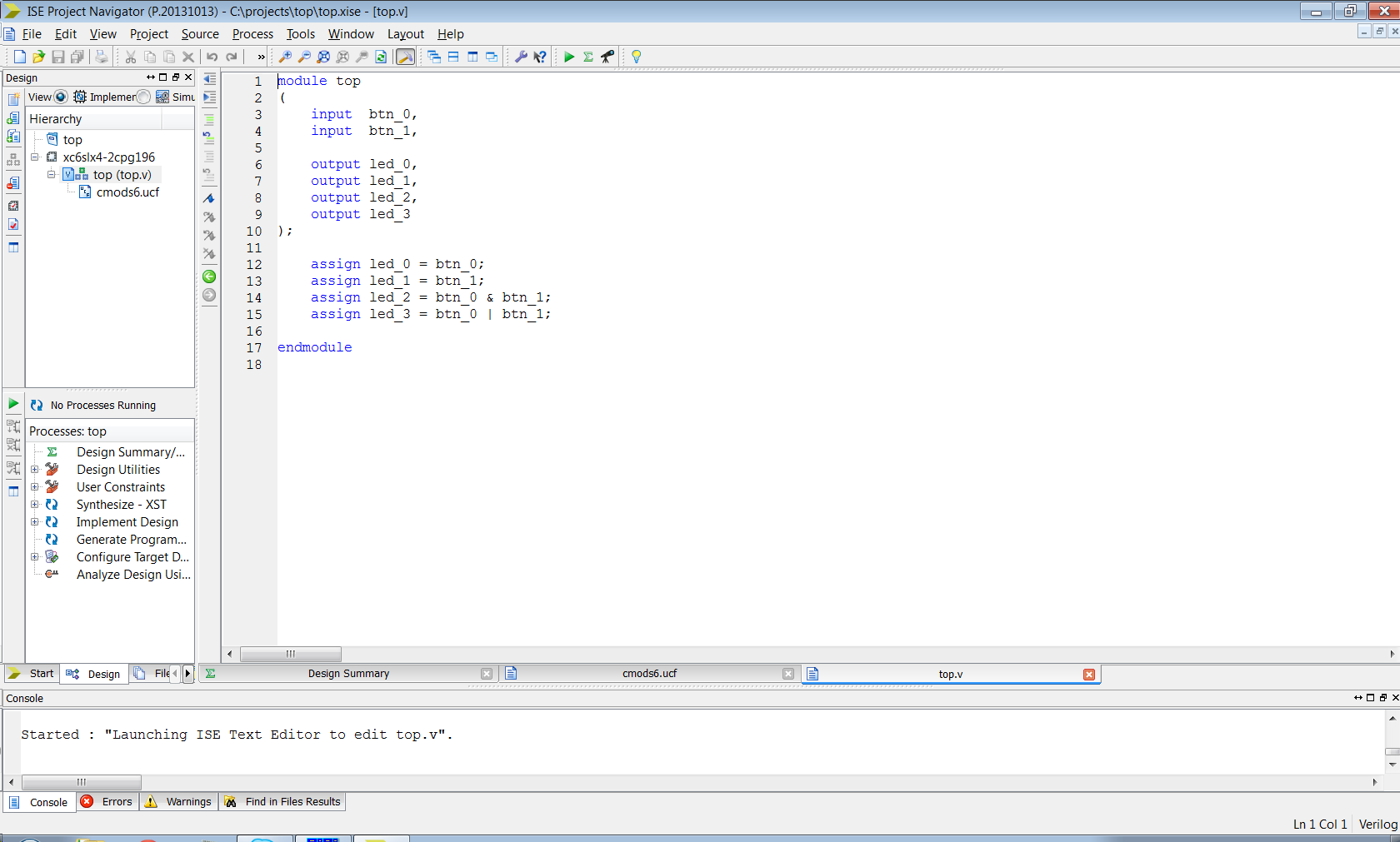

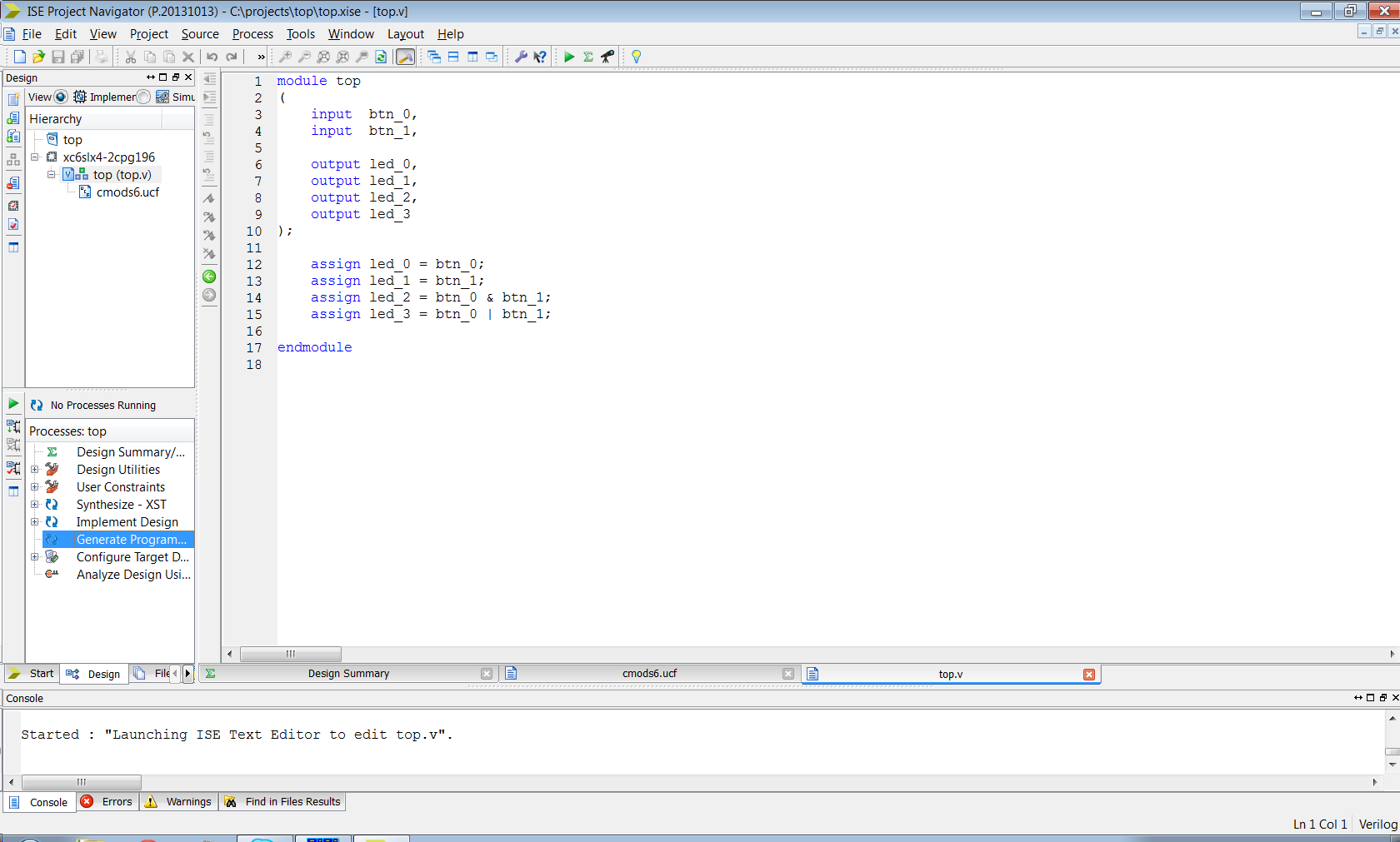

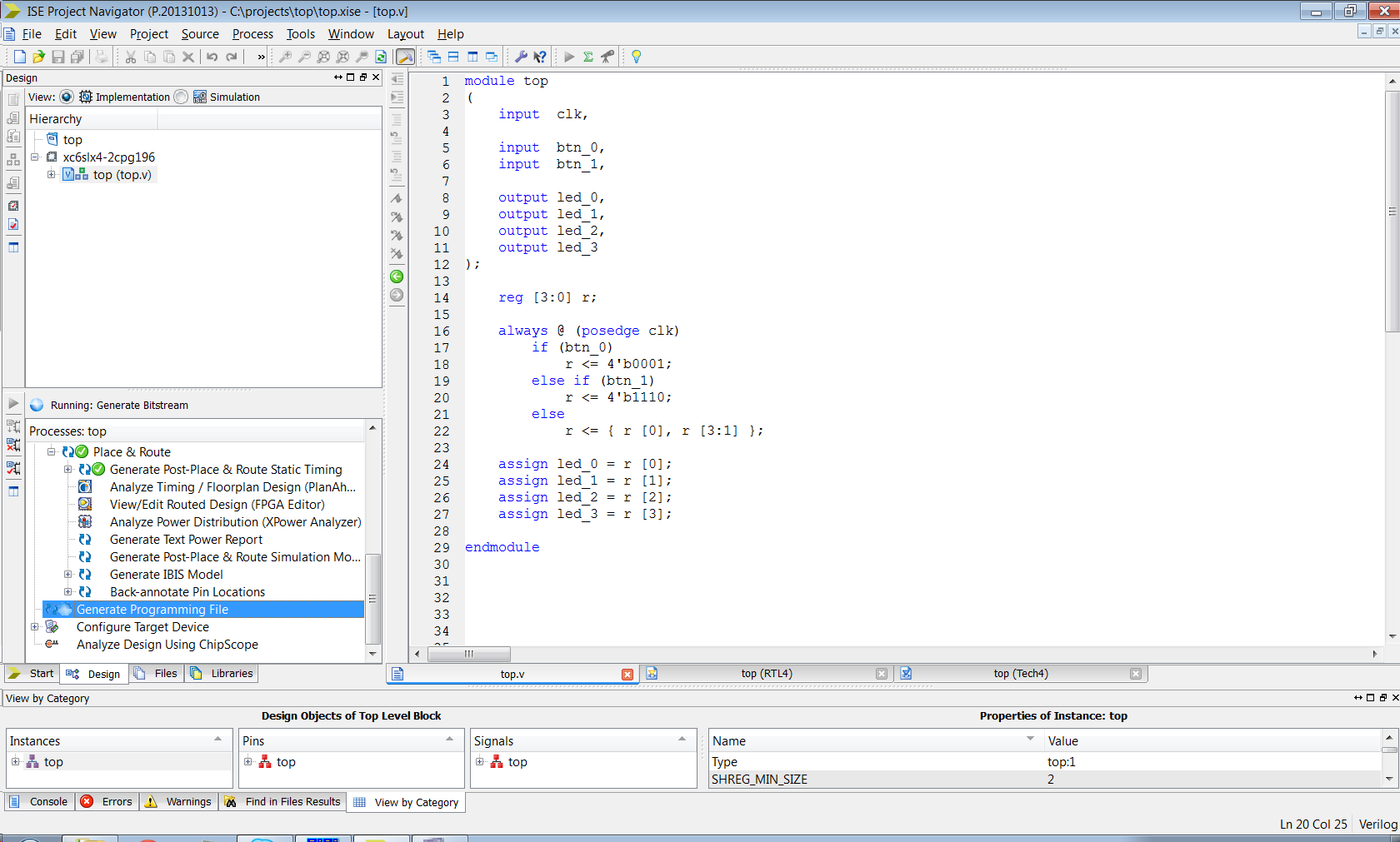

Файл top.v содержит описание схемы:

module top

(

input btn_0,

input btn_1,

output led_0,

output led_1,

output led_2,

output led_3

);

assign led_0 = btn_0;

assign led_1 = btn_1;

assign led_2 = btn_0 & btn_1;

assign led_3 = btn_0 | btn_1;

endmodule

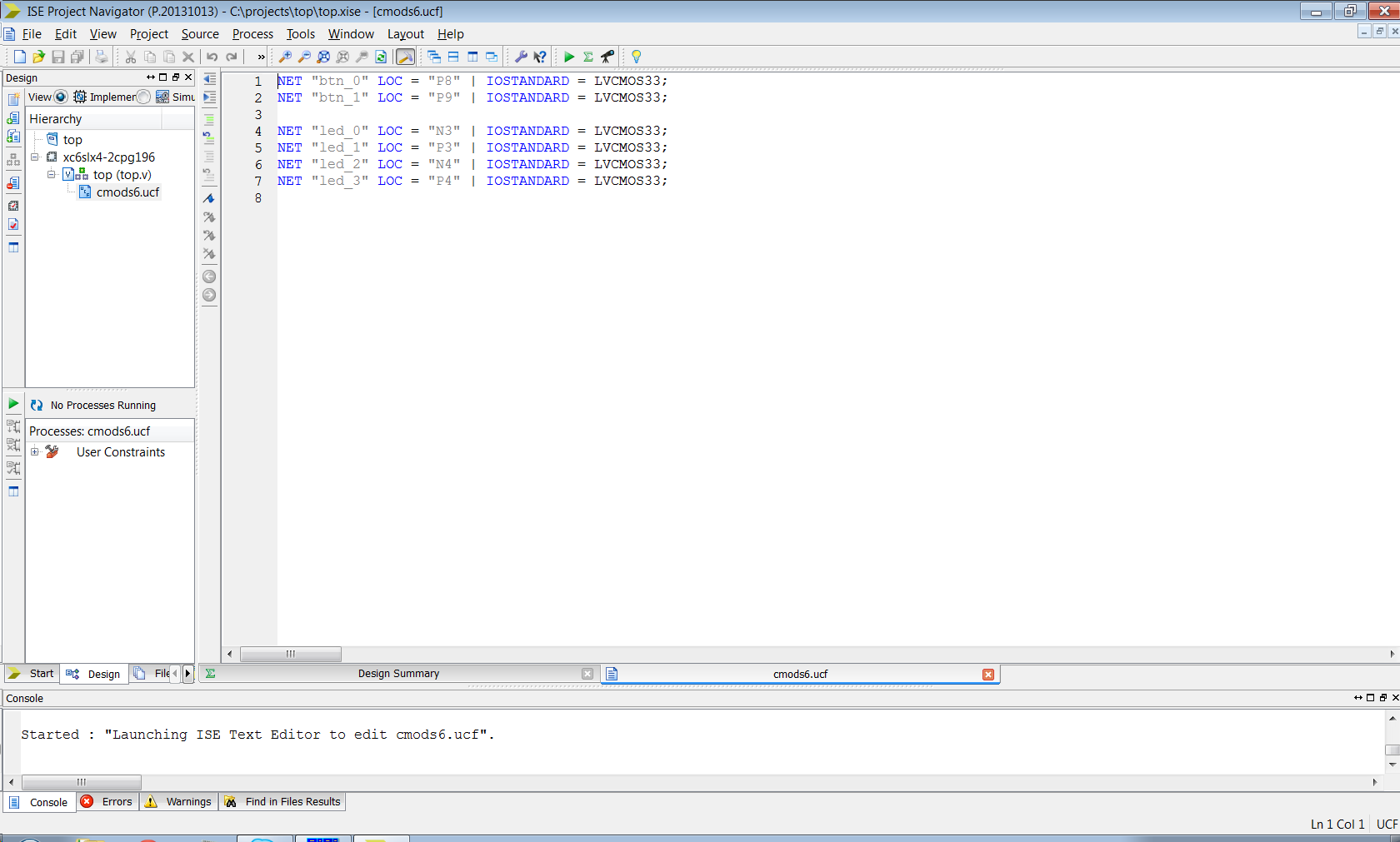

Файл cmods6.ucf содержит информацию для среды разработки о том, как связаны логические вводы и выводы главного модуля (btn_0, led_2, ...) с местонахождением (location, LOC) физических ножек микросхемы FPGA, которые именуются P8, N4 и т.д. Этот файл — урезанная версия файла для данной платы, загруженная с сайта компании Digilent (производитель плат):

NET "btn_0" LOC = "P8" | IOSTANDARD = LVCMOS33; NET "btn_1" LOC = "P9" | IOSTANDARD = LVCMOS33; NET "led_0" LOC = "N3" | IOSTANDARD = LVCMOS33; NET "led_1" LOC = "P3" | IOSTANDARD = LVCMOS33; NET "led_2" LOC = "N4" | IOSTANDARD = LVCMOS33; NET "led_3" LOC = "P4" | IOSTANDARD = LVCMOS33;

Теперь нажмем на кнопку «сгенерировать файл для программирования ПЛИС». Тут есть важный момент — «программирование» — это не софтверное софтверным программированием, которое сводится к созданию последовательности команд некоего процессора. Programming File в данном случае — это содержимое памяти в ПЛИС, которое определяет логические функции и соединения ячеек ПЛИС. Процессор в данной схеме не присутствует (хотя вы можете сами создать процессор, программируя (в вышеприведенном смысле) ячейки ПЛИС).

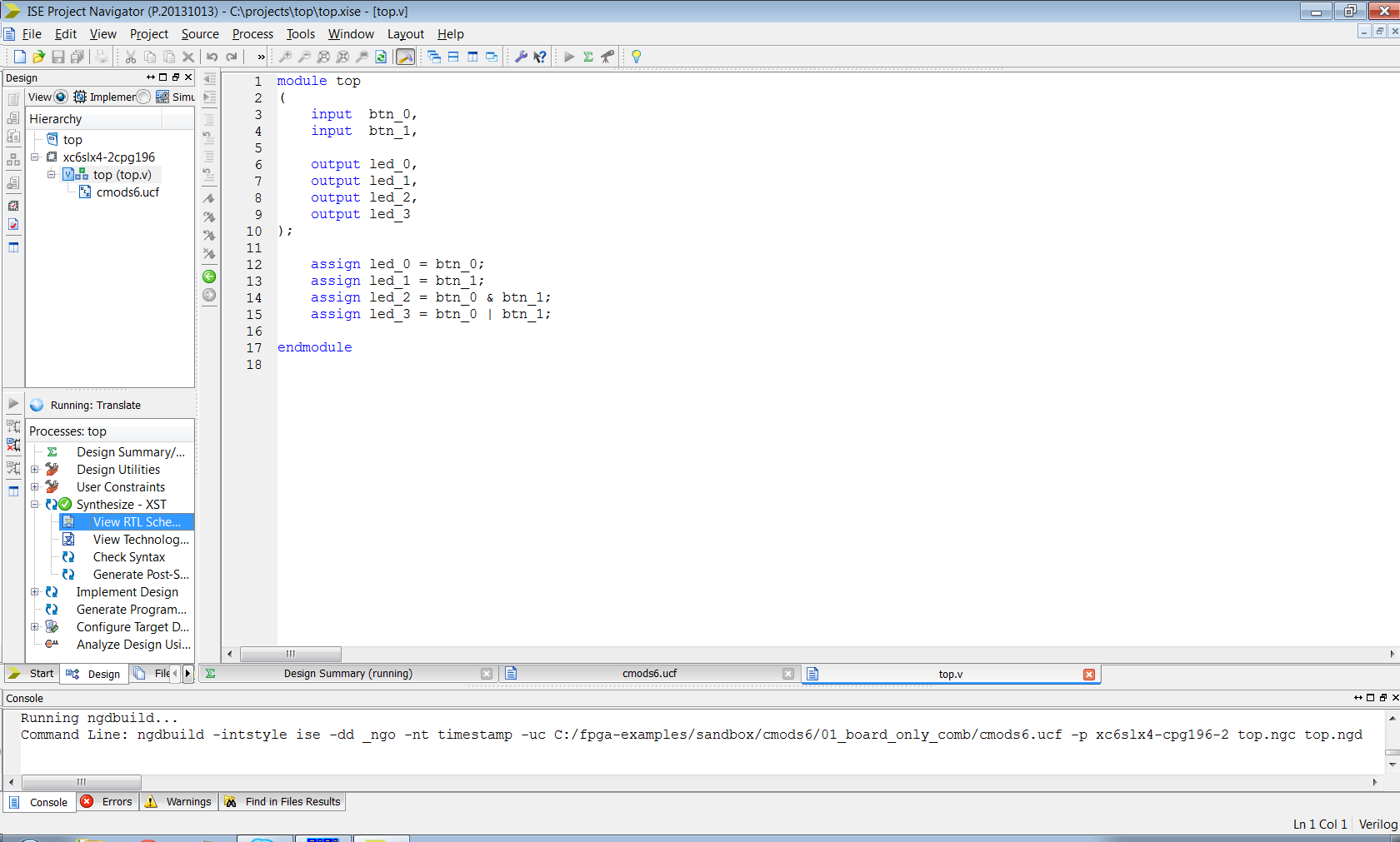

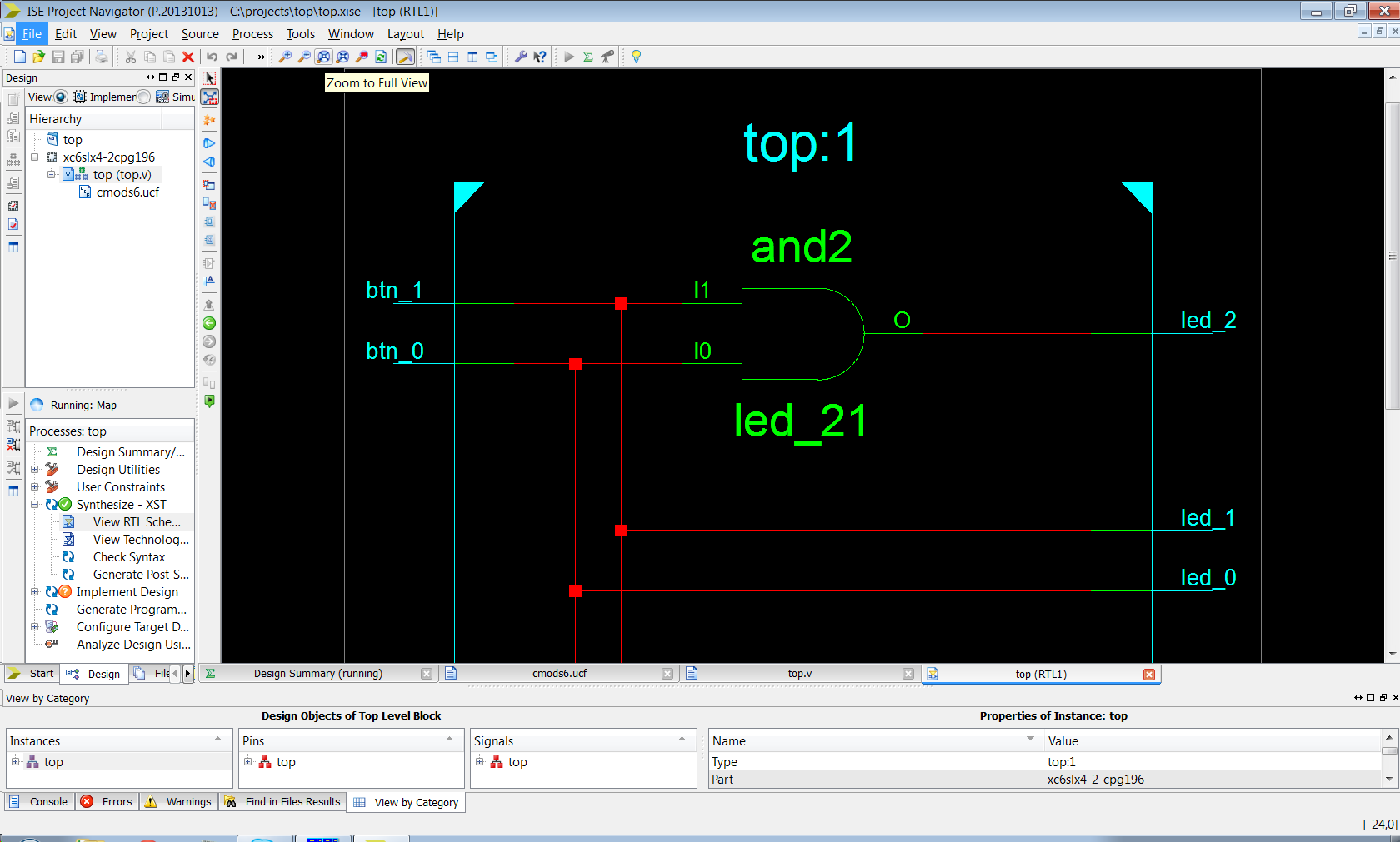

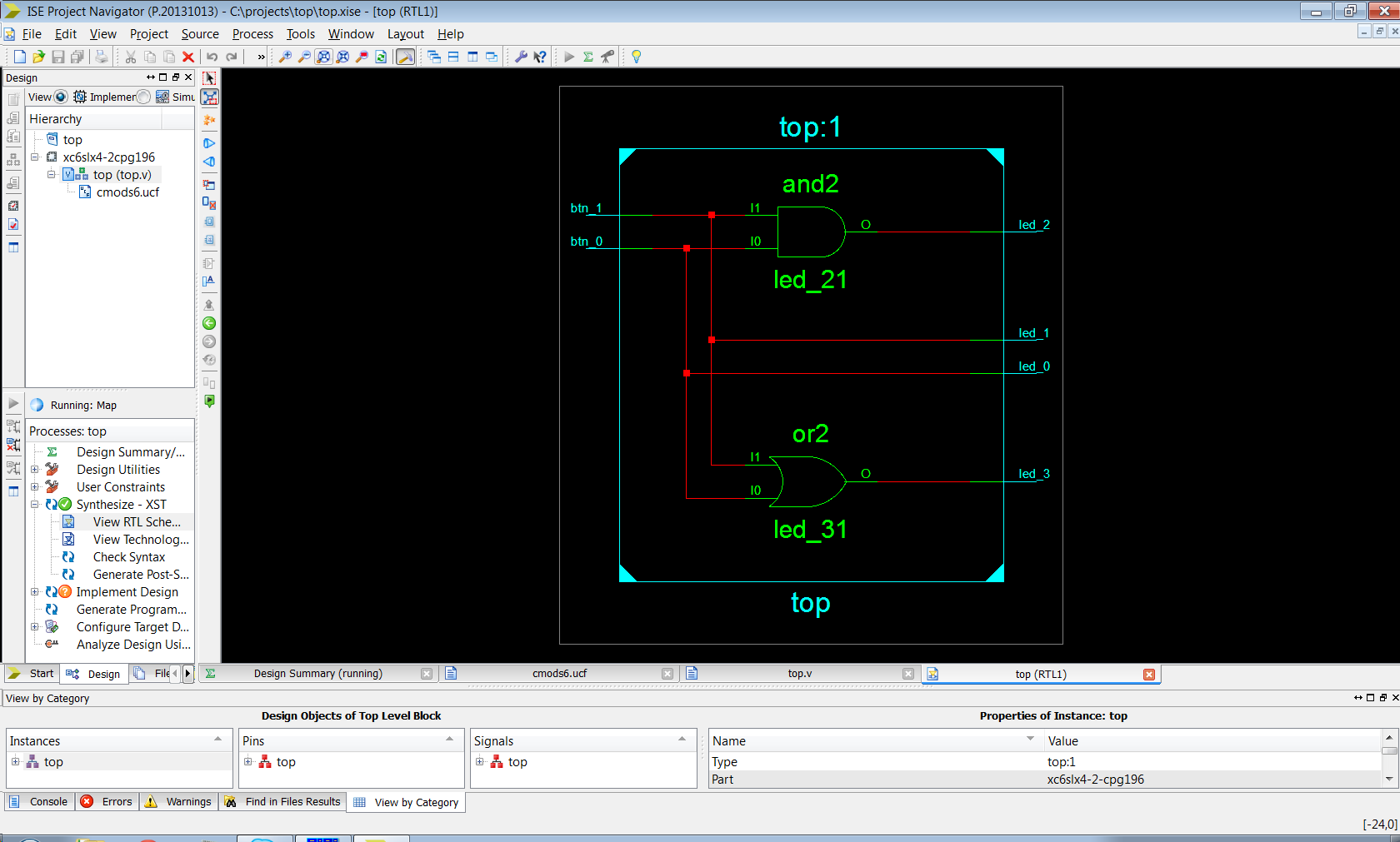

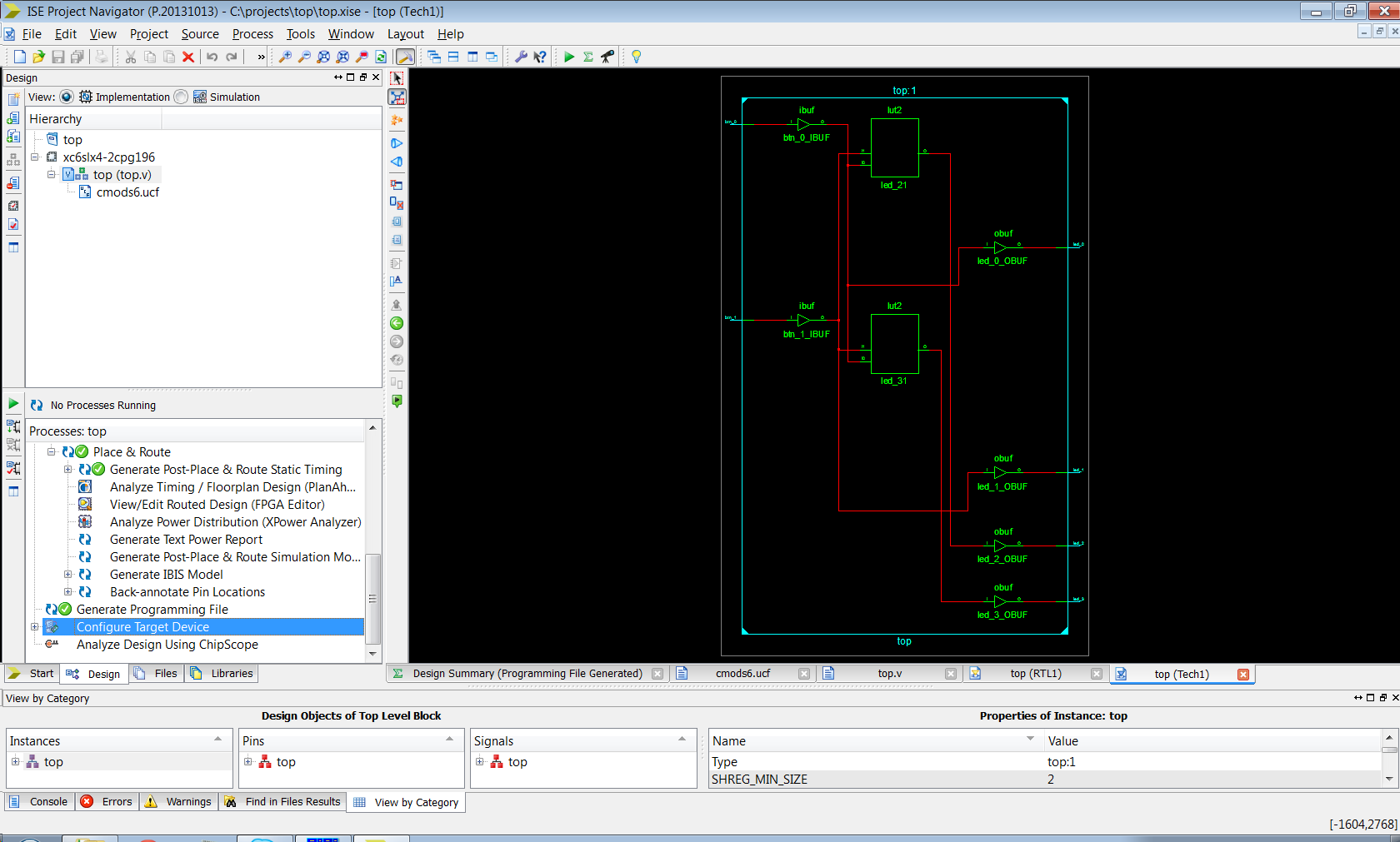

Теперь нажмем кнопку «посмотреть на абстрактную (не привязанную к конкретному FPGA) схему, описанную на верилоге и синтезированную софтвером):

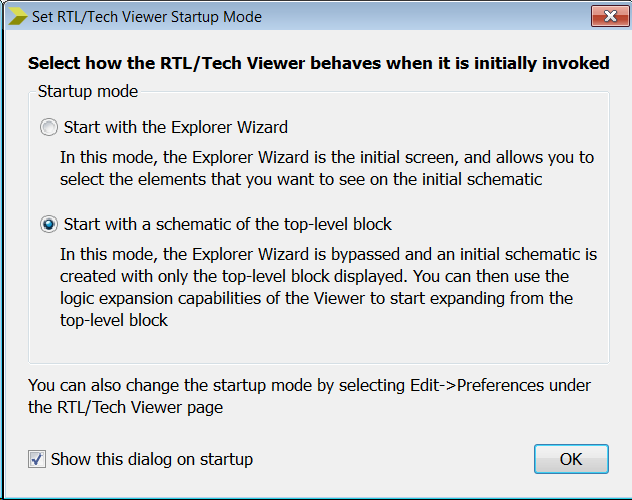

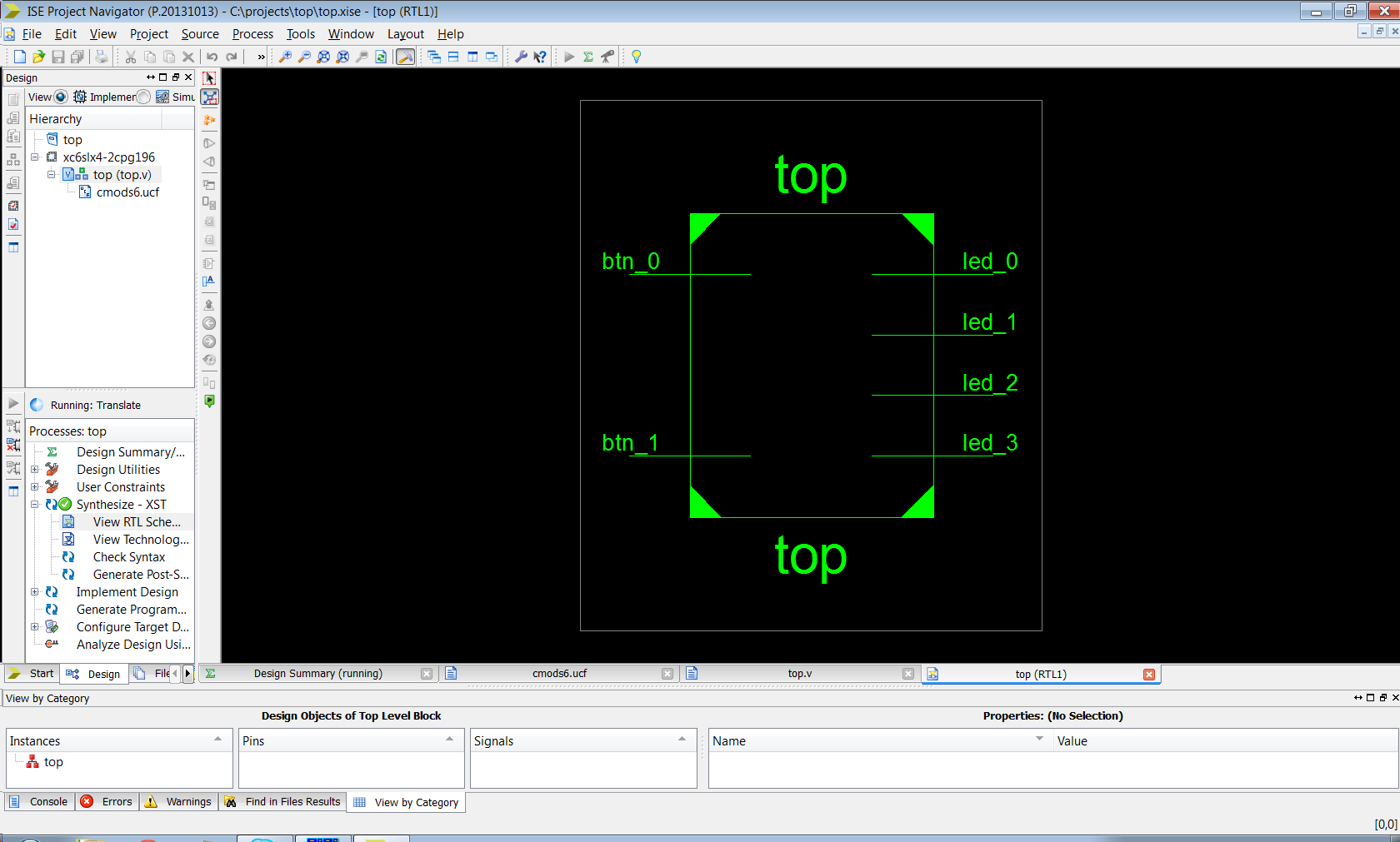

Верхний модуль:

Нажмем на мышкой чтобы посмотреть внутрь:

Нажмем на кнопку „Zoom to Full View“ чтобы увидеть всю схему:

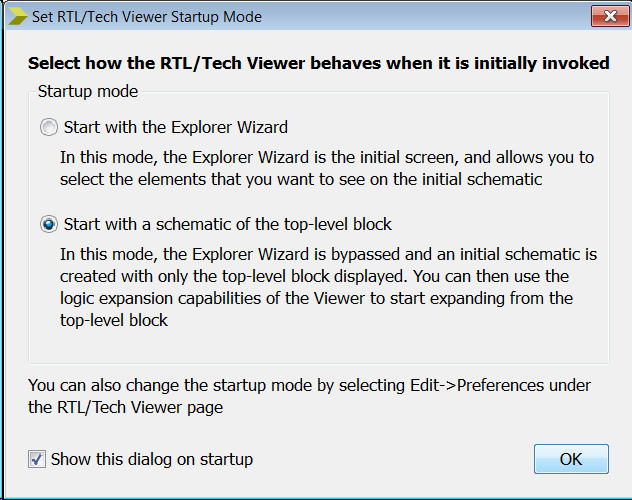

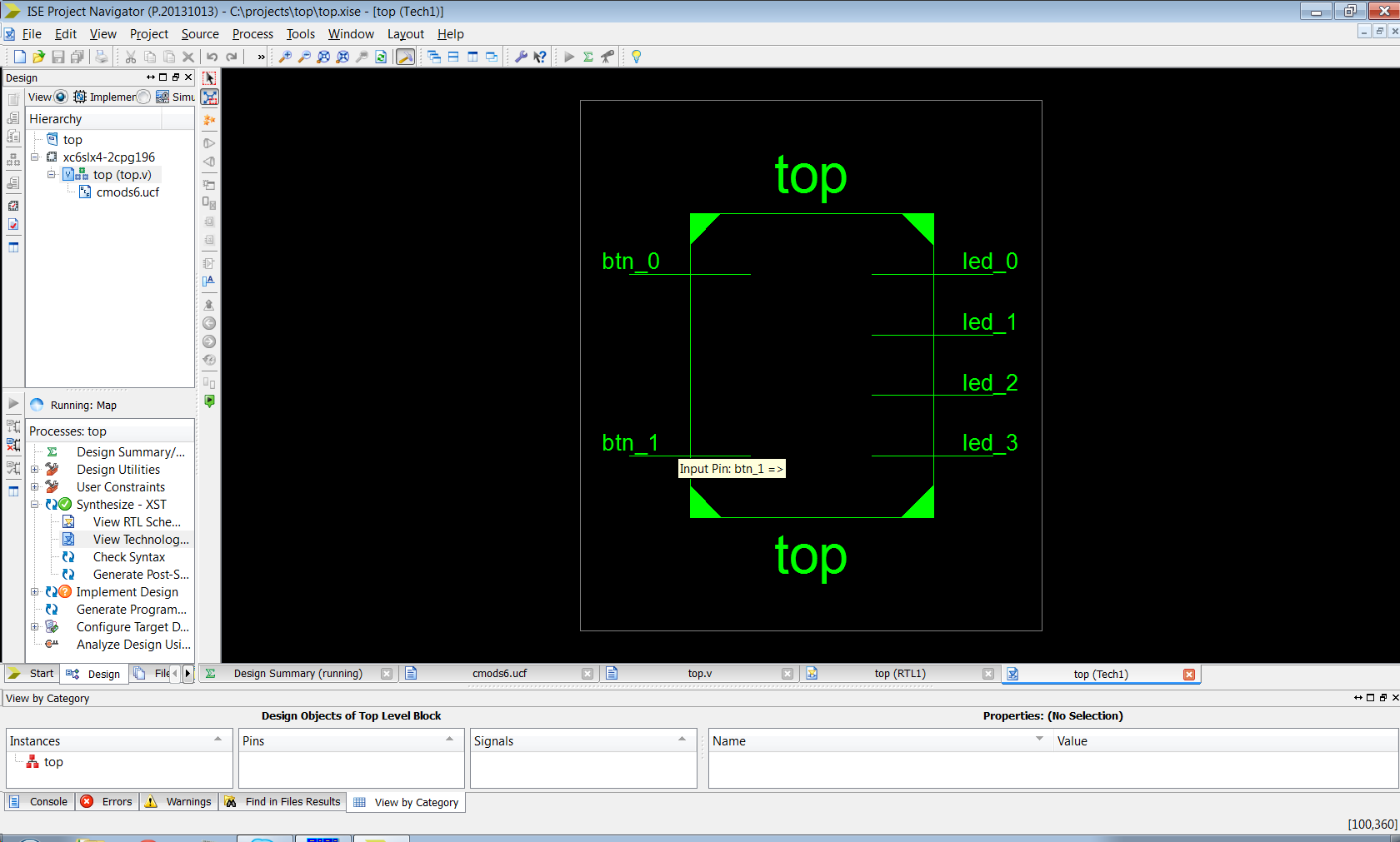

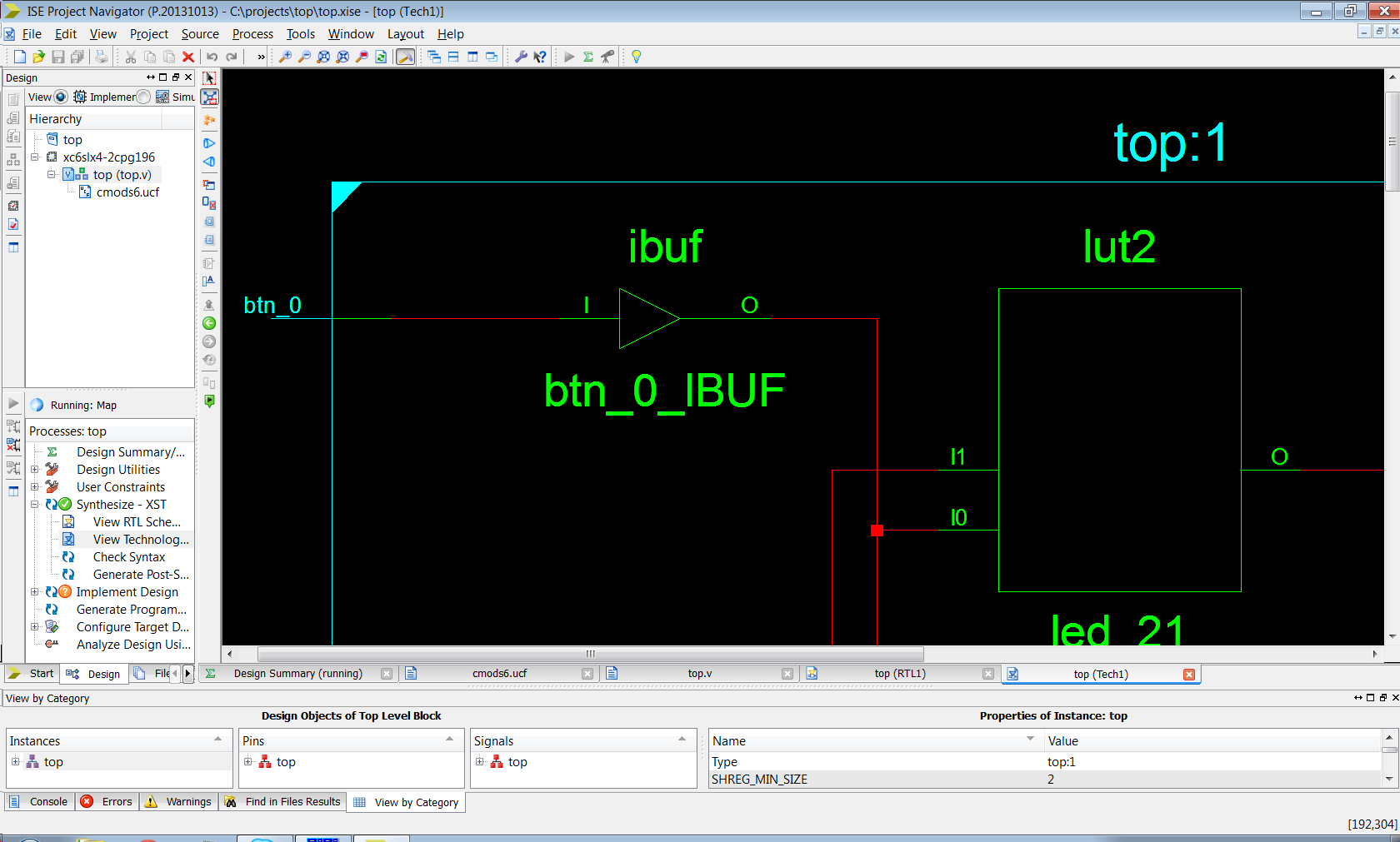

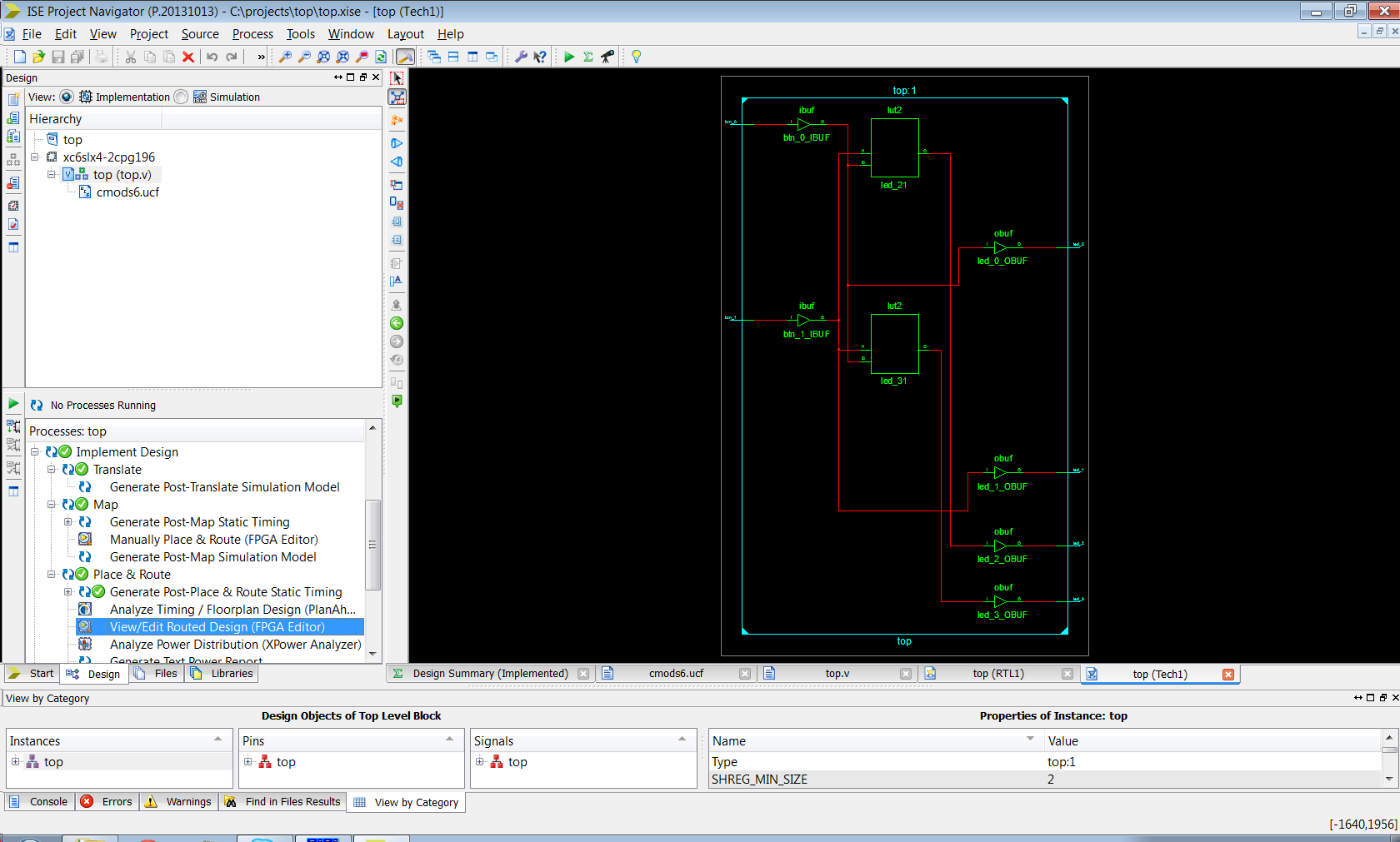

А теперь посмотрим на переработанную схему, сгенерированную софтвером для конкретного FPGA (View Technology-Specific):

Мы видим слово LUT — это Look-Up Table — его нужно запомнить на будущее:

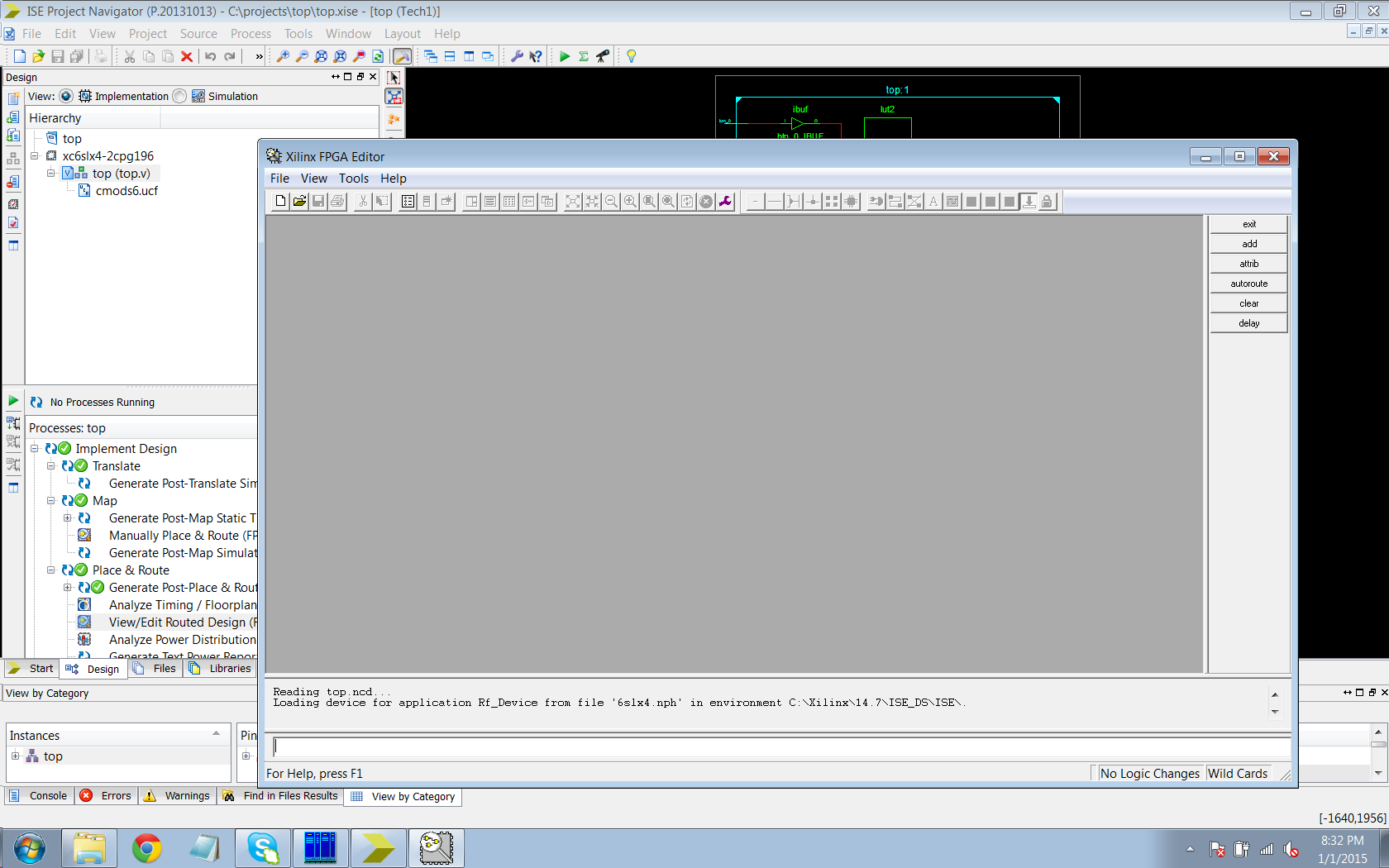

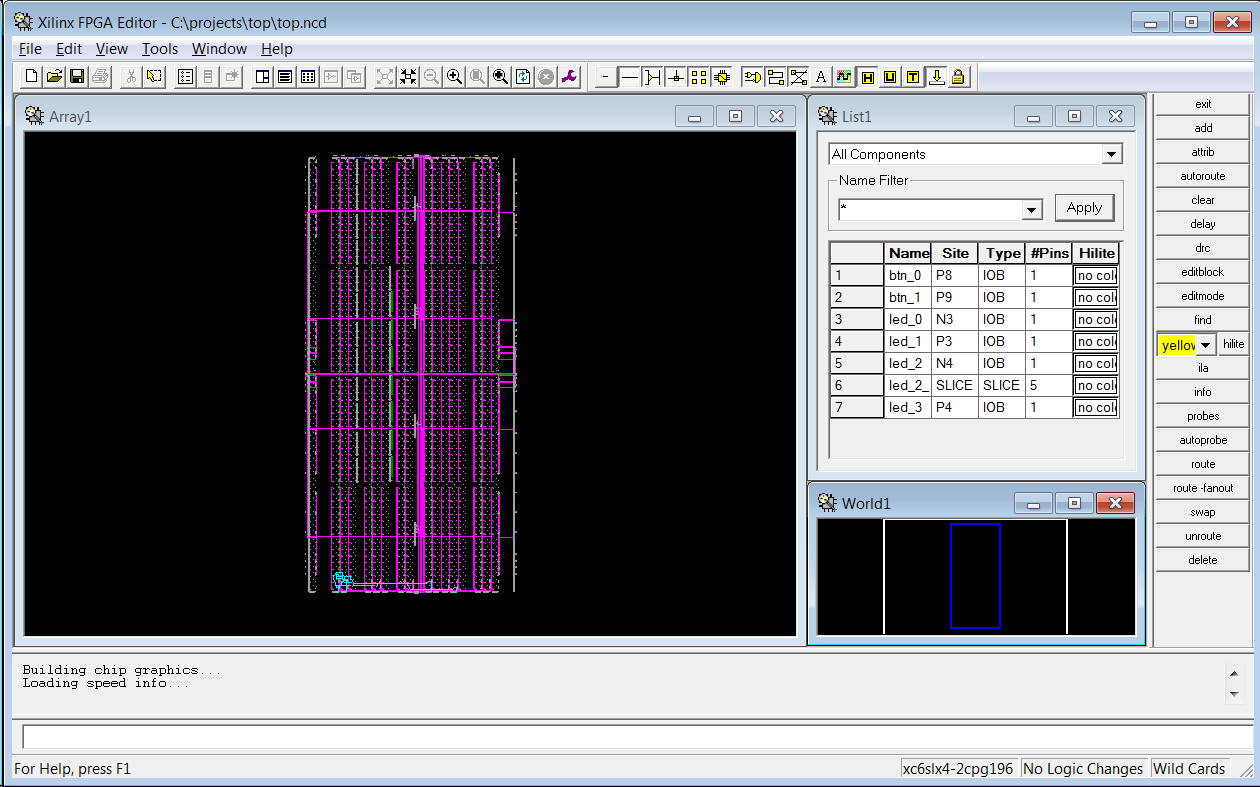

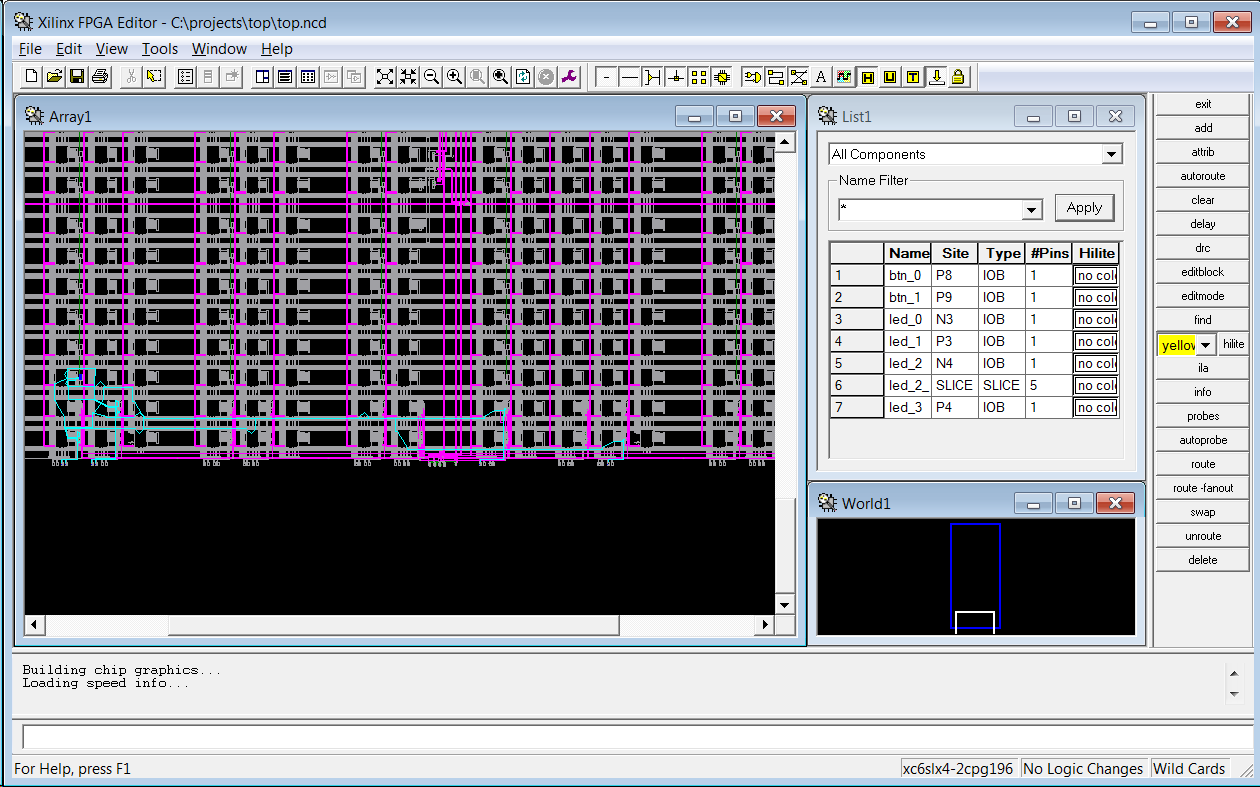

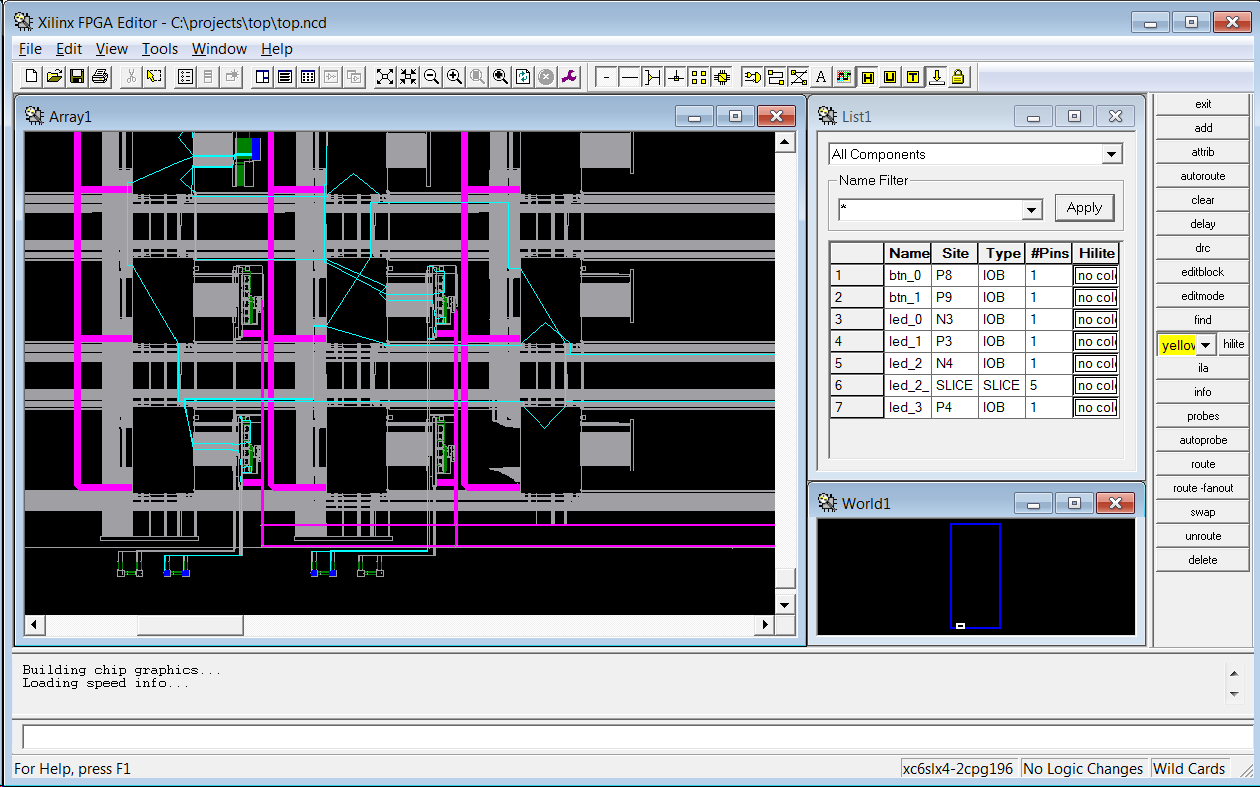

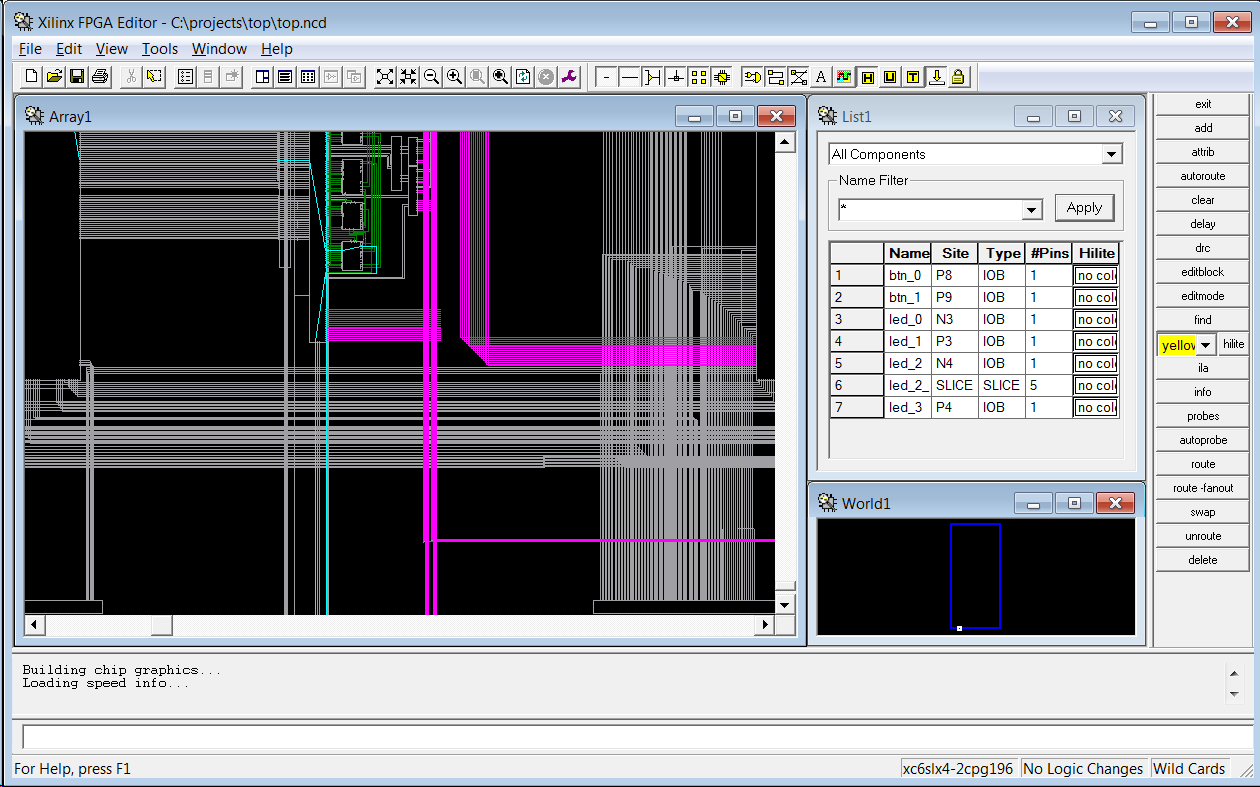

Теперь нажмем на кнопку „View/Edit Routed Design (FPGA Editor)“, чтобы посмотреть, как схема ляжет на ячейки FPGA:

Укрупним:

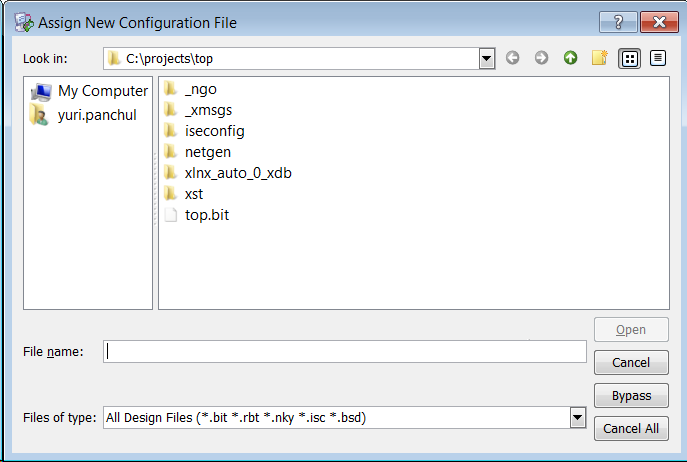

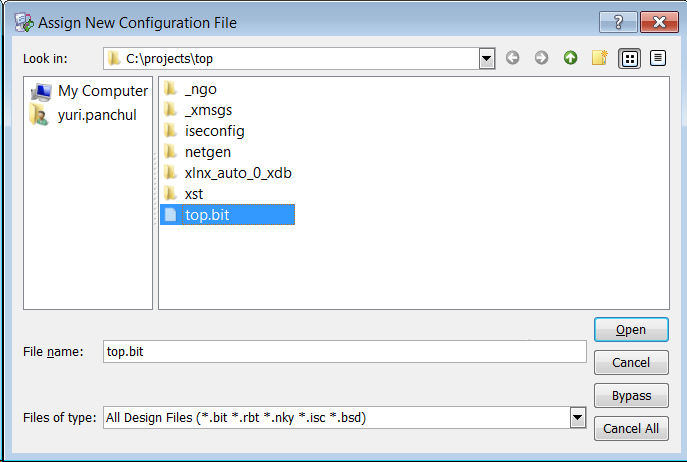

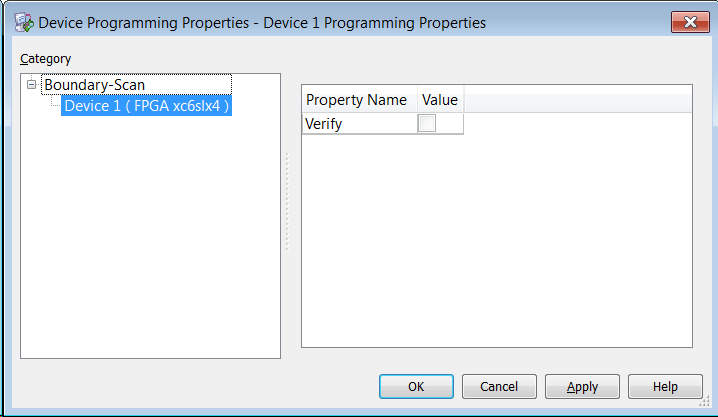

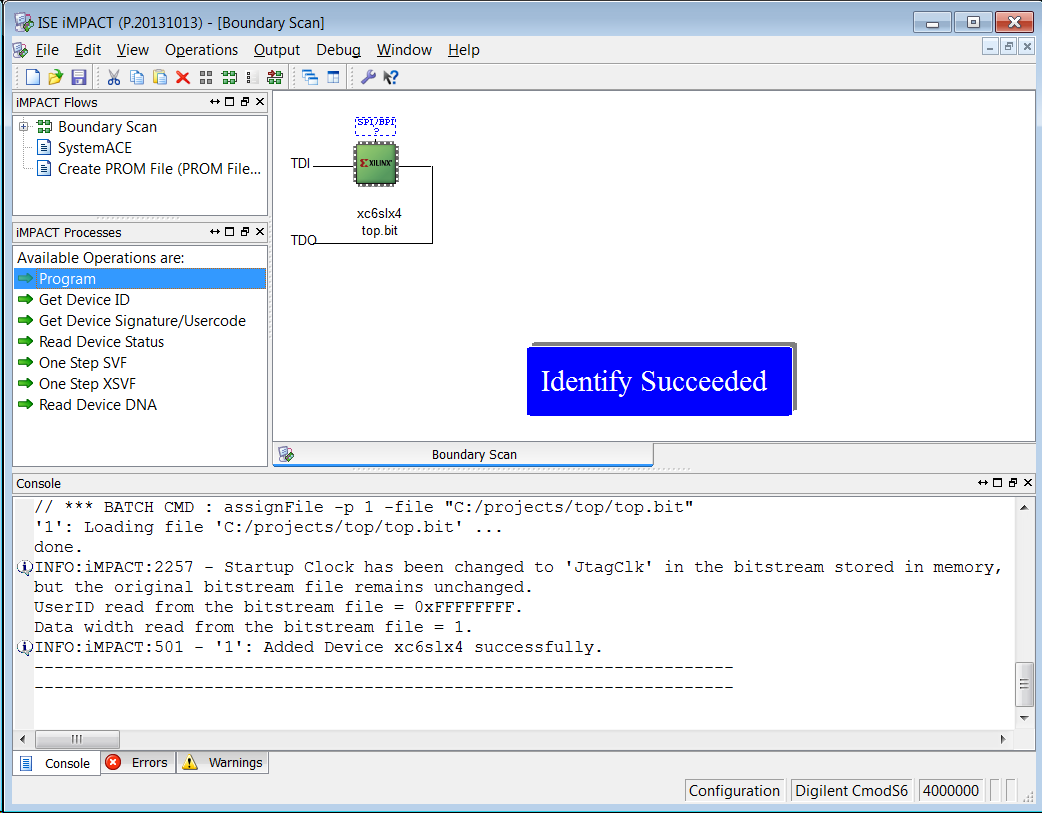

Жмем кнопку чтобы сконфигурировать FPGA. Плата прицеплена микро-USB кабелем к компьютеру.

С этого момента важно, что установлен плагин от Digilent-а для этой платы — digilentinc.com/Products/Detail.cfm?NavPath=2,66,768&Prod=DIGILENT-PLUGIN

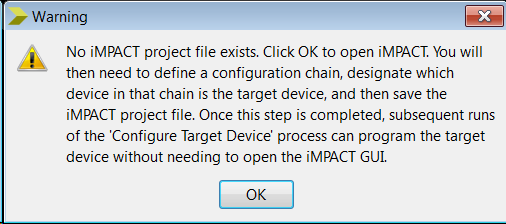

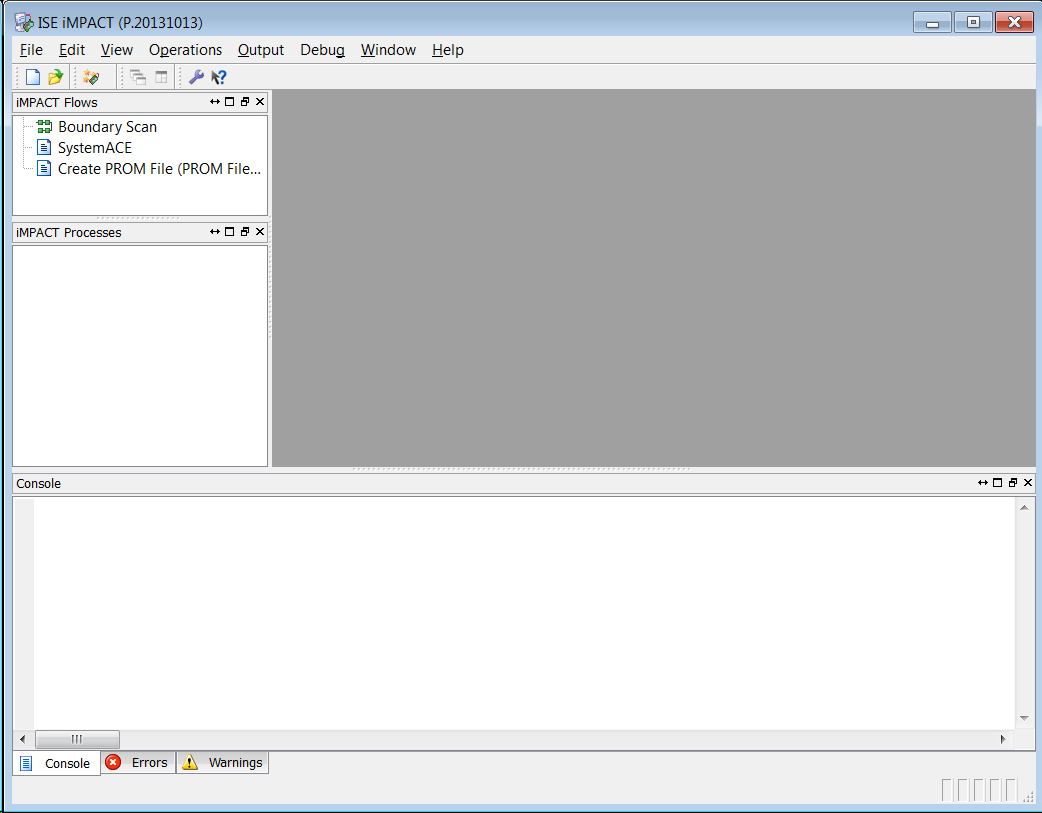

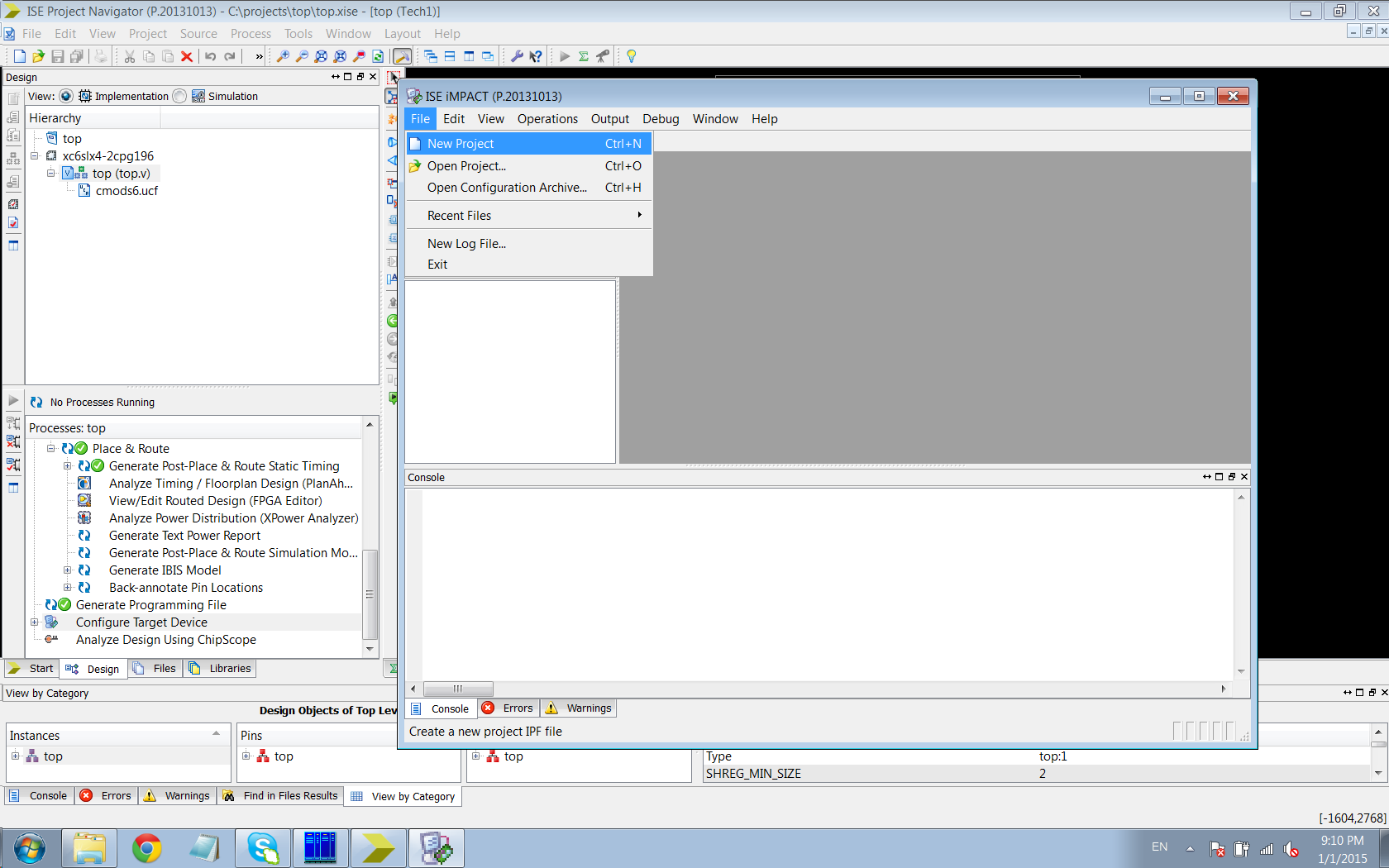

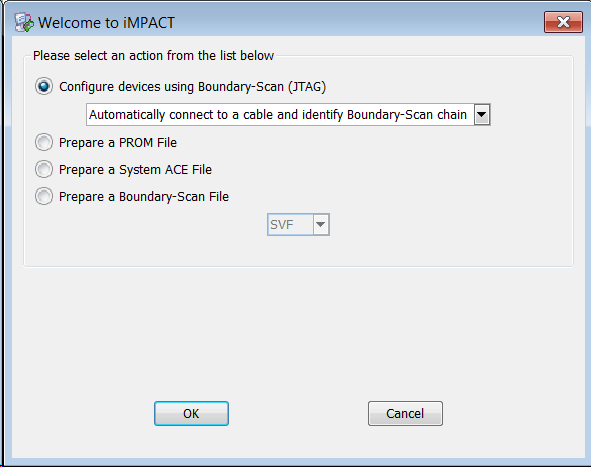

У Digilent-а есть еще софтвер под названием Digilent Adept, но он на моем компьютере с этой платой почему-то не работает, так что лучше использовать плагин и iMPACT. Последовательность действий ниже понимать не обязательно, это просто „магические заклинания“, чтобы перенести *.bit файл в конфигурационную память внутри FPGA:

Все, теперь плата должна работать — откликаться на нажатия кнопок и соответственно им мигать лампочками.

Теперь не будем закрывать iMPACT, вернемся к главному окну ISE и построим не комбинационную, а последовательностную схему — сдвиговый регистр. Используем генератор тактового сигнала низкой частоты 1 Hz, т.е. один раз в секунду. На плате еще есть генератор тактового сигнала на 8 MHz — это частоту с помощью PLL можно поднять до 200 MHz. Но высокая частота — это других дизайнов, а для наглядности 1 Hz — то что надо:

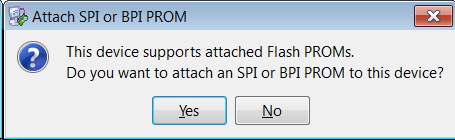

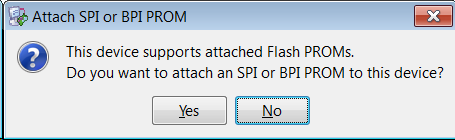

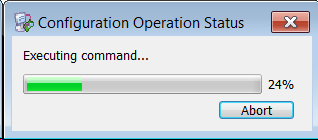

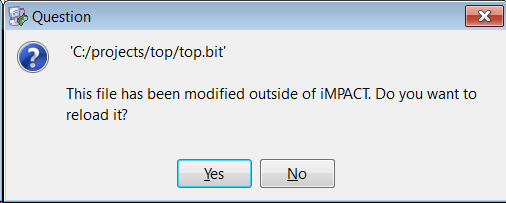

Засинтезируем ее, сгенерим bit-файл, вернемся в iMPACT и нажмем на кнопку Program. Оно скажет:

Нужно нажать Yes и в FPGA будет загружен новый дизайн. Кстати, теоретически повторная (после создания iMPACT project) загрузка должна происходить просто нажатием Configure Target Device в главном окне ISE, но реально у меня это не происходит — софтвер норовит создать новый iMPACT project. Поэтому и лучше использовать кнопку Program внутри окна iMPACT. Все претензии по этому поводу — в Digilent и Xilinx.

Приложение A. Два видео — как реализовать сдвиговый регистр и счетчик

Приложение B. Полный заголовок верхнего модуля на верилоге для данной платы

Со всеми соединениями и комментариями:

module cmods6

(

input CLK, // FPGA_GCLK, 8MHz - можно поднять до 200 MHz

input CLK_LFC, // FPGA_LFC, 1 Hz

output LED_0, // Четыре лампочки

output LED_1,

output LED_2,

output LED_3,

input BTN_0, // Две кнопочки

input BTN_1,

// DEPP interface - интерфейс для связи с PC через USB

input DEPP_ASTB, // Address strobe

input DEPP_DSTB, // Data strobe

input DEPP_WRITE, // Write enable (write operation = 0, read operation = 1)

output DEPP_WAIT, // Ready

inout [7:0] DBUS,

// General purpose I/O - куча пинов для брэдборды

input [7:0] PORTA,

input [7:0] PORTB,

output [6:0] PORTC,

input [7:0] PORTD,

input [7:0] PORTE,

output [6:0] PORTF

);

Приложение C. Где взять платы

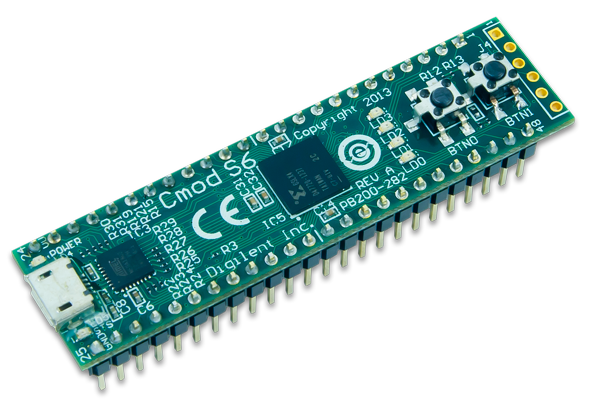

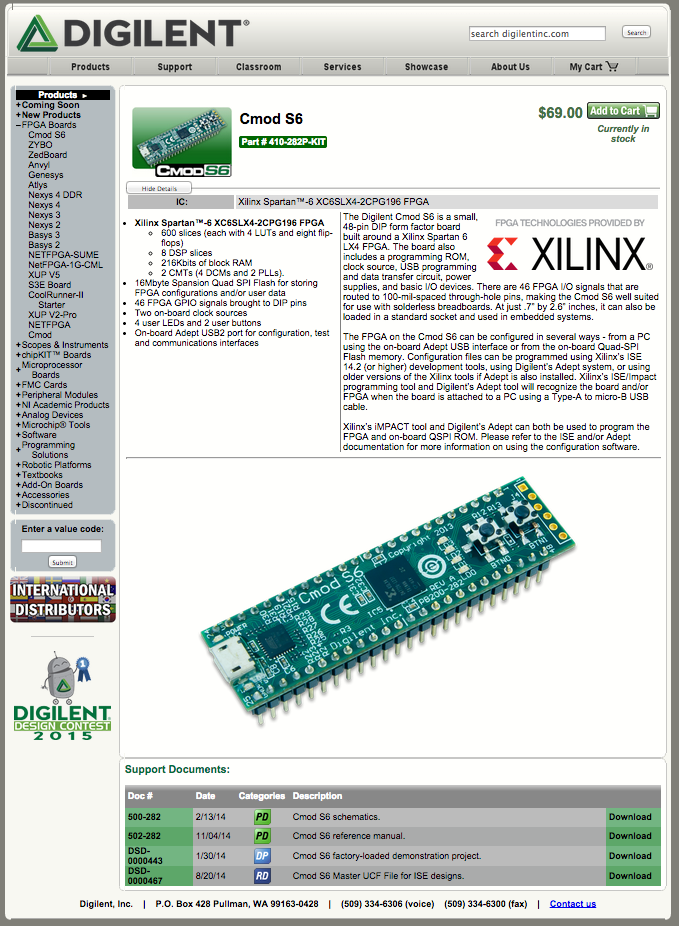

Платы с Xilinx FPGA можно брать на сайте Digilent, сейчас это отделение National Instruments. Вот плата Digilent Cmod S6, которую я использовал в посте, с самым небольшим Xilinx Spartan-6 FPGA:

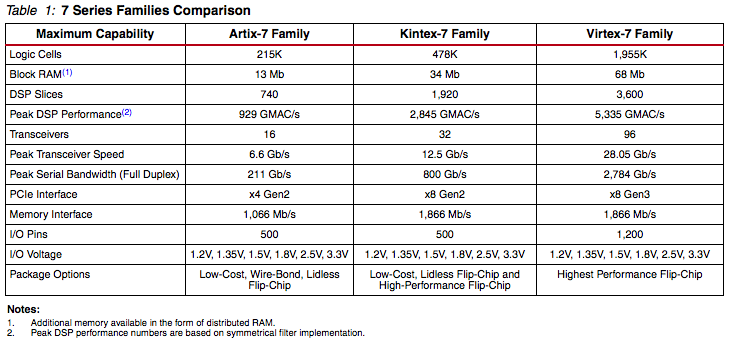

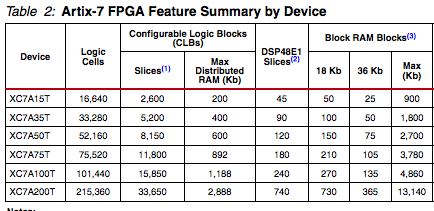

Для последующего обучения есть например платы Nexys 4 с более мощными FPGA Xilinx Artix-7. На них не нужно скручивать провода на макетной плате, так как эта стадия обучения уже пройдена:

Про платы с Altera FPGA я напишу другой пост.

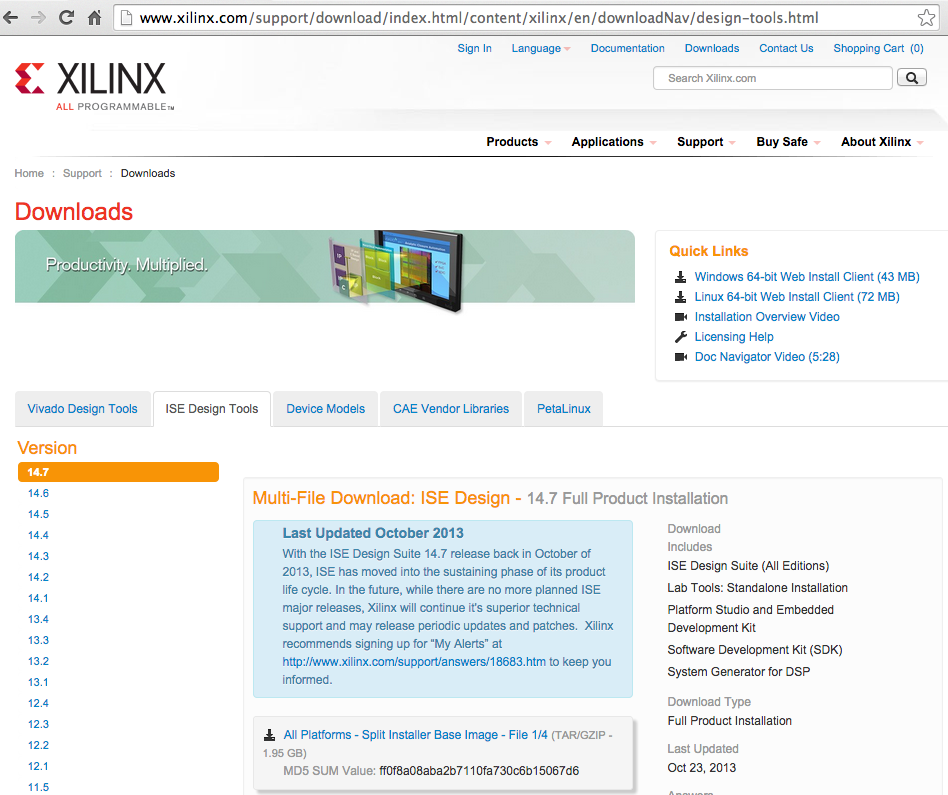

Приложение D. Где взять софтвер Xilinx ISE

Его можно загрузить прямо с сайта Xilinx. Использовать можно бесплатную версию. Но для Spartan-6 нужно использовать не самую новую версию среды разработки Xilinx Vivado 2014.4, а Xilinx ISE 14.7 2013 года. Почему не Vivado? Маркетологи в Xilinx решили пересадить всех пользователей чипов Spartan на более новые FPGA Artix, и выключили поддержку для Spartan из нового софтвера. Вот только плат, которые можно вставлять в макетную плату, на Artix еще нет. Поэтому нужно использовать версию софтвера 2013 года:

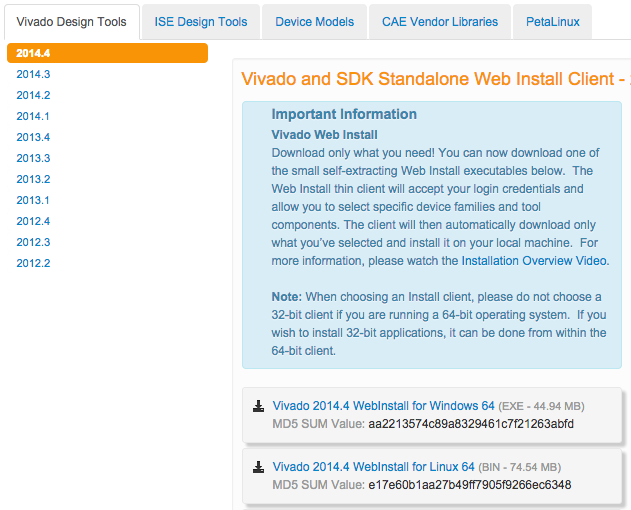

А вот софтвер Xilinx Vivado который подерживает в частности плату Nexys 4 с Xilinx Artix-7 (для платы со Spartan-6 он не нужен):

Теперь важный момент. Для того, чтобы загружать .bit-файл в конфигурационную память FPGA на плате, необходимо скачать специальный плагин с сайта Digilent:

На сайте еще есть софтвер Digilent Adept, но я его не рекомендую для Spartan-6, у меня были с ним проблемы.

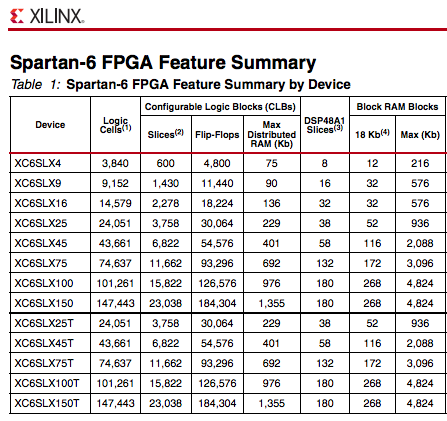

Приложение E. Немного табличек с параметрами FPGA

И в заключение еще одна фотка FPGA платы на макетной плате с кнопками, резисторами и семисегментным индикатором:

Автор: YuriPanchul