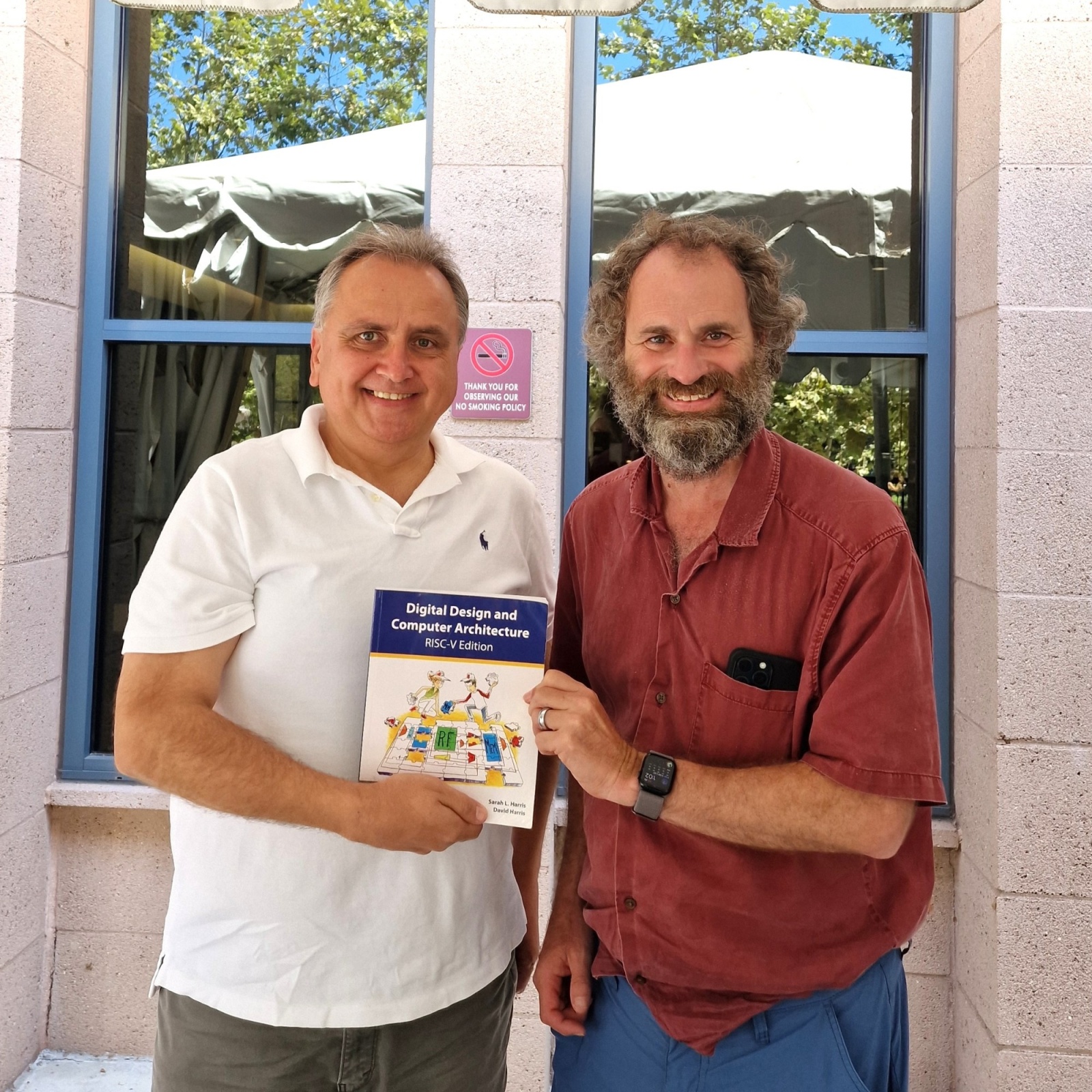

Встретился на ланч с Дэвидом Харрисом, автором (вместе с Сарой Харрис) популярного учебника "Цифровая Схемотехника и Архитектура Компьютера", который за последние 10 лет помог закрыть монументальную дыру в техническом образовании десятков вузов России и Украины. До этого учебника во многих вузах сразу после триггеров шло программирование микроконтроллеров, то есть у студентов раньше вообще не возникала база для проектирования современных чипов по маршруту RTL-to-GDSII, технологии, которая за последние 30 лет привела нас к смартфонам, быстрому интернету и ускорителям ИИ.

Учебник Дэвида активно используется на Школе Синтеза Цифровых Схем, которую поддерживают 24 российских и 1 белорусский университет. Регистрация на новый сезон Школы только что открылась.

Фокус "Цифровой Схемотехники и Архитектуры Компьютера" - на логическом проектировании на уровне регистровых передач, с помощью языков описания аппаратуры Verilog и VHDL. Хорошим подспорьем к этому учебнику является российский учебник "Цифровой Синтез: RISC-V" от коллектива авторов под эгидой ВШЭ МИЭМ, который привязывает материалы Харрисов к лабораторным работам на ПЛИС/FPGA, а также дополняет Харрисов например систолическими массивами, которые используются для ускорения вычислений машинного обучения.

При этом Дэвид Харрис - соавтор еще и учебника по физической стороне проектирования микросхем: CMOS VLSI Design: A Circuits and Systems Perspective, который глубже копает в сторону кремния и транзистора. К сожалению, пока эта книга еще не переведена на русский язык, хотя ее высоко оценивал например бывший замдиректора НИИСИ, специалист по радиационно-стойким чипам Максим Горбунов.

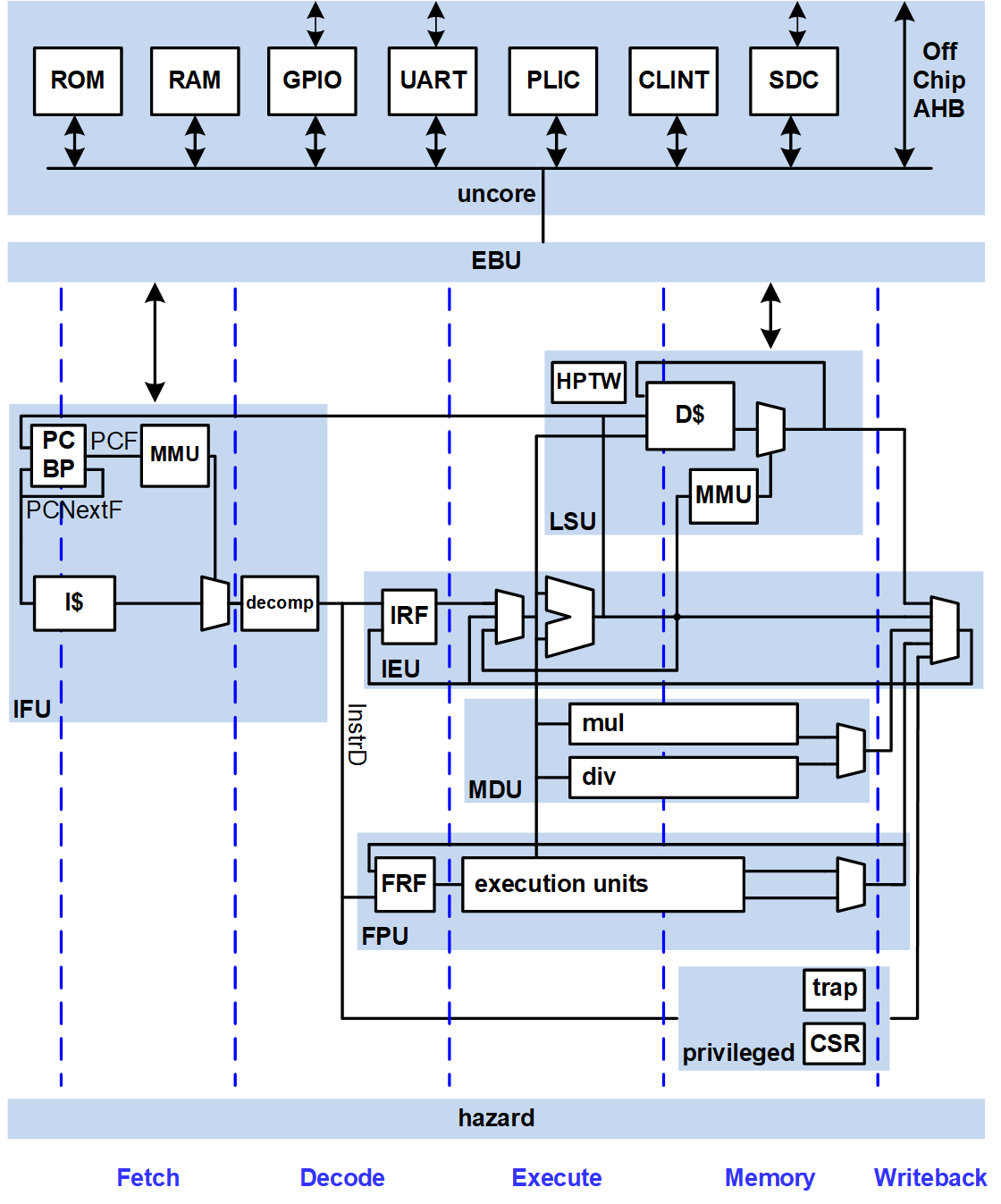

И вот при встрече я узнал, что пару лет назад Дэвид решил прокопать и в другую сторону, и написал (тоже с Сарой Харрис и еще двумя соавторами) книгу с углубленным изучением проектирования микроархитектуры процессоров. Она называется RISC-V Microprocessor System-On-Chip Design и выходит в январе. Дэвид поделился со мной манускриптом и я могу пересказать содержание.

У новой книги Дэвида Харриса довольно четко очерченная поляна:

-

Не игрушечный, но и не навороченный. Минимально необходимый для Линукса.

С одной стороны, описанный в книге открытый процессор Wally не является игрушечным учебным процессором типа schoolRISCV. Wally содержит предсказатель переходов, кэши (в том числе многосекционные), устройство управления виртуальной памятью (TLB MMU), контроллер прерываний и поддержку арифметики с плавающей точкой.

С другой стороны, Дэвид и соавторы сознательно отказались идти дальше и описывать суперскалярные процессоры и многоядерные кластеры с кэш-когерентностью (протоколы MESI). То есть их процессор - это минимальный процессор, на котором может работать Линукс и есть плавающая точка. И точка. На языке маркетинга процессор Wally стоит между microcontroller-class core и mid-range embedded processor core. Mid-range процессоры (но без плавающей точки) ставят например в домашние роутеры с OpenWrt Linux.

В принципе, книга Дэвида - не первая, которая описывает все детали проектирования процессора, до него была например книга Монте Далримпла. Но Монте - это вышедший на пенсию бывший разработчик Zilog, который начинал еще во времена, когда транзисторы процессора рисовали на бумаге карандашом. Поэтому процессор Монте - это минимальный микроконтроллер, без кэшей и Линукса. Кроме этого Монте долго был контрактором на custom версии Z80, владельцем малого бизнеса, поэтому книга Монте никак не передает процес разработки в большой компании, а вот книга Дэвида Харриса передает. Что немудрено - Дэвид работал в Интеле и Sun-е, то есть он хорошо знает про работу коллектива.

Также книга Дэвида Харриса описывает систему на кристалле, шины AHB и AXI. И в этом она тоже не первая - есть например полезная книжка Modern System-on-Chip Design преподователя из Кэмбриджа Дэвида Гривса. Однако книжка Гривса не привязана к коду на гитхабе, а вот у Харрисов - привязана.

Та же проблема у книги Modern Processor Design: Fundamentals of Superscalar Processors by John Paul Shen and Mikko H. Lipasti - в ней есть про суперскалярные и многопоточные процессоры, но она не привязана к коду, который можно симулировать, синтезировать, ставить эксперименты с производительностью итд. Кстати Дэвид Харрис тоже хочет добавить многопоточность в их ядро. Но не суперскалярность - и вот тут возникает открытая возможность для других авторов, может даже российских?

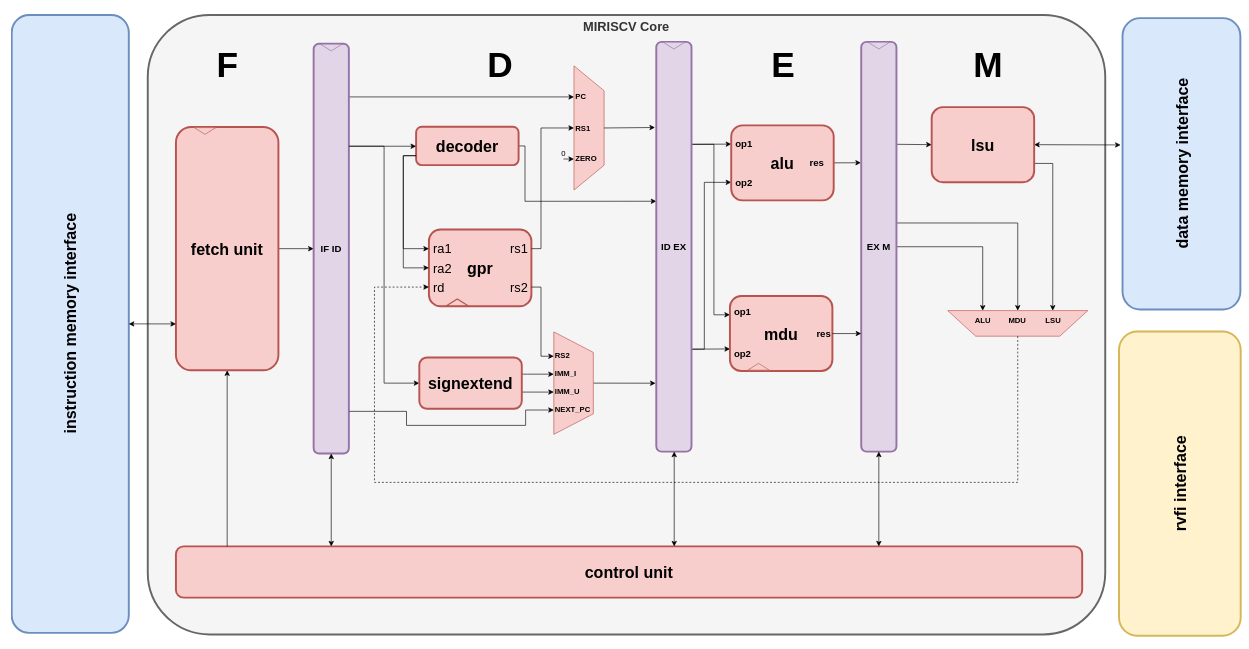

Раз уж мы заговорили о российских авторах - сейчас в зеленоградском МИЭТ идет работа над курсом по дизайну и верификации их собственного процессорного ядра MIRISCV, которое миэтовцы собираются развить примерно до такого же состояния, что и ядро Wally. Это означает, что в МИЭТ уже сейчас может сравнивать напрямую как эти ядра (дизайн, бенчмарки), так и процесс их верификации и синтеза. Это очень полезно! Для всего развития российcкой экосиcтемы.

Описание разработки и верификации процессора по взрослому

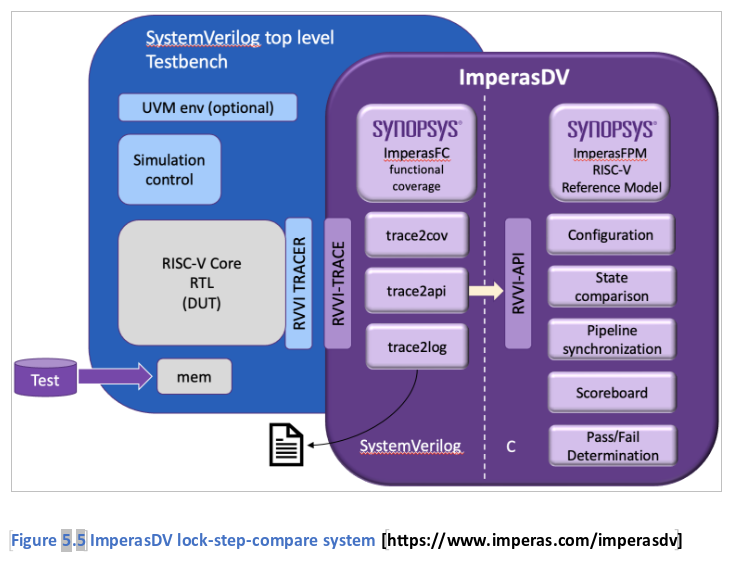

Дэвид Харрис и соратники впервые на моей памяти описали все аспекты разработки, в том числе верификацию RTL против архитектурной модели. То есть берется (или генерируется) тестовая программа, и она скармливается двум сущностям:

-

Первая сущность - это микроархитектурное описание процессора на языке SystemVerilog, на уровне регистровых передач (Register Transfer Level - RTL), с тактовым сигналом и стадиями конвейера. Это описание в процессе синтеза собственно и превращается в файл в формате GDSII, по которому делается фотошаблон, по которому на фабрике выпекают микросхемы.

-

Втора сущность - это архитектурная модель RISC-V (в данном случае программа на Си от компании Imperas), которая ничего не знает о тактах, конвейере, интерфейсах с шинами, и реализует вид на процессор с точки зрения ассемблерного програмиста - видимые программисту регистры, ветвления, приблизительная модель кэша и виртуальной памяти.

В RTL/микроархитектурном описании, в конвейере одновременно обрабатывается несколько инструкций, и запуск инструкции на обработку не требует полного завершения предыдущей. В архитектурной же модели все инструкции выполняются последовательно, следующая начинается только после полного окончания предыдущей.

Но результат выполнения и в одной, и в другой сущности - это записи данных в архитектурные (то есть видимые программисту) регистры по завершению каждой инструкции. И вот эти результаты можно сравнивать. Почему? Хотя в RTL много параллельности, но дизайнеры процессора поддерживают иллюзию последовательного выполнения программы для своих пользователей - ассемблерных програмистов и создателей компиляторов.

И вот Дэвид описывает как делается такое сравнение конвейерной и архитектурной сущностей (мог бы сказать "сравнение микроархитектурной и архитектурной моделей", но так как код на RTL превращается в конечном итоге в железо, в транзисторы и дорожки, то язык не поворачивается назвать этот код"моделью").

Далее в книге Дэвид c коллегами описывают всего понемножку, чтобы читатели знали, что бывает в каждом процессорном проекте, и где искать подробности: про прототипирование на FPGA, про запуск на спроектированном процессоре операционки Линукс, про отладку после пробного производства (post-silicon debug) и даже про писание Tcl скриптов для синтеза.

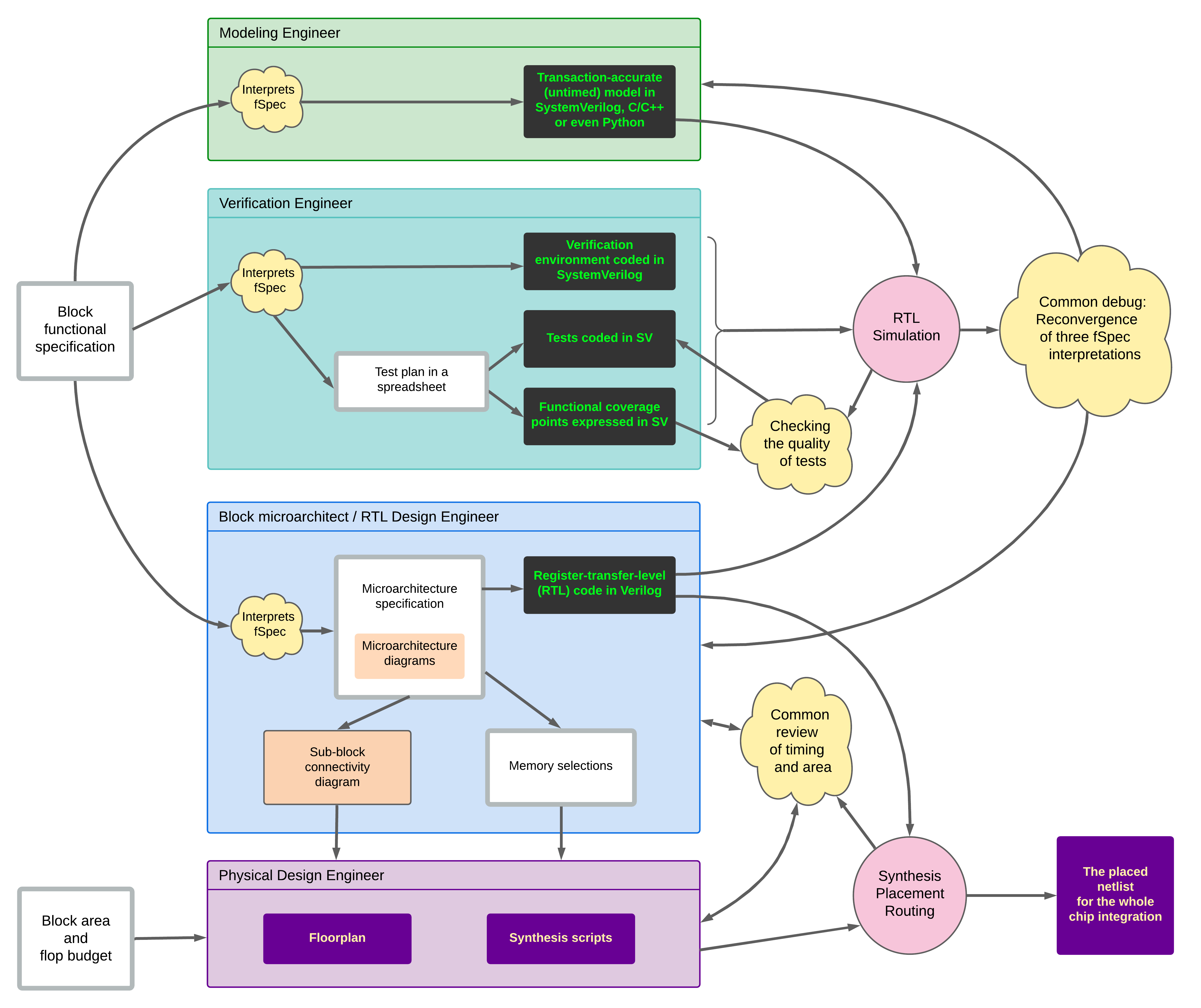

Для иллюстрации можно привести мою собственную картинку взаимодействия инженеров в проекте блока, которую я нарисовал для статьи про аппаратное ускорении ИИ в российском альманахе AI Report от МФТИ. В ней показано как взаимодействуют:

-

Инженер по архитектурному моделированию;

-

Инженер-верификатор, три роли: создатель среды верификации, создатель тестовых сценариев и специалист по проверке функционального покрытия (то есть проверки полноты тестов);

-

Микроархитектор блока / проектировщик на уровне регистровых передач;

-

Инженер по физическому проектированию.

Теперь ответы на вопросы читателей

У меня накопились вопросы читателей предыдущих книг Харрисов с телеграм-канала Школы Синтеза Цифровых Схем, а также канала icDesignCommunity и fpgasystems. Я задал Дэвиду не все вопросы, так как беседу в основном вел Дэвид, но пару ответов он сформулировал:

-

Рекомендации как начинать жизнь молодому инженеру

Дэвид работает в частном университете Harvey Mudd College, который является довольно нестандартным местом. Хотя университет всего 4-х летний и не так известен как Беркли и MIT, но он находится в топе по средней зарплате выпускников-бакалавров. Разумеется, выпускник не обязан ограничиваться 4-мя годами - потом он может идти получать магистра в Калтех, MIT или Стенфорд если захочет.

Подход Дэвида: лучше всего, если студент изучит основы и попробует на практике три разные инженерные специальности, например цифровую электронику, механический инжиниринг и скажем оптику или материалы. То есть посмотрит на решение инженерных задач в разных областях. Тогда он заодно научиться как осваивать и другие области, тем более что большинство деталей технологий за 5 лет все равно устаревают.

В прошлый визит к Дэвиду в 2015 году я смотрел как его студенты проектируют подводного робота - пример разноплановой инженерной задачи:

-

Что вы думаете про AI?

Дэвид сказал что AI проникает во все места, в частности аппаратные ускорители ML вычислений. А также что он использует ChatGPT в обучении, следующим образом: после каждого занятия Дэвид дает для домашней работы семь вопросов, из которых шесть - обычные, а вот на седьмой вопрос нужно ответить с помощью ChatGPT, причем проанализировать все возникающие у ChatGPT галлюцинации и, с помощью уточнений, привести его к правильному ответу.

-

Что Дэвид думает про факт, что студенты плохо решают жизненно важные для RTL позиций в компаниях типа Самсунга микроархитектурные задачи?

Тут уж я пожаловался Дэвиду, что студенты плохо решают задачи на контроль потока данных и подобные (я описал проблему в 1, 2, 3 и 4). Сначала Дэвид сказал, что учебная программа не резиновая, и он сам жалеет, что не имеет возможность развернуто поговорить о других сторонах электроники, в частности про физические аспекты транзисторов. Но потом, когда я объяснил Дэвиду актуальность таких микроархитектурных приемов для задач в сетевых чипах и GPU, он согласился, что про это стоит написать книгу или главу и предложил мне этим и заняться.

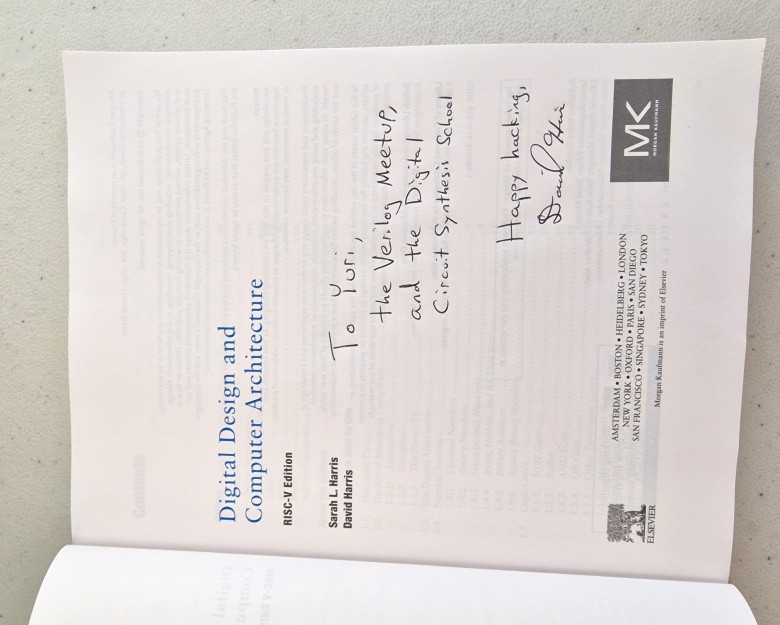

В конце Дэвид пожелал всем успеха и оставил автограф мне, клубу Verilog Meetup и Школе Синтеза Цифровых Схем / Digital Circuit Synthesis School:

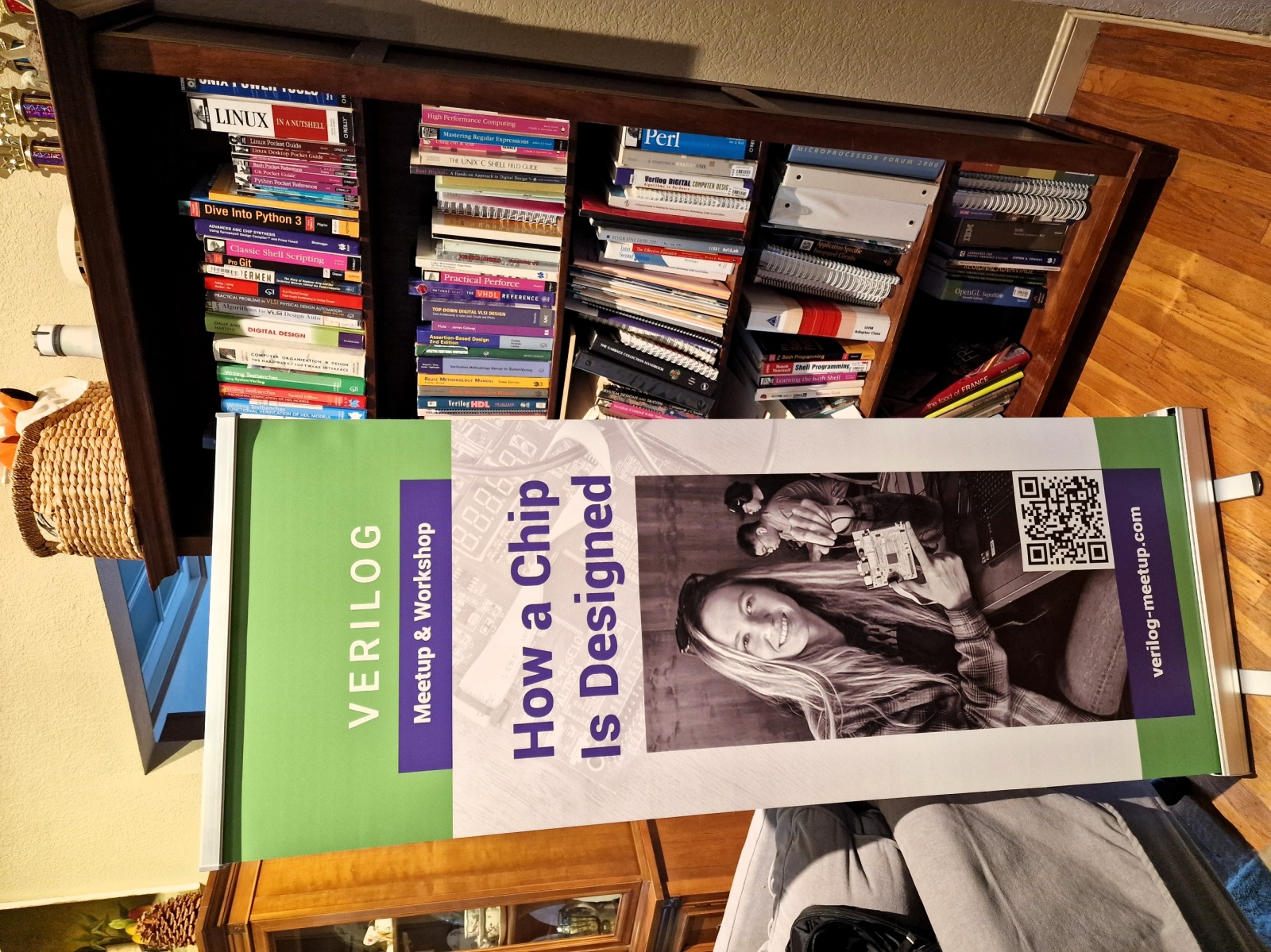

На следующий день после встречи с Дэвидом Харрисом я проводил выездную встречу клуба Verilog Meetup в Лос-Анжелесе. Обычно мы встречаемся в городе Горный Вид (Mountain View) в Silicon Valley. Встречу в Лос-Анжелесе я рекламировал для трех категорий слушателей:

-

Для интересующихся, что собственно делает в офисе инженер, который проектирует блоки микросхемы в телефоне Самсунг Галакси. Или Apple iPhone. Или вообще космической ракете от Роскосмоса или Blue Origin. База технологии, идея цифровой логики (комбинационная + последовательностная), как работает инженерная группа.

-

Для студентов и их родителей, которым может быть полезно понять, как готовиться к поступлению на работу после окончания университета. Для людей в индустрии не секрет, что куча отличников топовых вузов банально проваливаются на интервью в электронные компании, потому что они запомнили слайды с лекций, но не делали практических проектов. Или делали проекты, но не проверяли особые случаи, ожидая что профессор проверит. Поэтому надо практиковаться, например в формате клуба Verilog Meetup.

-

Также такие встречи полезны для инженеров, которые уже работают в электронной или софтверной промышленности, но делают не дизайн на уровне регистровых передач, а заняты чем-нибудь смежным и хотят или сменить профессию, или расширить области, в которых они разбираются. Бывают Design Verification (DV) инженеры, которые хотят стать RTL инженерами, программисты firmware которые хотят стать DV инженерами, инженерами которые заняты post-silicon debug, которые хотят стать RTL или DV. Или программисты инфрастуктуры из Гугла или Амазона, которые хотят расшириться в хардверную инфраструктуру, или full stack инженеры которые хотят стать еще более full stack.

Для встречи в LA я подготовил вот такие слайды, а также принес плат с микросхемами FPGA / ПЛИС, так как без демо на платах слушатели часто скучают. Пришли 13 человек (16 с организаторами), из которых были русские, украинцы, армяне, в том числе русский програмист (вроде из Гугла или Амазона) с дочерью, другие серьезного вида старшие школьники, в том числе владеющий Линуксом, а также индийский инженер из Интела и китайский инженер, который был интерном у нас в Самсунге, а сейчас работает проектировщиком в LA.

Вот как это выглядело на Youtube (краткие видео):

и на RuTube:

Это видео и фотографии приготовил видеограф Арсений Кристенко из агентства FlexibleMedia . Мероприятие помогла провести дизайнер Оксана Мелис , которая также сделала вот такой плакат слева. На плакате изображена Мария Горбунова, выпускница Санкт-Петербургского государственного университета аэрокосмического приборостроения (ГУАП), которая сейчас работает в компании Broadcom и иногда наведывается к нам на Verilog Meetup в Silicon Valley.

Я также сделал полную запись на три часа всей презентации с помощью Zoom и выложил ее на YouTube:

И RuTube:

Тут может возникнуть вопрос: в чем вообще прикол учиться проектировать чипы для школьника, если производство скажем чипа для смартфона на фабрике стоит десятки миллионов долларов?

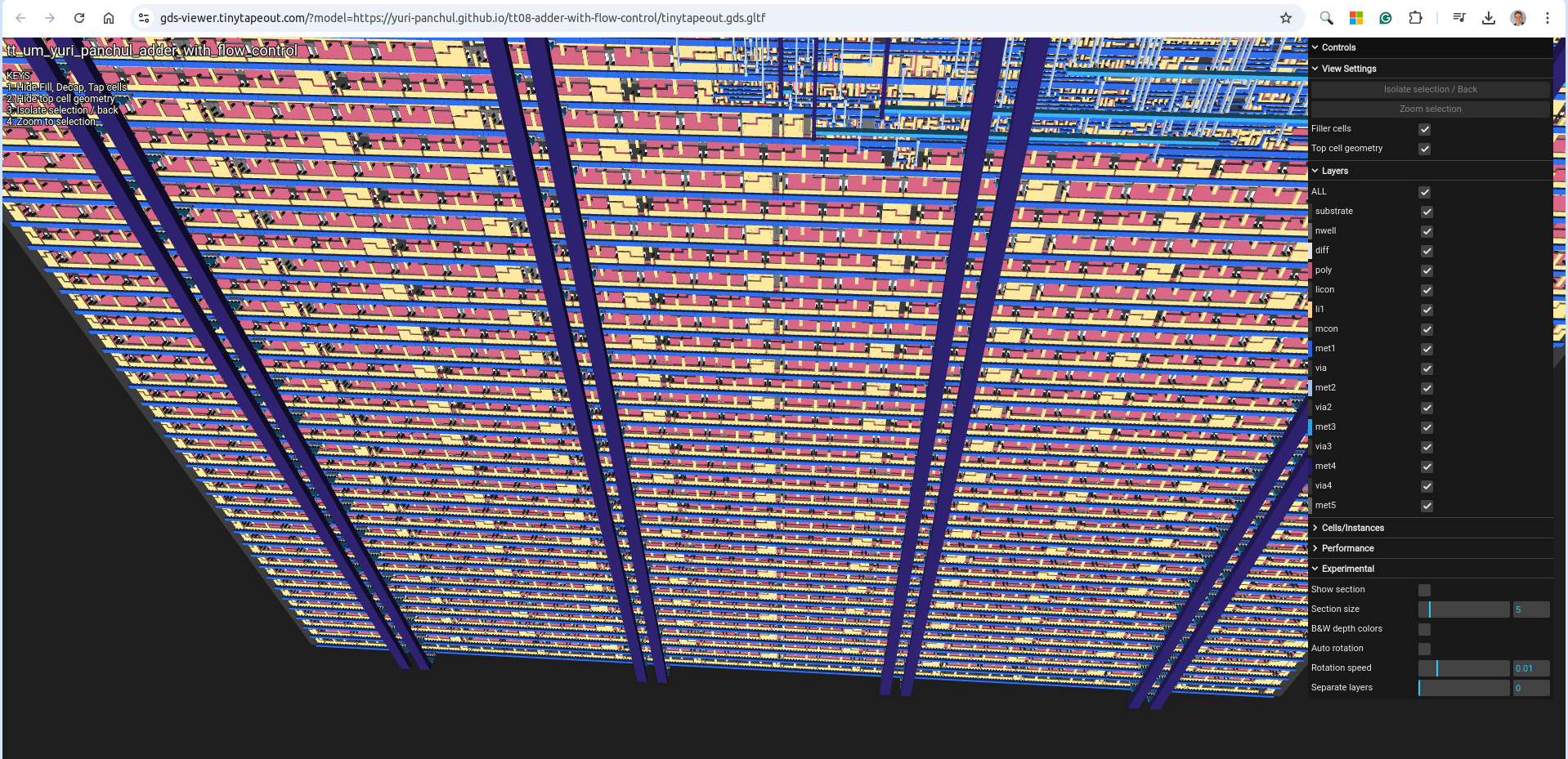

Так вот перед встречей в LA меня сконтактировал Матт Венн (Matt Venn), основатель сервиса Tiny Tapeout, который позволяет произвести свой чип на фабрике любому школьнику.

Работает это так: помимо коммерческого производства (которое стоит миллионы долларов), есть так называемый shuttle service - для исследователей и малосерийного экспериментального производства микросхем. Этот сервис стоит тысячи или десятки тысяч долларов. Так вот Матт Венн придумал как каждый чип для shuttle / MPW (multi-project wafer) распилить еще на 50 заказчиков, чтобы каждый платил всего $150+, а самые умные не платили вообще ничего (если например участвуют в соревновании кто сделает лучшую аппаратную графику).

Я напишу про Tiny Tapeout отдельный пост и однозначно интегрирую в будущем проекты с Tiny Tapeout во все свои семинары в разных странах. Пока же я, не отходя от кассы, заказал производство трех пробных дизайнов:

-

Adder with Flow Control - вопрос на интервью, которым я мучаю студентов-отличников.

-

schoolRISCV CPU with Fibonacci program - школьный процессор от Станислава Жельнио.

-

Sea Battle VGA game with sprites - видеоигра со спрайтами, чисто в хардвере, без процессора и софтвера. Вообще она выглядит скорее как "Ракета и Дрон", но я назвал ее "Морской бой", чтобы не смущать никого ассоциациями.

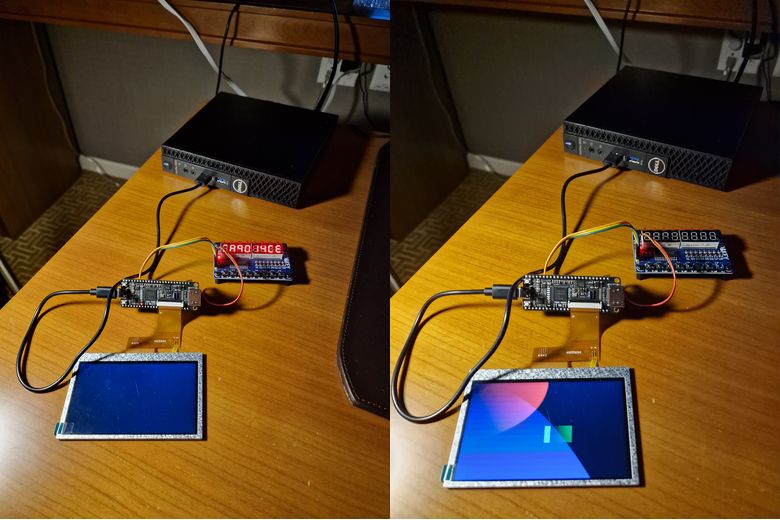

Помимо симуляции и производства на фабрике, у дизайнера есть еще одна опция - реализовать свою схему на микросхемах реконфигурируемой логики ПЛИС / FPGA. Я принес платы с такими микросхемами на встречу в LA, и показал участникам, как соединить FPGA с графическими экранчиками и рисовать статические и движущиеся картинки:

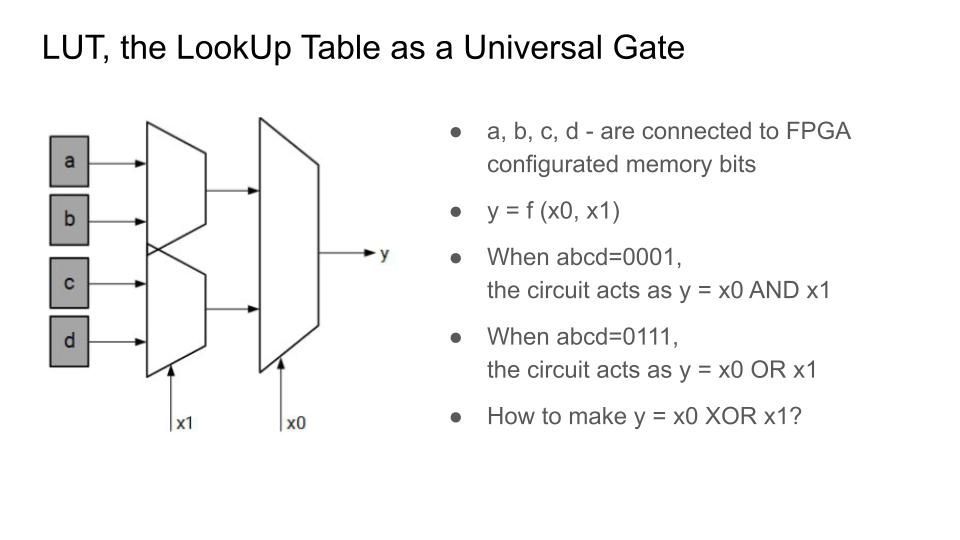

Как это работает? FPGA - это матрица из ячеек, в которых стоит конструкция под названием Lookup Table, или LUT. Простой LUT можно построить из трех мультиплексоров, аппаратных аналогов софтверного оператора "if". У такого LUT есть шесть входов и один выход. Четыре входа, константы a, b, c, d - берутся из битов памяти конфигурации. Еще два входа - x0 и x1 - переменные. В зависимости от значений a,b,c,d вся конструкция работает либо как логическая операция И над x0 и x1, или как логическая операция ИЛИ, или как любая другая булевская функция от переменных x0 и x1.

В ячейках FPGA также есть элементы состояния, D-триггеры, которые позволяют строить схемы с тактовым сигналом: счетчики, конечные автоматы и конвейеры.

Кроме встречи в LA мы каждое воскресенье проводим встречи в клубе хакеров Hacker Dojo в Маунтин-Вью, Калифорния. Встречи сообщества Verilog Meetup начинаются в 11 утра и проходят до 2 часов дня. На заседания заходят инженеры из Apple, Google, Intel, Amazon, NVidia итд. Мы в основном заняты созданием новых примеров на верилоге и поддержкой новых FPGA плат. Под лозунгом "Образовывай себя с помощью образования других". Выглядит это так: в YouTube:

В RuTube:

18-20 октября наше сообщество Verilog Meetup будет участвовать в выставке самоделкиных Maker Faire в городе Вальехо, который кстати два раза был столицей Калифорнии:

На выставке мы будем демонстрировать в частности вот такой набор для экспериментов с FPGA на основе микросхем от GoWin Semiconductor, китайской компании, у которой есть отличный шанс отобрать часть образовательного рынка от американских компаний Xilinx (часть AMD) и Altera (часть Intel).

Если вы живете в области сан-францисского залива и хотите билет на Maker Faire бесплатно, заходите на заседания Verilog Meetup по воскресеньям. Соберете установку, запустите на ней все примеры - получите билет (у меня есть пять билетов для таких целей). Кому билетов не хватит, можете их купить здесь.

А если напишите адекватную инструкцию по сборке платы и запуску примеров на любом из языков народов СССР (русский, украинский, армянский, азербайджанский и другие) - получите и весь комплект бесплатно. Комплект уже одобрил например преподаватель из Швейцарии.

Тут надо сказать, что движение за улучшение преподавания электроники происходит не только в Америке и Китае, но и например на Украине. Где за это дело взялись известные преподаватели-активисты Евгений Короткий и Сергей Иванец, из Киевского и Черниговского Политехов соответственно. С Евгением и Сергеем мы еще в 2016-2017 года организовали пару семинаров в Киеве (Короткий - это на фото высокий с лампочкой). Короче, они пришли в Киевскую Школу Экономики, где в духе Евроинтеграции скооперировались с европейским университетом ETH Zurich, совместная программа с которым стартует в этом месяце.

Эти программы полезно анализировать, особенно россиянам. Например из описания 227-0116-00L VLSI 1: HDL Based Design for FPGAs видно, что там не хватает времени на микроархитектуру, но зато есть моменты по верификации, в которых, по моему опыту с практикантами, плавают даже выпускники Стенфорда. Еще полезно смотреть на проекты на гитхабе от ETH Zurich, находить то, чего не хватает в российских программах (например DMA controller в PULP), писать свой аналог, потом ставить их в общий тестбенч и сравнивать. Пропускную способность можно сравнить на симуляции на уровне регистровых передач, а максимальную тактовую частоту, размер и оценку энергопотребления - можно определять с помощью синтеза с Open Lane. Если российcкий вариант лучше - рекламировать, если хуже - анализировать что пошло не так.

Ну и завершим тем, что как ни крути, но самую большую активность в освоений технологий Verilog, ASIC, FPGA, RTL-to-GDSII на пространстве бывшего СССР проявляют россияне в компании с беларусами. Только что открылась регистрация на новый сезон Школы Синтеза Цифровых Схем - образовательной инициативы, которую поддерживают 24 российских и 1 белорусский университет.

В этом сезоне к Школе Синтеза присоединился и университет в Курске, что лично меня особо греет, потому что один из моих прадедушек был учителем и директором школы в Курске, Курской и Белгородской губерниях Российской Империи (при этом дедушка с бабушкой и родители были связаны с киевским политехом).

Так что покупаем учебники, FPGA платы, регистрируемся и поздравляем друг друга с началом нового учебного года!

Автор: YuriPanchul