В России не любят Линукс. Студенты и корпорации всячески отлынивают его использовать, даже если Линукс насаждают преподаватели или госзаказчики. Но есть область, в которой Линукс придется полюбить. Это разработка микросхем. Даже внутри Apple и Microsoft инженеры используют Synopsys Design Compiler / IC Compiler и Cadence Genus / Innovus, у которых вообще нет версий для Windows и MacOS, только для Linux. Да, я знаю, что Synopsys и Cadence ушли из России. Но даже открытые тулы для синтеза ASIC - Open Lane - есть только под Linux.

Я уже несколько лет использую для семинаров по FPGA загружаемые через USB SSD диски, на который ставится весь необходимый софтвер. Такое решение позволяет избежать агонии первого дня семинара, когда приходит куча народу со своими ноутбуками, три часа ставят Quartus, а потом мучаются с драйверами USB Blaster для китайского контрафактного клона, который без танцев с бубном не хотят поддерживать ни Win10, ни Linux, ни особенно Win11.

С Win11 совсем трэшак - оно хочет подписанных драйверов, а какие подписанные драйверы для контрафактных USB бластеров, которые производятся в Китае типа 15 лет? У меня из-за этого чуть не накрылся семинар в Киргизии в прошлом году. Спасло только то, что университет еще не сделал апгрейд с Win10 на Win11. Сейчас я знаю, что можно было отключить эти подписанные драйверы. Или купить 20 плат не по $50, а по $200 - у дорогих плат такой проблемы нет. $1000 или $4000 - это большая разница.

А как же виртуальные машины? - спросите вы. С моей точки зрения они вносят дополнительный уровень танцев с бубном. И это не мое дремучее мнение - так же считает мой приятель, который работал над виртуализацией в Микрософте. То оно USB порт не пробивает, то еще какие-нибудь глюки. Плюс учить дополнительные опции, качать и копировать файлы в десятки гигабайт. А тут вставил в USB порт, и если загрузится, то заработает.

Конечно, загружаемые SSD тоже не без проблем: тут и Legacy BIOS boot против UEFI boot, и Secure Boot с Bit Locker, и зловещий "хвост GPT", и отрубание всего из-за скачка напряжения в USB хабе - но с этими проблемами мы методично разобрались. Решение я и описываю в этой заметке, предназначенной в первую очередь для учеников и руководителей кластеров в Школе Синтеза Цифровых Схем, которая начинается с сентября в 14 российских городах (объявления и точных дат еще нет, но уже записалось 200 учеников).

Прежде всего: как выглядит загружаемый SSD? А вот так. Всего $8 за 120GB (1 2) или $12 за 240GB. К нему еще нужен SATA-to-USB 3.0 адаптер за $3.46 (нужно внимательно смотреть чтобы брать USB 3.0 а не 2.0).

Тут вы можете спросить: А как же флешки? Зачем большие по физическому размеру SSD? Отвечаю: С флешек пускают всякие легкие программы типа Ардуино. Синтез цифровых схем - это тяжелые программы, использующие много памяти и работающие с кучей временных файлов. По моему опыту, на флешке они настолько раздражающе тормозят, что хочется выдернуть флешку и швырнуть ее об стену. Хуже раздражает только ChatGPT если дать ему задание написать конвейерный дизайн на SystemVerilog и он уверенно пишет несинтезируемый код по аналогии с C++.

Но вернемся к SSD. Начнем с использования. Предположим что я привез стопку SSD на семинар, или загружаемые SSD уже изготовил один из руководителей кластера Школы Синтеза Цифровых Схем.

Часть I. Загрузка с SSD

Нужно подключить SSD к выключенному компьютеру, потом включить компьютер и начать нажимать одну из клавиш для входа в BIOS. На разных компьютерах эти клавиши разные, на многих Esc или Del, но есть и другие:

-

ASUS, Acer: DEL или F2

-

Dell: F12 or F2

-

HP: F10

-

Lenovo: F2 или Fn + F2 (ноуты), F1 (десктопы), Enter + F1 (ThinkPad)

-

MSI: DEL

-

Samsung: F2

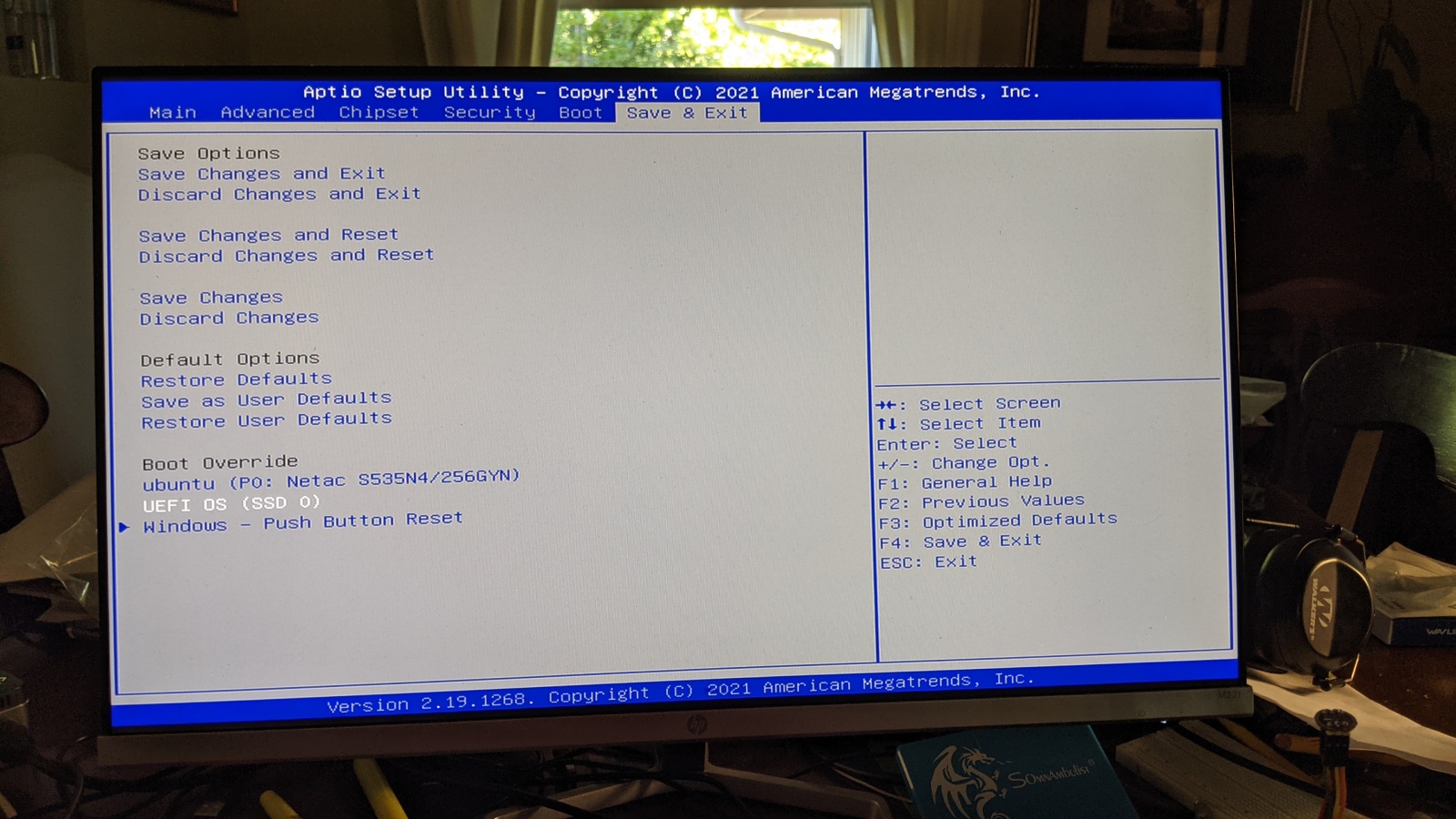

Если такой вход работает, то вы увидите меню вроде этого. С него можно загрузиться с SSD. SSD с Simply Linux, который мы сформировали, поддерживает и загрузку через UEFI, и более старую Legacy Boot загрузку:

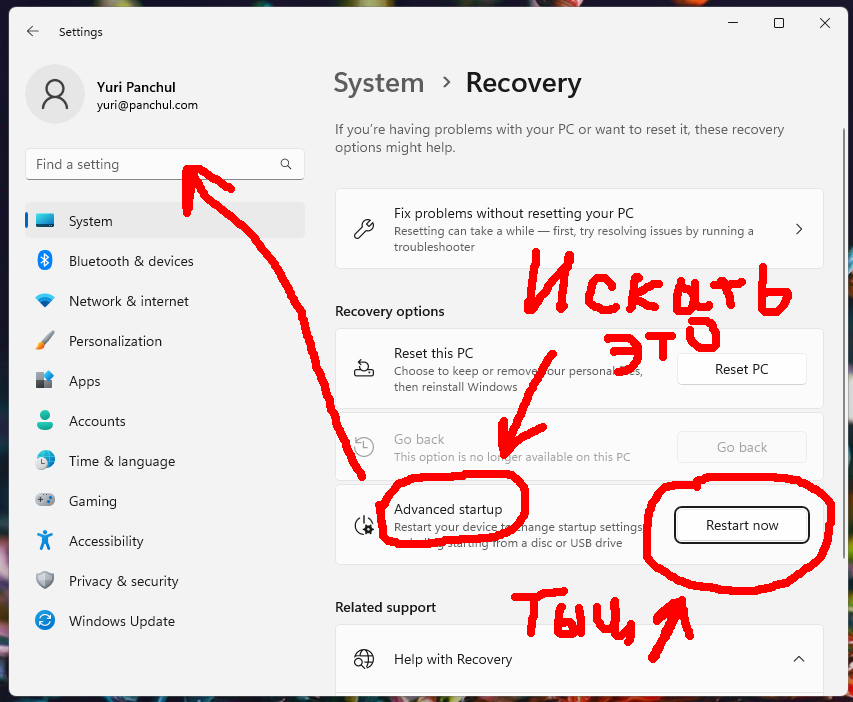

Что же делать, если клавиши при включении компьютера не работают? Это могут быть козни Микрософта - он сделал загрузку не-виндоус трудной в Windows 10 и Windows 11 с помощью Secure Boot и Bit Locker. В таком случае попробуйте загрузить Windows, пойдите в Settings и найдите там (Микрософт это спрятал, но через поиск находится) "Advanced Startup". Вы увидите кнопку "Restart now". Нажмите ее:

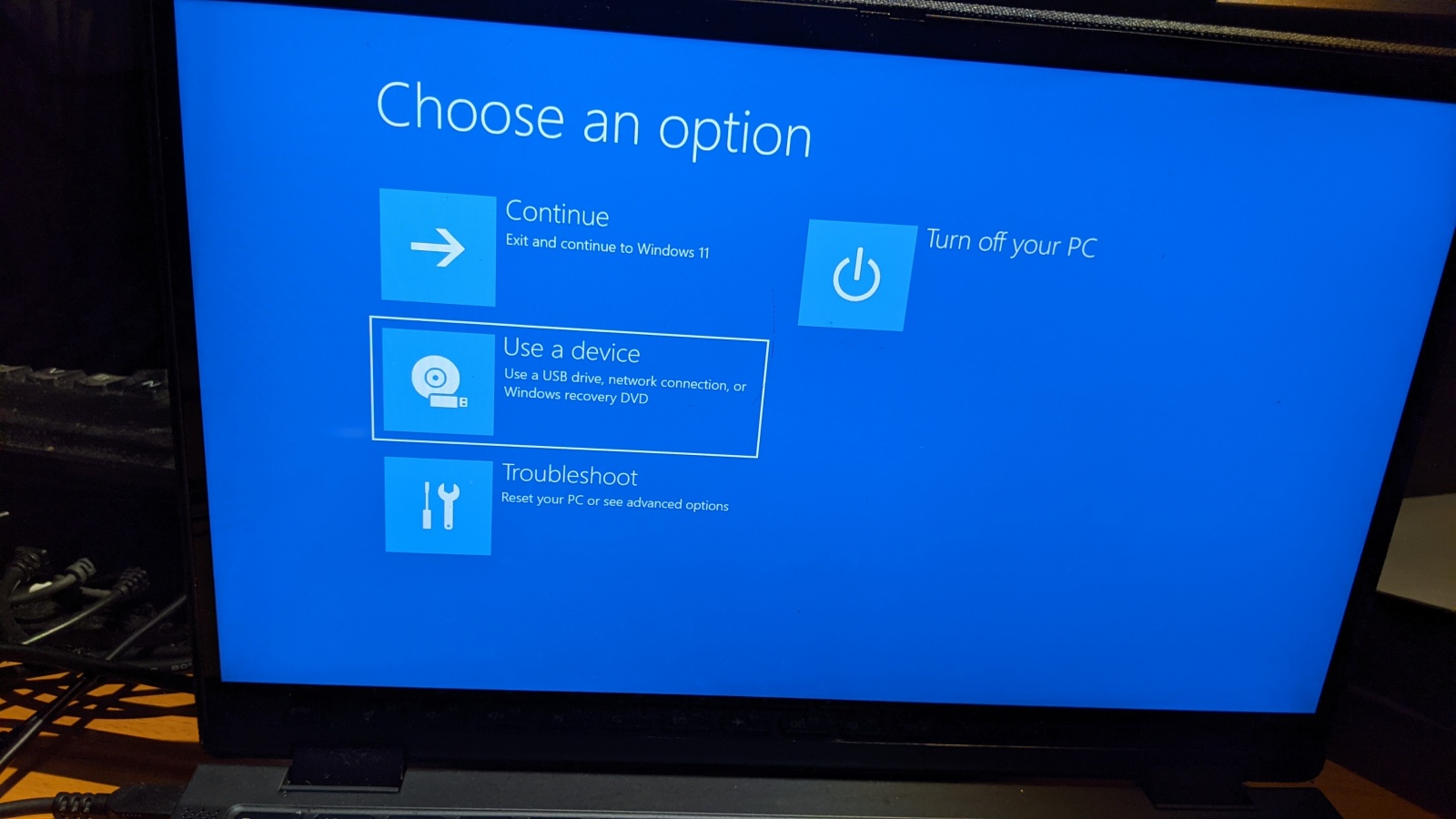

Система перезагрузится и вы увидите такой экран. Нажмите "Use a device":

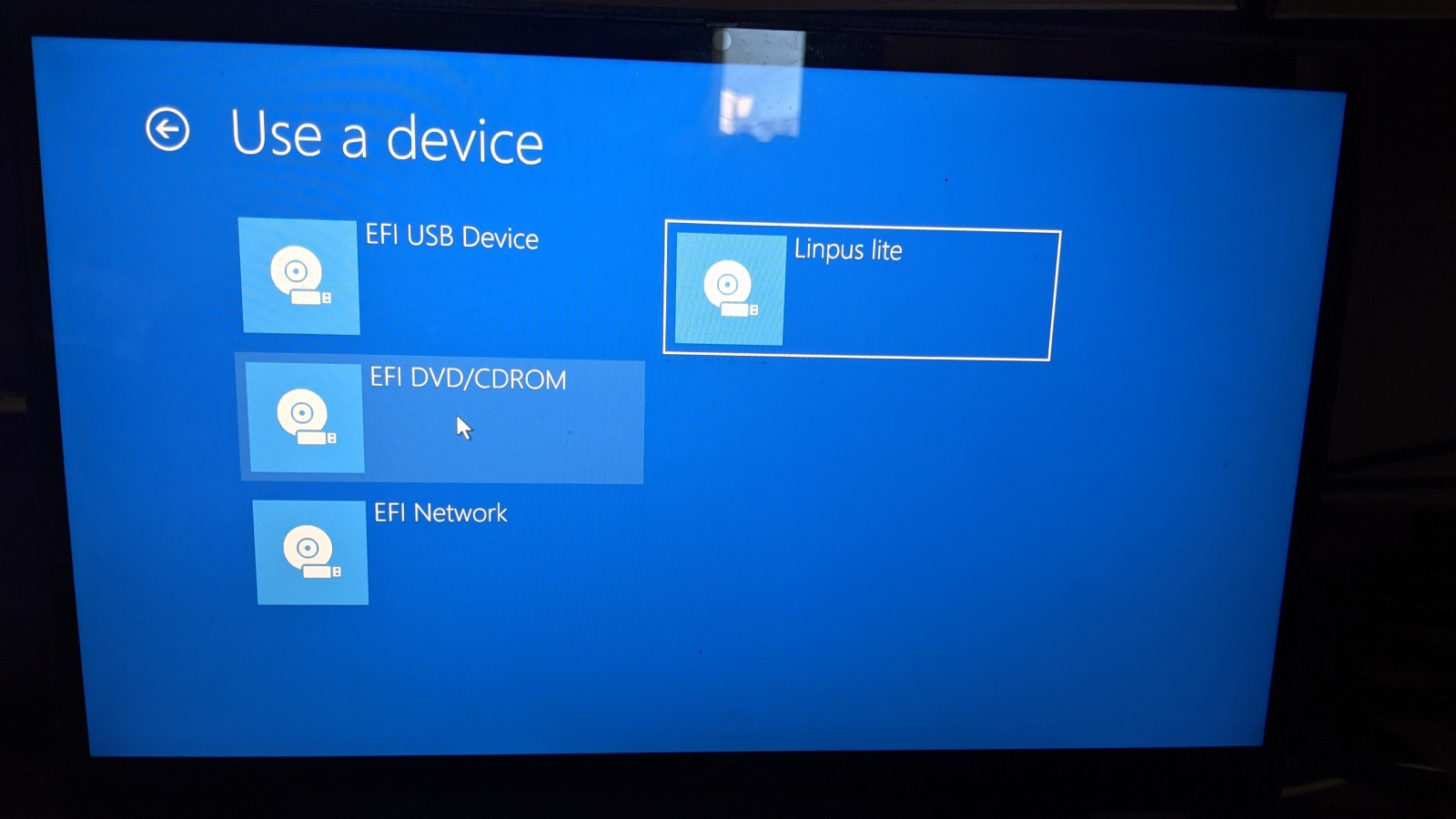

Теперь нажмите "Linpus lite". "EFI USB Device" тоже может работать, но не всегда:

После чего начинает грузиться Simply Linux:

Пароль пользователя verilog на загружаемом SSD - тоже verilog.

Почему мы выбрали именно Simply Linux от Базальта? Три причины:

-

Локальная российская поддержка.

-

Другие российские линуксы почему-то не бутились на компьютере Lenovo Yoga с secure boot. Для Astra Linux и RedOS появлялась ошибка "Error: Blocked by current security policy". С ROSA и Green Linux было что-то еще хуже (уже не помню что - типа Green загружался с SSD только на компьютер, на котором его устанавливали).

-

Отличия поменьше, например: симулятор Icarus Verilog на Simply ставился из пакета (правда только стабильная версия 11.0, версию 12.0 нам пришлось запрашивать). А вот на Astra Linux этот симулятор пришлось нетривиально строить из исходников, вместе с GTKWave. Хотя он в конце концов заработал, что говорит в пользу Астры, так как на RedOS и ROSA я построить Икарус из исходников так и не смог.

Часть II. Обновление репозиторий

После загрузки нужно обновить репозитории с примерами на верилоге. Для этого нужно подключиться к интернету, открыть терминал и проверить, каких из нужных пакетов не хватает (их нужно клонировать), а какие уже есть (их нужно обновить). Например если директория ~/projects/basics-graphics-music уже существует, то нужно ввести команды:

cd ~/projects/basics-graphics-music

git pullНо если директории ~/projects/basics-graphics-music нет, то

cd ~/projects

git clone https://github.com/yuri-panchul/basics-graphics-music.gitАналогичным образом нужно поступить с репозиториями https://gitflic.ru/project/yuri-panchul/valid-ready-etc и https://gitflic.ru/project/yuri-panchul/systemverilog-homework (они будут меняться весь август, сейчас первая в нестабильном состоянии, а вторая пустая).

Пару слов о содержании репозиториев.

-

Основной набор вводных примеров - репозиторий basics-graphics-music. Он похож на репозиторий прошлого года в Бишкеке, и примеры на Школе Синтеза прошлого сезона, но отличается радикально большей портабильностью примеров.

Все примеры должны работать на зоопарке плат - не только Omdazz, но и куче других (не только с FPGA от Intel/Altera, но и Xilinx, Gowin и Lattice). При первом запуске скрипта он спрашивает, какую плату вы используете, после чего вы просто работаете в независимом от платы модуле top.sv, который в свою очередь инстанциируется в board_specific_wrapper.sv (в который вам как правило заглядывать не нужно). Работать вы можете как со скриптами, так и с GUI.

Недостаток: из-за того, что все модули сразу параметризованы, материал будет менее доступен для школьников, кроме самых способных. Но для студентов, которые уже умеют программировать, это не должно быть проблемой.

-

Задачки на знание языка SystemVerilog и алгоритма работы симулятора. Эти задачки будут выставлены в репозитории systemverilog-homework в течение августа и будут базироваться на задачах предыдущих лет, например из бишкекского репозитория.

-

Задачки на микроархитектуру: конвейеры, арбитры, контроль потока данных, очереди FIFO, пересечение тактового домена - без знания всего этого пройти интервью на RTL Design позицию в крупные электронные компании невозможно. Одновременно вводятся элементы верификации, без которых невозможно пройти интервью на и Design Verification позицию. Эти задачи находятся в репозитории valid-ready-etc которые сейчас обновляется, будет готов к сентябрю.

Помимо этих трех репозиториев будут репозитории из МИЭТ с их собственными процессорными ядрами. МИЭТ на них делал например хакатон по изменению конвейера процессора.

Часть III. Проверка работы с FPGA платой

Что же делать после загрузки SSD? Стоит проверить как он работает с вашей платой. Тут есть момент - в момент подключения платы к компьютеру - Линукс может накрыться медным тазом (к счастью не перманентно, только до перезагрузки). Это особенно касается плат типа Omdazz и Saylinx, у которых два USB шнура - один для питания, другой для программатора (USB Blaster II). Особенно часто это происходит, если все (загрузочный SSD, плата, клавиатура, мышка) - подключены через общий USB hub, у которого еще и нет дополнительного питания.

Глюк по-видимому происходит из-за скачка питания, но может быть и что-то связанное с SATA-USB адаптером. Это лечится разными способами: использованием разных USB портов, использованием хаба с дополнительным питанием, подключение шнура питания к другому компьютеру. В любом случае подключение всего лучше делать при выключенном компьютере. Хотя в современном Линуксе надежная файловая система с защитой против разных сценариев, но я не знаю, что может случиться при сбое посреди какой-нибудь операции.

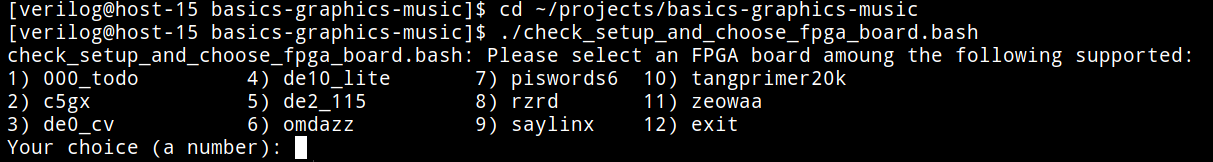

Но пора что-нибудь запустить. Для начала скажем компьютеру, какая у нас плата. Для этого мы запустим скрипт check_setup_and_choose_fpga_board.bash:

cd ~/projects/basics-graphics-music

./check_setup_and_choose_fpga_board.bashСкрипт выведет список поддерживаемых плат и спросит, какую из них вы хотите использовать. Выберем номер 6, плату Omdazz:

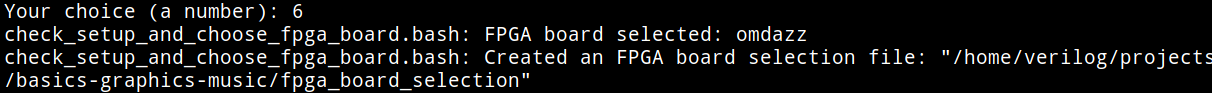

Скрипт сообщит имя выбранной платы и сохранит ваш выбор в текстовом файле в верхней директории репозитории:

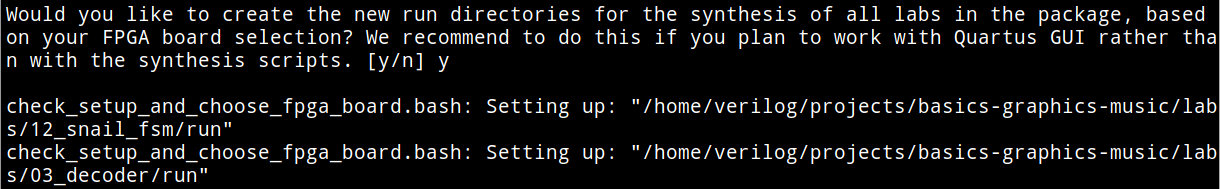

Далее скрипт задаст вопрос, хотите ли вы, чтобы он создал временные рабочие директории для всех примеров репозитория на основе вашего выбора платы. Если не любите скрипты и собираетесь далее работать только с графическим интерфейсом программы синтеза Quartus, ответьте Y ("Да"). Если же вы собираетесь далее использовать скрипты - все равно как отвечать.

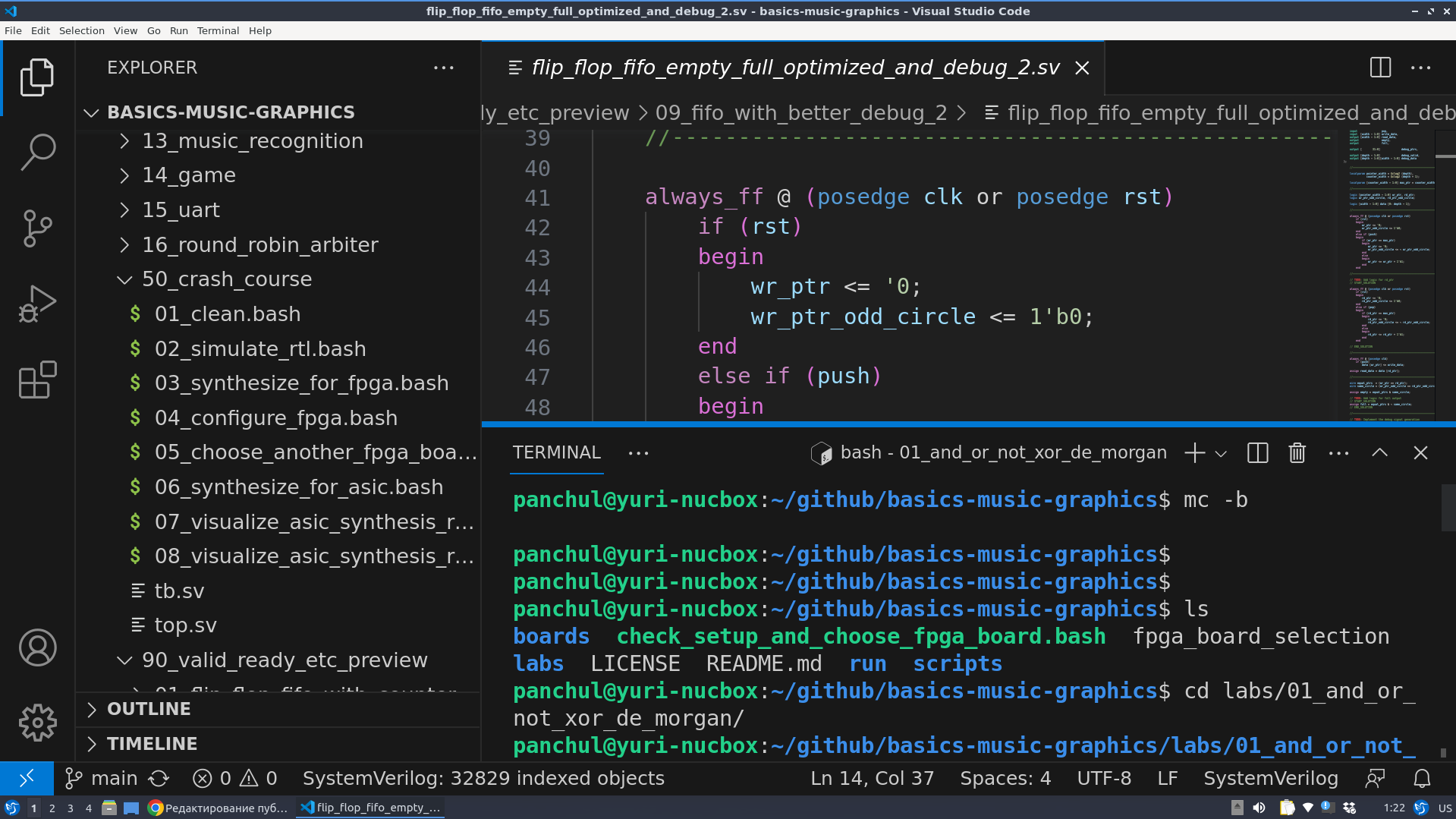

Теперь заходим в поддиректорию labs/01_and_or_not_xor_de_morgan и видим там скрипты для каждого шага работы с примером. Запустим скрипт 03_synthesize_for_fpga.bash для синтеза с выбранной FPGA платой.

cd labs/01_and_or_not_xor_de_morgan

./03_synthesize_for_fpga.bashОно должно синтезировать код примера на верилоге и прошить память конфигурации FPGA.

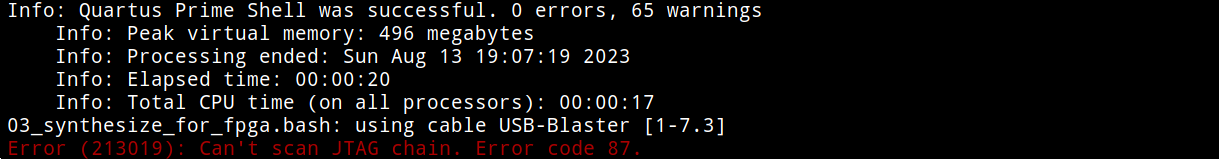

Иногда оно не прошивает с первого раза. Выглядит это так:

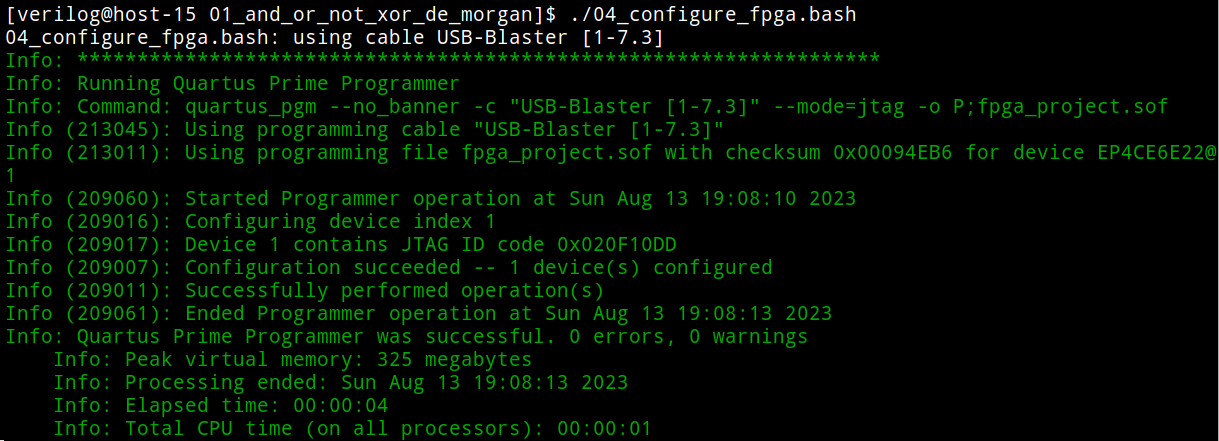

Тогда нужно выткнуть и воткнуть USB шнур в USB Blaster, после чего запустить скрипт ./04_configure_fpga.bash. Скорее всего все получится, если выбрана правильная плата:

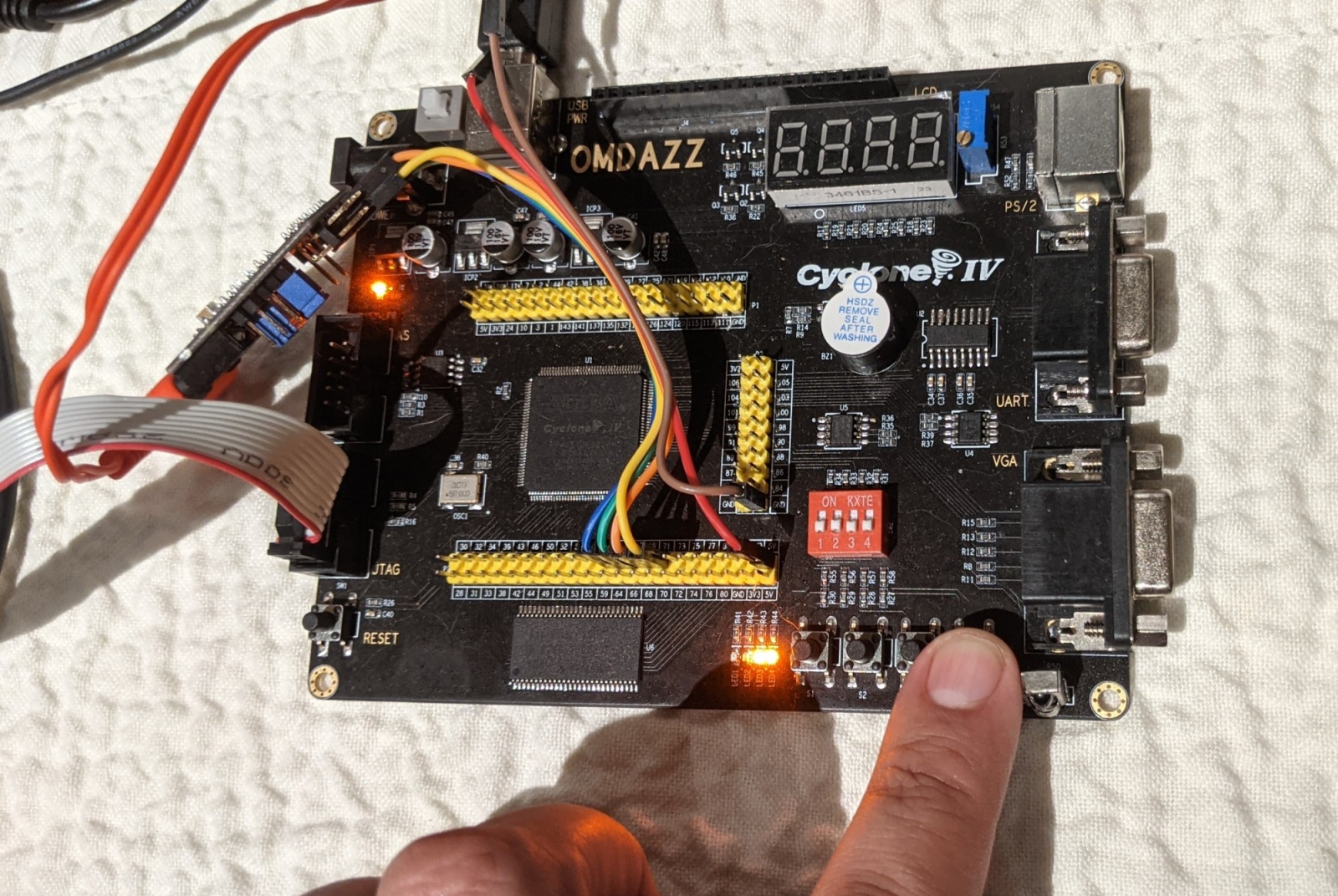

Теперь вы можете понажимать кнопки на плате и посмотреть на изменение светодиодов, в соотвествии с кодом на верилоге:

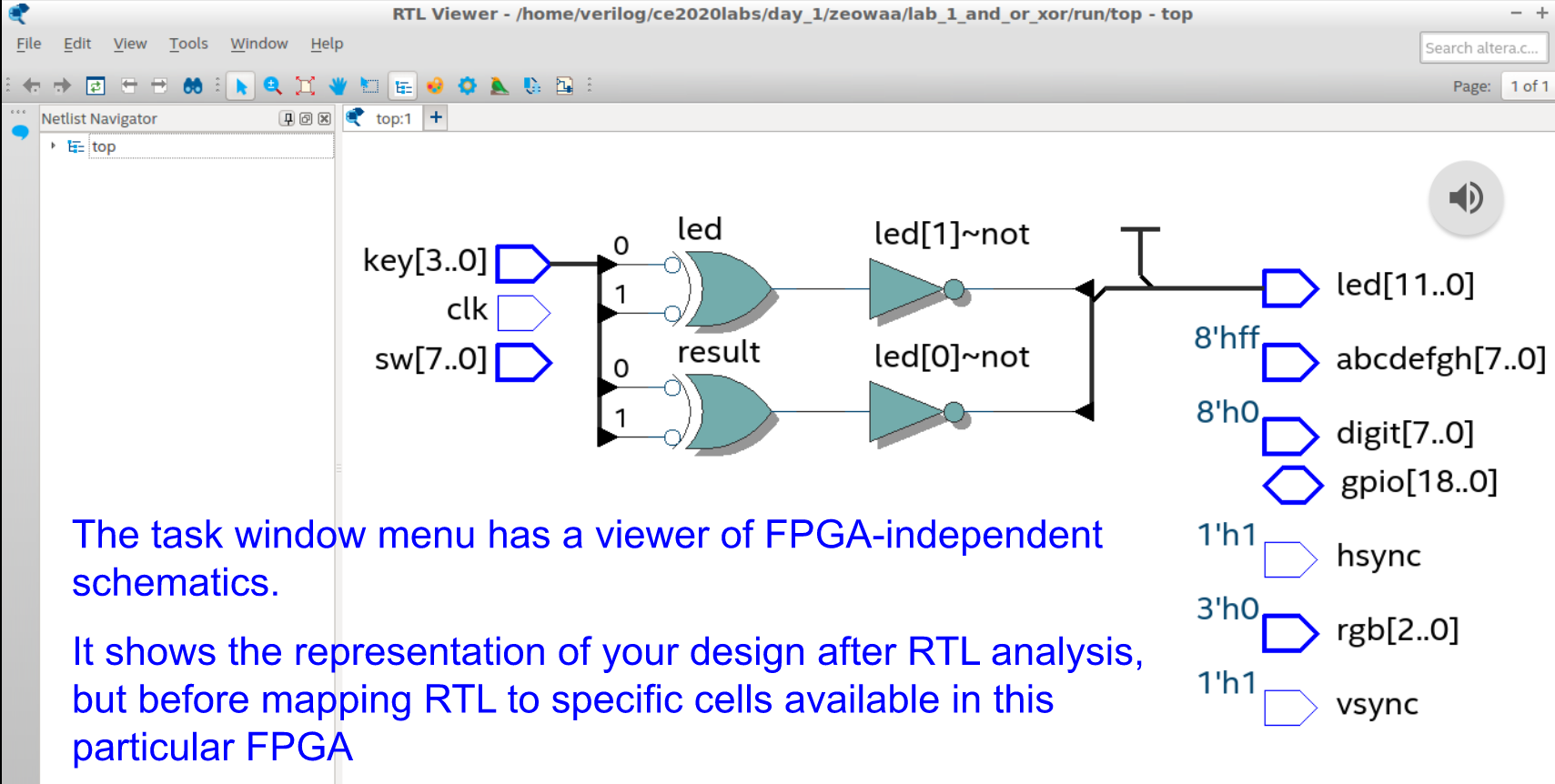

Синтез, редактирование исходников и прошивку схемы в FPGA можно также делать в GUI. Я описал как это делать в слайдах для Иннополиса, Бишкека и Тбилиси. Также вам об этом расскажут преподаватели Школы Синтеза Цифровых Схем. В этом посте только замечу, что в GUI есть отличный RTL Viewer, который покажет вам, во что превращается ваш код на верилоге:

Будем считать, что вы проверили, что SSD и ваша плата вместе работают. Для законченности картины стоило было бы еще спаять и подсоединить микрофон, усилитель и VGA монитор, а также купить блокфлейту и попробовать упражнения с распознаванием и генерацией звука и графики. Вот как это выглядело в Тбилиси на конференции LaLambda:

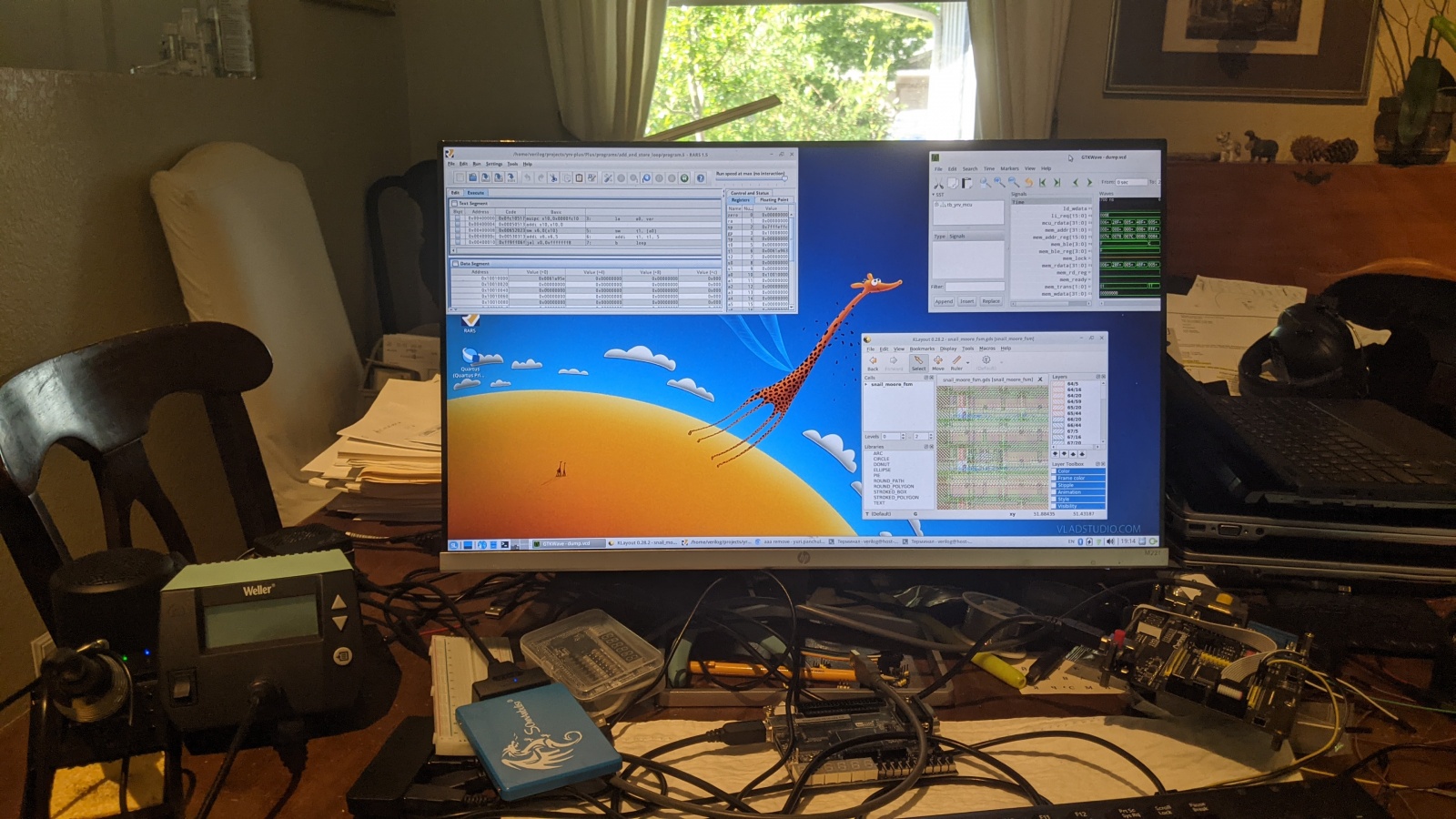

В дополнение к этому посту вы можете просмотреть мою сессию по использованию загружаемого SSD с Борисом Краснянским в реале, который работает над портированием плат: 1, 2, 3, 4.

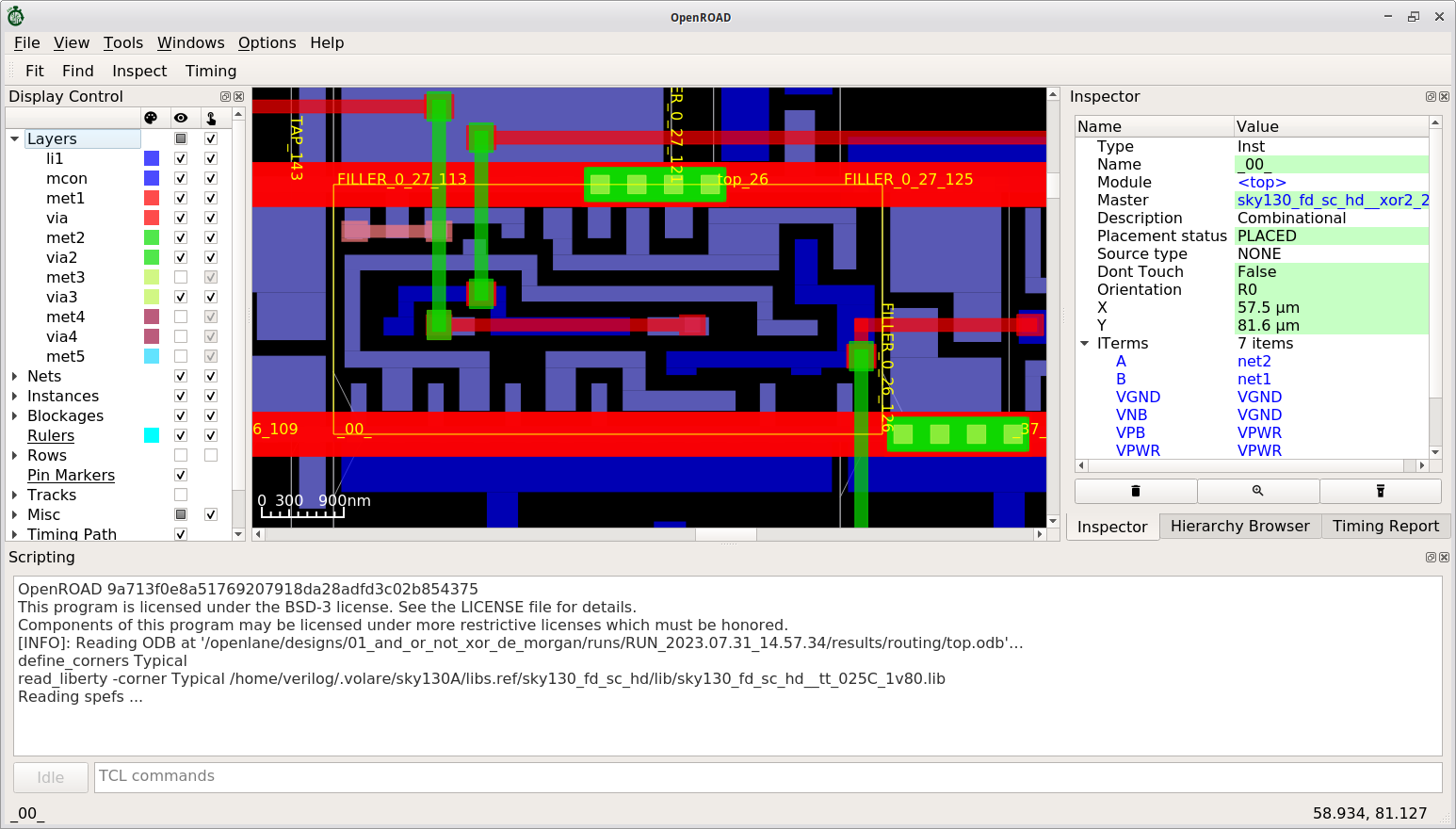

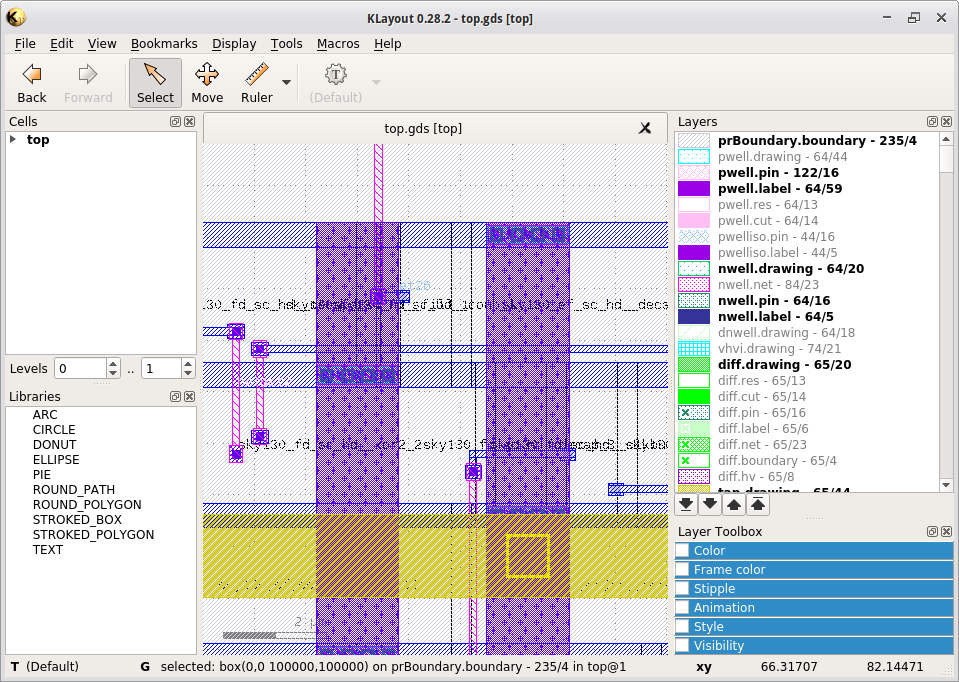

Часть IV. Синтез для ASIC

В новом сезоне Школы Синтеза мы решили ввести синтез для ASIC рано. Потому что мы выращиваем не только FPGA, но и ASIC дизайнеров. Нам нужно познакомить будущих создателей CPU, GPU, ускорителей ML и чипов для магистральных маршрутизаторов - c маршрутом RTL-to-GDSII, библиотеками стандартных ячеек (ASIC standard cells) и как выглядят отчеты по статическому анализу тайминга для ASIC. Поэтому мы включили в загружаемый SSD пакет открытых средств проектирования для ASIC софтвер под названием Open Lane.

Open Lane - это довольно большая коллекция тулов, которая работает под Docker. Но для начального ознакомления мы свели его к трем скриптам:

-

06_synthesize_for_asic.bash

-

07_visualize_asic_synthesis_results_1.bash

-

08_visualize_asic_synthesis_results_2.bash

Скрипты работают (далеко) не для всех примеров, но мы работаем над тем, чтобы все примеры для FPGA также синтезировались для ASIC.

Первый скрипт, 06_synthesize_for_asic.bash, запускает все 42 шага синтеза, размещения и трассировки, после чего извлекает из моря информации ключевые отчеты:

asic_01_main.log

asic_02_synthesis.v

asic_03_placement.nl.v

asic_04_routing.nl.v

asic_05_final_no_power_grid.nl.v

asic_06_final.v

asic_07_static_timing_analysis.sta.max.rpt

asic_08_static_timing_analysis.sta.min.rpt

asic_09_static_timing_analysis.sta.power.rpt

asic_10_library_exchange_format.lef

asic_11_magic.mag

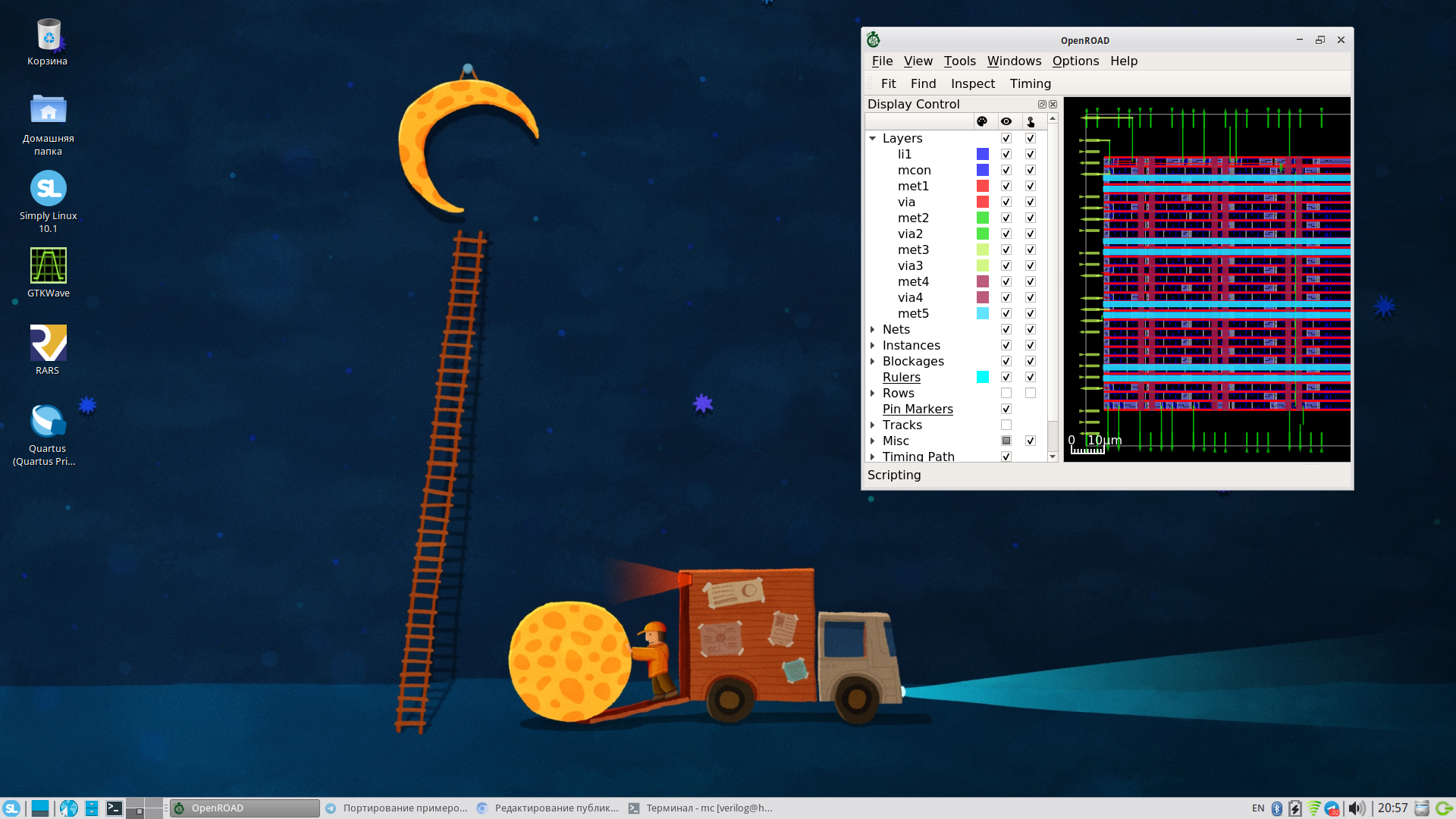

asic_12_standard_delay_format.sdfВторой скрипт, 07_visualize_asic_synthesis_results_1.bash, запускает GUI на питоне, которое показывает что получилось в виде файла в формате GDSII - слоев и геометрических фигур. Этот файл отправляется на фабрику, чтобы на его основе сделать маски и выпечь микросхемы:

Третий скрипт, 08_visualize_asic_synthesis_results_2.bash, показывает то же самое с помощью редактора klayout. Не волнуйтесь, мы не будем заставлять учеников редактировать GDSII файл. Вообще на таком низком уровне процессор проектировали только титаны типа Федерико Фаджина, который задизайнил первый в истории микропроцессор Intel 4004.

Часть V. Пара мелких моментов

1. Размер партиции у SSD

Приготовленный нами в кооперации с Базальтом имидж SSD занимает примерно ~20 GB в упакованном виде и ~50 GB в распакованном. Когда вы грузитесь с него в первый раз, то вы увидите, что на диске всего ~50 GB пространства, бОльшая часть которого уже занята. Однако когда вы загрузитесь второй раз, партиция будет растянута на все имеющееся у вас пространство SDD: 120 GB, 128 GB, 240 GB, 480 GB итд.

2. Visual Studio Code

В последнее время все больше разработчиков используют среду VS Code, в том числе под Линуксом. VS Code. Я забыл попросить Антона Мидюкова из Базальт СПО поставить VS Code, потому что привык что люди используют vim, emacs или встроенный редактор в Midnight Commander.

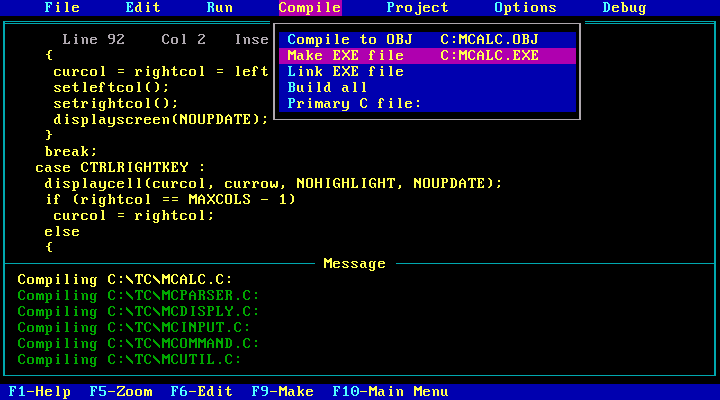

Лично я использую редактор joe, который является клоном (сейчас вы угадаете мой возраст) редактора в TurboC 1.5, но с квадратными блоками, шаблонами и другими улучшениями. К квадратным блокам (которые кстати реализованы криво в современном редакторе Sublime Text 3) я привык в лучшем редакторе начала 1990-х - MultiEdit.

Но к популярности VS Code среди молодежи я отношусь нормально. Преподаватели МИЭТ его тоже рекомендуют, так как у него низкий порог входа, есть дерево файлов слева и можно включить консоль снизу.

Как установить VS Code на Simply Linux расписано на сайте altlinux.org. Также у VS Code есть есть куча плагинов (extension), в том числе для SystemVerilog. Мне зашел вот этот:

Часть VI. Как приготовить загружаемый SSD

Прежде всего вам нужно связаться с организатором Школы Синтеза Цифровых Схем Александром Биленко (a.bilenko@yadro.com) и получить от него ссылку для скачивания имиджа. В принципе, на этом инструкцию можно было бы закончить и сказать "ну и используете dd или там dcfldd", но не все так просто. Из-за проблемы, которая называется "хвост GPT" (не путать с ChatGPT).

GPT - это Global Partition Table. Оказывается этих таблиц на диске две - основная и резервная. Я уже упоминал, что файл имиджа (~50 GB в распакованном виде) меньше чем размер любого SSD (который сейчас начинается с 120 GB и даже 5 лет назад начинался с 60 GB). Поэтому если на SSD есть две GPT, то после записи имиджа резервная таблица не будет переписана. Она будет там лежать и мешать загрузке.

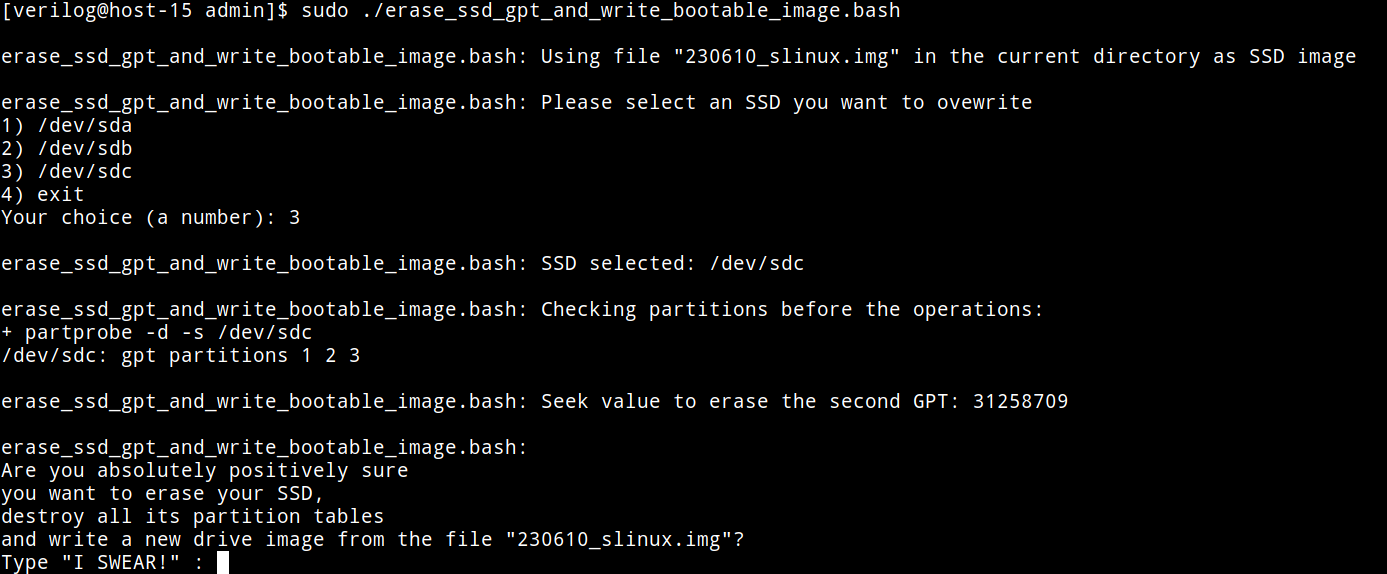

Такой проблемы нет, если диск размечен без GPT, со старыми DOS Partitions. Но для гарантии вторую GPT нужно стереть. Именно это и делает скрипт erase_ssd_gpt_and_write_bootable_image.bash , который находится в директории /home/verilog/projects/basics-graphics-music/scripts/admin.

Этот скрипт нужно поместить в директорию с имиджем SSD, файлом с расширением .img. Или поместить имидж в директорию со скриптом, после чего запустить, причем под sudo. Скрипт проверит, что имидж один, спросит, какой диск переписать, проверит, что этот диск не смонтирован, заставит принести клятву, что вы знаете, что вы делаете (написать "I SWEAR!"), после чего скрипт послушно запишет имидж на выбранный SSD. Операция занимает десятки минут.

На этом я свой рассказ заканчиваю и надеюсь, что читатель достаточно заинтригован, чтобы войти или продолжить свое путешествие по мирам русских Линуксов, FPGA или ASIC Design.

Автор: Юрий Панчул / Yuri Panchul