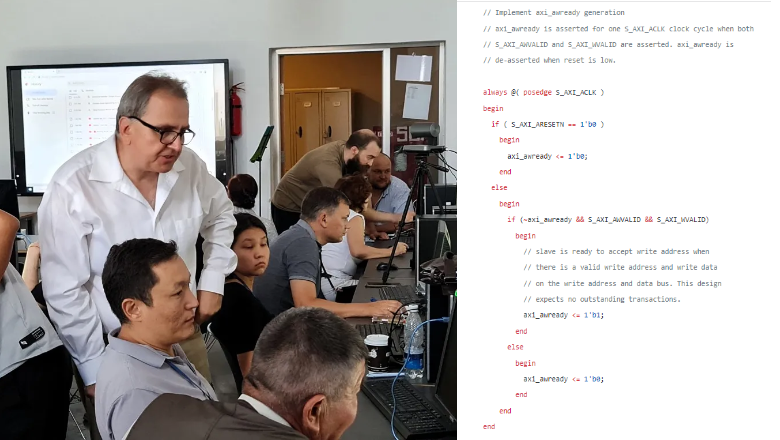

Оказывается, в Кыргызстане, который в 11 веке стоял аккурат посередине Великого шёлкового пути, спустя тысячу лет появились проектировщики цифровых схем на уровне регистровых передач. Во время семинара «Модели бизнеса и основы технологий микроэлектроники для Центральной Азии» мы встретились с инженером Азаматом Бексадаевым, который принимал участие в разработке двух блоков на верилоге для международного проекта Parallella. Этот проект был инициирован американской компанией Adapteva, которая сейчас превратилась в Zero ASIC.

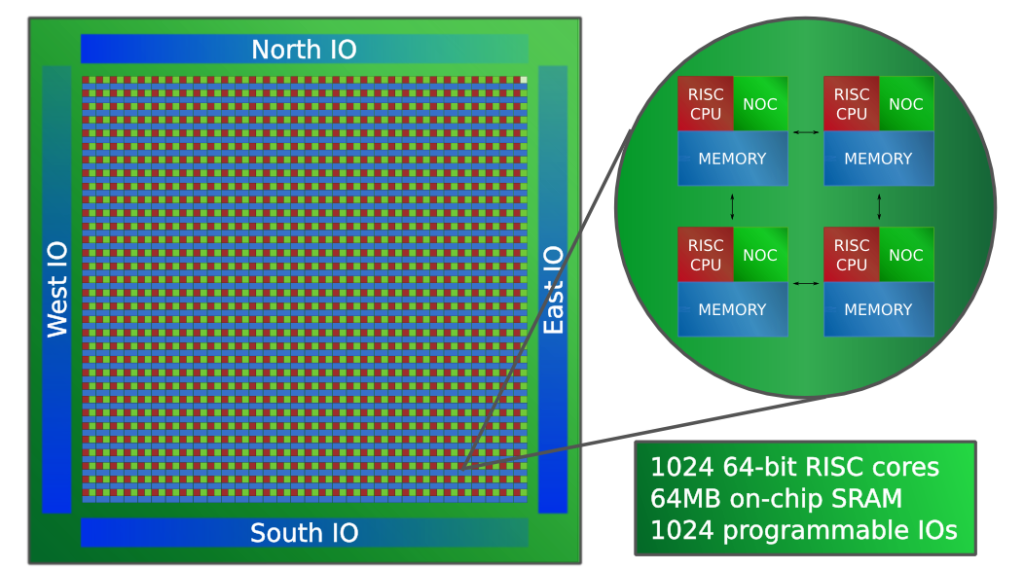

Основой технологии Adapteva была решетка из большого количества процессорных ядер внутри одной микросхемы. Ядра имели собственную архитектуру под названием Epiphany и были оптимизированы под энергоэффективные вычисления с плавающей точкой. По микроархитектуре каждое ядро было суперскаляром с внеочередными выполнением инструкций (out-of-order – OoO).

Архитектура не использовала когерентные кэши, вместо это в ней было разделённое глобальное адресное пространство, с локальными памятями при каждом ядре. При этом, всю конструкцию можно было программировать на Си, хотя программисту стоило понимать, что он делает. Инструкции и стек выполнения для каждого ядра должны были находиться в локальной памяти, но вот данные могли быть в разных местах: локально, в памяти других ядер, или вообще во внешней памяти вне чипа. Скорость доступа разумеется зависела от местанахождения данных.

Целью технологии было построить своего рода встроенный суперкомпьютер, в котором помимо решетки из 1024 ядер на чипе – можно было бы строить еще и решетку следущего уровня, из многих таких чипов, вплоть до миллиарда ядер. Adapteva выпустила несколько чипов на TSMC, в том числе чип на 16 нанометров в 2016 году. Деньги в проекте были от кикстартера, венчурных капиталистов и американских военных. Adapteva также вероятно пыталась продать компании Ericcson идею использовать Epiphany для распознавания речи и лиц в сотовых телефонах, судя по упоминанию Эриксона и раcпознавания в разных материалах (1, 2).

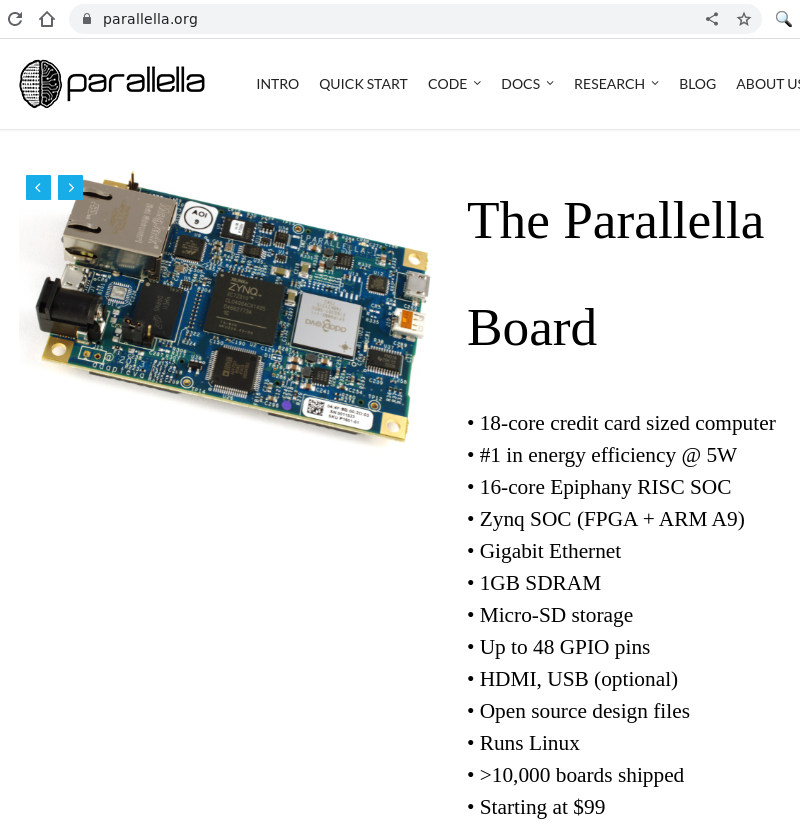

Плата Parallella, которую Adapteva пробовала раскрутить через Kickstarter для энтузиастов новых технологий вычислений, включала не только чип с ранней версией решетки процессоров Epiphany, но и более мейнстримный чип Xilinx Zynq, а также другие компоненты, в том числе порт Ethernet. Чип Zynq, с которым в основном работал Азамат Бексадаев, представляет из себя комбинацию из двухядерного процессора ARM Cortex A9 – c матрицей из ячеек реконфигурируемой логики – Field-Programmable Gate Array – FPGA, которые по-русски принято называть Программируемые Логические Интегральные Схемы – ПЛИС.

Хотя ПЛИС работают как правило на более низкой частоте, чем ASIC (фиксированные микросхемы, Application-Specific Integrated Circuits), а также требуют больше ресурсов (площади на кристалле, электроэнергии), ПЛИС из-за их возможности меняться на лету широко применяют для обучения проектировщиков микросхем, для прототипорования ASIC-ов и для некоторых малосерийных изделий. Пара слов о сущности ПЛИС из другой моей заметки на Хабре:

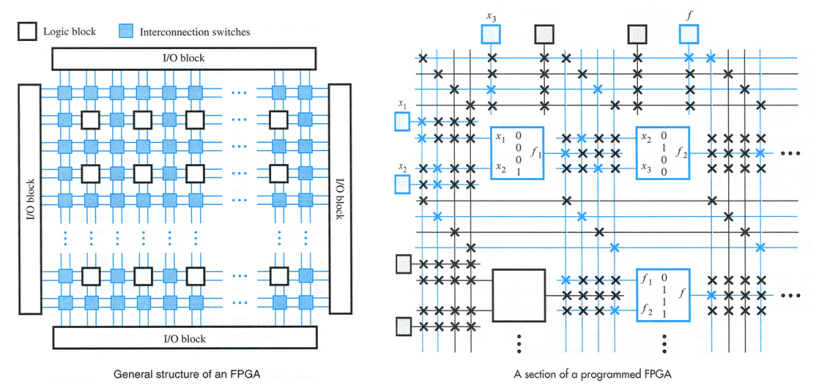

В самом простом варианте FPGA состоит из матрицы однородных ячеек, в функцию каждой из которых можно поменять с помощью мультиплексоров, подсоединенных к битам конфигурационной памяти. Одна ячейка может стать гейтом AND с четырьмя вводами и одним выводом, другая — однобитным регистром и т.д. Загружаем в конфигурационную память последовательность битов из памяти — и в FPGA образуется заданная электронная схема, которая может быть процессором, контроллером дисплея и т.д.

ПЛИС-ы / FPGA — не процессоры, «программируя» ПЛИС (заполняя конфигурационную память ПЛИС-а) вы создаете электронную схему (хардвер), в то время как при программировании процессора (фиксированного хардвера) вы подсовываете ему цепочку написанных в память последовательных инструкций программы (софтвер).

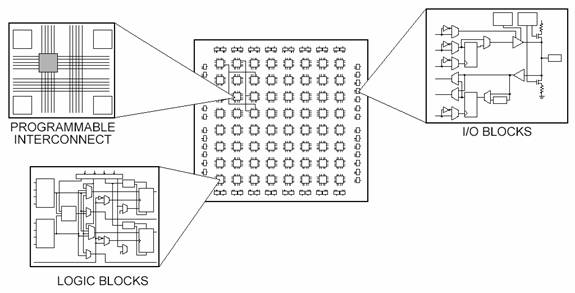

Внизу — схема простейшего блока FPGA, в который входит look-up table (LUT) и flip-flop. Правда в этой схеме не показаны мультиплексоры, которые меняют функцию ячейки, и соединения с конфигурационной памятью.

Диаграммы, иллюстрирующие структуру FPGA:

И еще одна:

Какую же именно схему реализовывал Азамат Бексадаев на Zynq FPGA а проекте Parallella? Два блока, которые Азамат описал в своем профайле на LinkedIn: контроллер флеш-карты памяти и аппаратный grep, обработка текста хардвером. Я тоже когда-то писал про обработку текста схемой без процессора в заметке “Как делать парсинг текста голым хардвером, без процессора и без софтвера”, но у Азамата задача горадо более сложная. Вот репозиторий проекта на GitHub и детали из линкдина Азамата:

-

Redesigned SD/eMMC Host Controller (HC) from “Wishbone” interface into the “AMBA AXI” interface and written key features for this Controller:

-

Extended data bus from 1 bit to 8 bit,

-

Written module Single Operation DMA (SDMA),

-

Upgraded SDMA to Advanced DMA (ADMA),

-

Written AutoCMD23 feature to optimise CMD exchange flow between Card and HC,

-

Controller was upgraded to work in High Speed mode. This mode allow read/write data in 50MHZ,

-

Implemented supporting of Dual Data Rate (DDR) mode, which is doubled the speed data transferring.

All these implemented upgrades and features speeded up the Host Controller from 14MB/s to 97MB/s. Some of features were carried out together with the changes of kernel SDHCI host driver.

-

-

Developed Pattern searching engine on FPGA with Regular Expression. Meta-characters compatible with POSIX standard. (Analogue of “grep”):

-

Participated in building and testing of subset construction algorithm that searches of patterns for some of the regexp meta characters.

-

Responsibility:

-

Develop RTL design on Xilinix ZYNQ 7020 SoC using Verilog HDL. Development kit – ZedBoard, Target board is Parallella.

-

Integrate Design with Linux driver.

-

Testing and debugging the each steps of the projects.

-

Measure electrical utilization. Comparing and analyzing metric results.

-

Writing documentation.

-

Competence in Agile Scrum methodology. Daily Scrum, Sprint planing, Backlog grooming, Sprint retrospectives.

Какова же мораль всей этой истории? В Кыргизстане есть инженеры, которые умеют писать профессиональный код на языках описания аппаратуры, получают это умение в местных вузах (в кыргызском политехе есть курс по VHDL с лабами на FPGA) и развивают это умение с помощью участия в open-source проектах. Такое наблюдение поддерживает идею, ради которой собственно и был организован семинар в Бишкеке: в Средней Азии можно, с относительно низкого старта, развить экосистему проектирования микроэлектронных чипов, используя оставшиеся от советского периода традиции образования, в комбинации с поддержкой местных бизнесменов и международных технологических компаний.

Кстати, пока я смотрел на фрагмент кода Азамата, который я вынес в заголовок (фрагмент генерирует сигнал AWREADY протокола AXI), я осознал, что этот дизайн можно сделать более эффективным. Кто из читателей первым скажет как именно? Вот исходники. Подсказка: про это написано в свежей редакции стандарта AXI.

Материалы самого семинара (код, фото и видео) вы можете скачать и посмотреть на сайте Digital Design & Verification in Central Asia.

Автор: Юрий Панчул / Yuri Panchul