Проектированием простого процессора сейчас никого не удивишь. Любой способный студент может за пару недель написать на верилоге однотактный RISC-V или ARM процессор и синтезировать его для ПЛИС. Процессор будет работать на учебной плате и выполнять простые программы на Си и ассемблере.

Такой процессор можно постепенно усложнять: сделать его конвейерным, добавить кэш и прерывания. Но где находится граница между такими студенческими упражнениями - и взрослыми высокопроизводительными процессорными ядрами, которые стоят в сотовых телефонах и облачных серверах?

На границе между вводным и продвинутым курсом микроархитектуры CPU принято ставить внеочередное выполнение инструкций (out-of-order execution), именно оно отделяет мальчика от мужа. Эта фича впервые появилась еще в 1960-е годы в суперкомпьютерах CDC 6600 и IBM 360/91, но проникла в персоналки с PentiumPro только в 1996 году и в Apple iPhone в 2012 году.

Именно внеочередное выполнение инструкций - главная козырная карта самого горячего процессорного проекта российской микроэлектроники - двухгигагерцового RISC-V процессора для ноутбуков от компании Ядро / Syntacore. Этот проект был объявлен в прошлом году. Что с ним станет в результате известных событий?

Прежде чем обсудить что может делать Syntacore (оставим этот вопрос на сладкое), поговорим об истории out-of-order.

Первым «настоящим» суперкомпьютером и первым процессором с внеочередным исполнением инструкций принято считать CDC 6600. Этот компьютер выпускался с 1964 года. Первые экземпляры CDC 6600 купили лаборатории в Ливерморе и Лос-Аламосе. Они использовалось для сохранения мирного неба над головой, то бишь для моделирования ядерного оружия. (Вот где истоки процессоров в айфонах, ага) Потом CDC 6600 пошли и в мирный атом (CERN, Lawrence Radiation Lab) и студентам в университеты. Всего было выпущено около 100 машин:

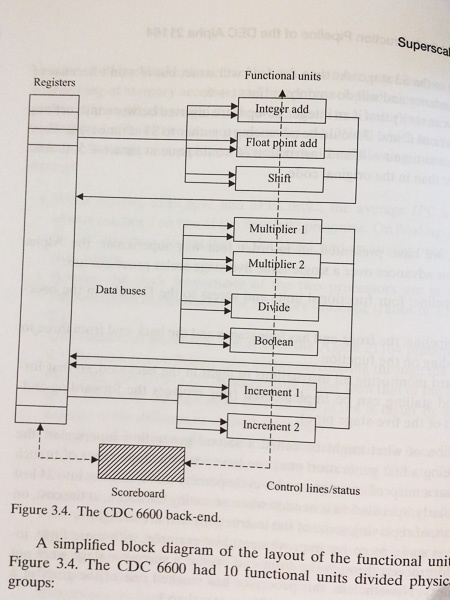

Внутри процессора CDC 6600 было несколько функциональных устройств, которые работали параллельно: два устройства сложения (целочисленное и с плавающей точкой), два устройства умножения, устройство деления, блок логических операций, блок сдвига и два блока прибавления константы.

Внеочередное выполнение иструкций в CDC 6600 было сделано с помощью аппаратной структуры под названием scoreboard, типа "учетная доска" или "табло". "Табло" хранила информацию, какие из функциональных устройств не заняты, из каких регистров занятые устройства получают операнды, в какие регистры пишут результаты. А также готово ли значение каждого операнда, или функциональному устройству нужно ждать, пока другое устройство не запишет в регистр операнда результат более ранней операции.

Если вы хотите написать реализацию упрощенного CDC 6600 на верилоге и FPGA в качестве студенческого курсового проекта, вы можете посмотреть детали например в слайдах по CDC 6600 из Беркли.

Что же давала такая структура? Допустим у вас есть программа:

A = B * C

D = E / F

G = H * I

J = K + L

и допустим умножение и деление требует несколько тактов для выполнения. С помощью использования параллельных функциональных устройств и табло можно было запускать каждую инструкцию, не дожидаясь окончания предыдущих. Замедления возникали только при зависимостях между инструкциями (деление ждет результата умножения - A):

A = B * C

D = A / F

или если функциональных устройств не хватало (три деления при одном функциональном устройстве деления):

A = B / C

D = E / F

G = H / I

Однако у такого табло есть недостаток - оно не очень хорошо работает, если нужно переиспользовать какой-нибудь регистр для нового вычисления:

A = B * C

D = A / F

A = H * I

J = A + L

В этой последовательности возникает так называемая "антизависимость" - мы не можем начинать умножение в третьей строке перед завершением деления во второй, чтобы не "запачкать" случайно операнд умножения. Для решения такой проблемы внутри процессора заводится больше регистров чем видит программист (программист видит только так называемые "архитектурные регистры"), после чего процессор аппаратно заменяет доступы к регистрам, так что программа ведет себя так, как будто программист написал:

A = B * C

D = A / F

M = H * I

J = M + L

A = M

то есть вторая инструкция не задерживает третью, а пятое действие выполняется параллельно с четвертым. Они теперь могут вообще выполняться так:

Параллельно A = B * C; M = H * I (вспомним что у нас два устройства умножения в CDC 6600)

Параллельно D = A / F; J = M + L

A = M

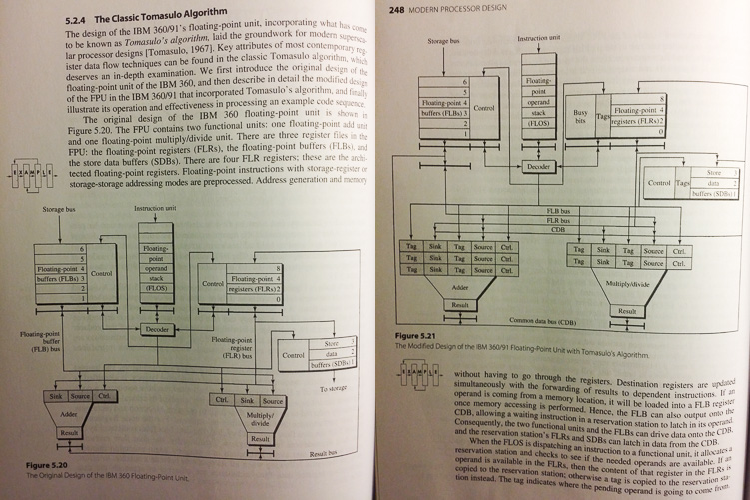

Аппаратную структуру, которая выполняет такой трюк, изобрел инженер по имени Роберт Томасуло в 1967 году. В одной из самых полезных современных книжек по разработке процессоров, Modern Processor Design: Fundamentals of Superscalar Processors by John Paul Shen and Mikko H. Lipasti (2013), наглядно показано, как выглядел блок операций с плавающей точкой у IBM 360/91 до улучшения Томасуло и после него:

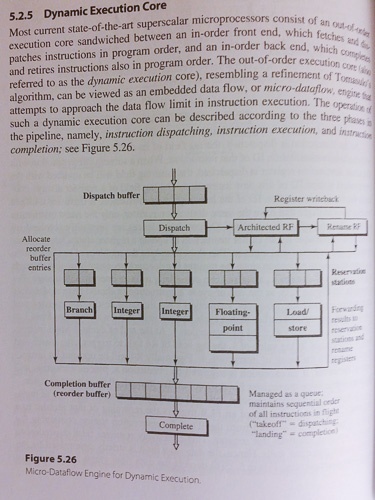

После описания классического Томасуло книжка Шен-Липасти описывает как делается планирование операций и переименование регистров в современных процессорах с динамическим конвейером. Динамический конвейер (в отличие от более простого статического) - это базовая идея и современных CISC процессоров в серверах, и высокопроизводительных RISC процессоров в смартфонах. После долгих споров на тему RISC/CISC в 1980-е годы в микроархитектуре по крайней мере высокопроизводительных машин произошла конвергенция:

Тут есть интересный момент - некоторые люди не понимают разницы между архитектурой и микроархитектурой. Возмем уже упоминавшийся российский проект суперскалярного RISC-V процессора для линуксных ноутбуков с частотой 2 гигагерца. От компании Syntacore - отделения российской же компании Yadro. Если бы проект завершился, то Россия могла бы избавится от зависимости не только от Интела и AMD, но и от лицензионных ARM ядер, и при этом иметь приличные компьютеры для школ и госсектора - низкопотребляющие и не тормознутые.

Вот статья за июль 2021 года под названием "Разработчики «железа» для «закона Яровой» создают российский процессор за десятки миллиардов рублей". В ней есть такой абзац:

Планы «Ростеха» и Yadro нереальны?

Архитектуры процессоров, которые сегодня есть на рынке, существуют 30–40 лет, над ними работали поколения разработчиков, в них вложено много ресурсов и денег, отметил в разговоре с «Ведомостями» директор Консорциума отечественных разработчиков систем хранения данных Олег Изумрудов.

«Они давно применяются для серьезных вычислений и ответственных задач. На этом фоне странно делать ставку на молодую, недоработанную архитектуру, – полагает он. – Заявленные в проекте характеристики недостижимы в перспективе десятилетий. Например, обещанная тактовая частота процессора значительно выше достижимой сейчас в RISC-V. Существующие сегодня процессоры этой архитектуры работают на частоте 450 МГц. Сейчас заявленные отечественными разработчиками показатели на практике не реализуемы».

Товарищ Изумрудов путает архитектуру (систему команд процессора - вид процессора для программиста) и микроархитектуру (аппаратную структуру конвейера). Современные x86 и ARM ядра такие шустрые по сравнению с готовыми чипами с RISC-V ядрами не потому, что RISC-V - сыроватая архитектура, а потому, что большинство RISC-V ядер сделаны с простым статическим конвейером.

Если суровые математически мыслящие микроархитекторы придумают высокопроизводительный динамический конвейер, поставят продвинутый предсказатель переходов TAGE, сделают эффективные многоядерные кластеры с когерентными кэшами, то можно сделать RISC-V ядро ничуть не хуже чем ядро с архитектурой ARM в Apple M1. Архитектура RISC-V это не запрещает (она не хуже чем ARM) - только неразвитая микроархитектура. И речь идет конечно-же не о 30-40 годах, а всего нескольких.

"Но..." - спросит читатель - "а как же известные события и отказ TSMC работать с российким рынком?" Да, мы все в курсе, что российские процессоры больше на тайваньском TSMC делать нельзя. И даже на фабрике SMIC в КНР тоже нельзя, так как США им строго-настрого запретило обслуживать русских, а рычаги у США есть.

Но ведь никто же не запретил российким компаниями продавать лицензии на свой код на верилоге тем же китайским или индийским компаниям, не так ли? Вполне себе бизнес модель. Называется Semiconductor IP - Полупроводниковая Интеллектуальная Собственность.

Для этого не нужно тратить 20 миллиардов долларов на современный фаб. Можно сидеть в заснеженной избушке в Сибири, рисовать карандашом микроархитектурные диаграммы, потом отлаживать код на верилоге на бесплатном симуляторе, запускать подкрученный open-source tool Yosys / OpenLANE для оценки статического тайминга. Купить ПЛИС Gowin из КНР вместо IntelFPGA или Xilinx для прототипирования.

И продавать можно не только китайцам. Вы знаете, что помимо TSMC есть например GlobalFoundries c техпроцессом 12 нанометров, которую контролирует фонд города Абу-Даби, столицы Объединенных Арабских Эмиратов? Может в Эмиратах тоже хотят проектировать и производить чипы? Если сделать российский процессор с хорошим динамическим конвейером, лучше чем у SiFive и других вендоров, то почему бы эмиратцам и не купить лицензию? На код на верилоге?

Я был в Абу-Даби как турист, там очень мило, хотя и жарко:

И вот тут возникает главный вопрос! А есть ли в России достаточно квалифицированных кадров для проектирования и верификации всех блоков и фич продвинутого процессорного Semiconductor IP? Предсказателей переходов и тестов для них, аналитиков производительности динамического конвейера, математиков оптимизирующих библиотеки для векторных расширений? Чтобы победить всех конкурентов из Америки, Великобритании и Азии?

В России даже RTL-дизайнеров не так много, и с верификаторами на SystemVerilog совсем дефицит. Но это не значит, что их нельзя вырастить. Короче, в эту субботу, 19 марта, c 12.00 до 15.00 в зеленоградском МИЭТ (Московский Институт Электронной Техники если кто не знает) пройдет занятие Сколковской Школы Синтеза Цифровых Схем:

Школа 2021/22. Занятие 16. Начала продвинутой микроархитектуры: восстановление порядка транзакций и внеочередное выполнение инструкций

Ведущие: инженеры Syntacore и МИЭТ

Если вы хотите прийти на занятие в МИЭТ в реале, напишите емейл Александру Биленко info@chipexpo.ru (это гарантирует место с компьютером и FPGA платой). Если вы не умеете работать с FPGA платами - не беда, бОльшая часть материала показывается с помощью симуляции.

Как проехать к месту проведения занятия: https://miet.ru/page/1127

ОЧЕНЬ ВАЖНО! Для прохода на территорию МИЭТ необходимо иметь при себе паспорт !!! Все желающие посетить занятие должны ДО ЧЕТВЕРГА (17 марта) включительно прислать свои данные (ФИО) на почту info@chipexpo.ru

Также желательно зарегистрироваться на сайте Школы. Зарегистрировавшиеся получат по емейлу упражнения для проверки своих знаний и умений.

Если не можете приехать - вот трансляция в Youtube, которая начнется в субботу в полдень.

Добро Пожаловать в Продвинутую Микроархитектуру CPU и Приятных Занятий!

Автор: Юрий Панчул / Yuri Panchul