Уже не первый год Wilson Research Group проводит исследование по тенденциям в сфере FPGA и ASIC. По данным исследованиям можно определить основные векторы развития и изменения, которые происходят в мире программируемой логики.

Затравка

На Хабре, да и где либо еще не так часто можно найти информацию об аналитике рынка разработки под FPGA. Не понятно что и как меняется, хотя казалось бы изменений и интереса к рынку довольно много. Люди, далекие от ПЛИС и те слышали о покупке Altera Intel'ом.

Так почему же нет никакой информации? Данный пост призван все исправить и внести порядок и ясность в ряды хардверщиков. А еще пытается закончить холивар между сторонниками Verilog/SystemVerilog и VHDL.Ура!

И еще… здесь приводятся основные тезисы по FPGA, если вам нужны по ASIC — ссылки на источники есть в футере. Если будет большой интерес — можно будет написать отдельный пост.

Начнем

Большинство участников проводимого опроса — это разработчики электроники(hardware designer), инженеры по верификации(verificarion engineer).

Исследование выявило тенденцию по увеличению количества встраиваемых процессоров в проектах ПЛИС с 2014 года(увеличилось с 56% до 59%).

Увеличение незначительное. И понятно почему. Проекты, использующие встроенные процессоры добавляют сложности к верификации из-за «хардверного» и «софтверного» взаимодействия, а также необходимости реализации сложных интерфейсов.

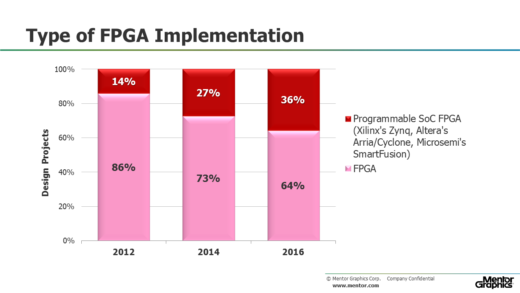

Рынок программируемых SoC FPGA, таких как ZYNQ от Xilinx, Arria/Cydone от Altera(Intel) и SmartFusion от Microsemi растет. Реализация проектов со встроенным процессором на них заметно упростилась и теперь 36% FPGA проектов релизуются именно на этих чипах.

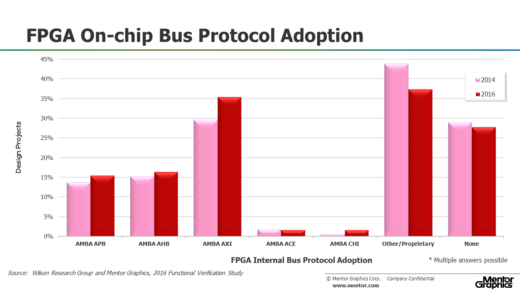

Вместе с этим растет и доля проектов, использующих стандартизированные интерфейсы на кристалле вместо проприетарных. Рост AMBA связан с тем, что в указанных выше чипах, как правило, встроенным процессором является ARM. Да и стандарт открыт.

Теперь о верификации

48% времени, потраченного на проект отводится на верификацию. Это значение растет. Так, например в 2014 году на верификацию уходило 46%, а в 2012 — 43% времени проекта.

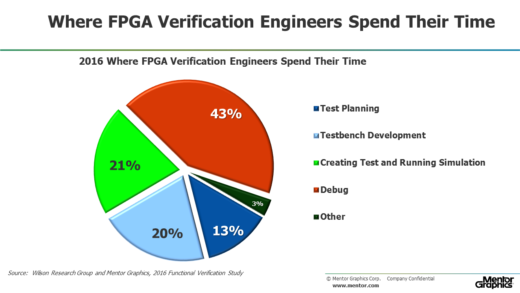

Если посмотреть на среднее время, которое инженеры по верификации тратят, выполняя различные задачи, связанные с конкретным проектом — мы увидим, что большую часть времени они тратят на нахождение и устранение ошибок. Как правило, от проекта к проекту это время значительно отличается.

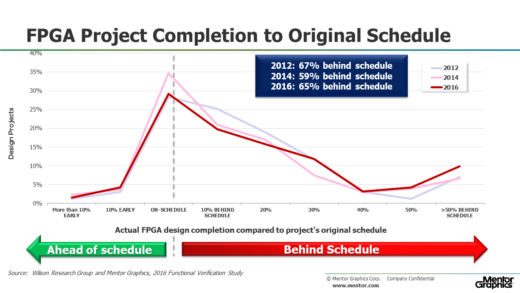

Следующие данные помогут объяснить менеджеру почему ты так долго не сдаешь проект в срок :)

Если вы выполните свой проект за срок в полтора раза превышающий запланированный — вы окажетесь далеко не исключением (примерно каждый десятый проект сдается именно так).

Во время или раньше срока сдаются лишь 35% проектов.

Как правило отставание от сроков связано с тем, что 78% проектов имеют «непростые» ошибки. Как минимум 30% проектов имеют одну ошибку и зависимость количества проектов от количество ошибок имеет вид распределения Рэлея.

Типы ошибок в FPGA проектах можно распределить по категориям от наиболее популярных к менее. Самой популярной ошибкой, требующей переработки проекта остается логическая или функциональная ошибка, затем ошибки с тактированием, в аналого-цифровых схемах, ошибки в файле прошифки для процессора и т.д.

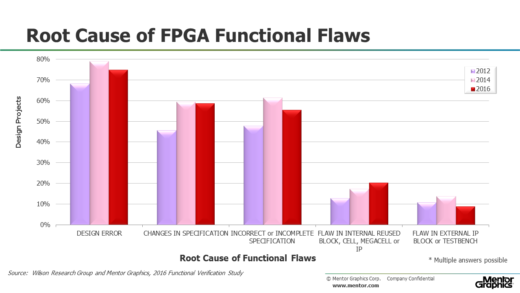

Основными причинами появлениями ошибок в логике и функциональности работы проекта являются:

1. Ошибки в дизайне, 2. Изменения в спецификации, 3. Некорректная или неполная документация, 4. Ошибки в своих или сторонних IP-блоках/тестбенчах и прочих элементах проекта

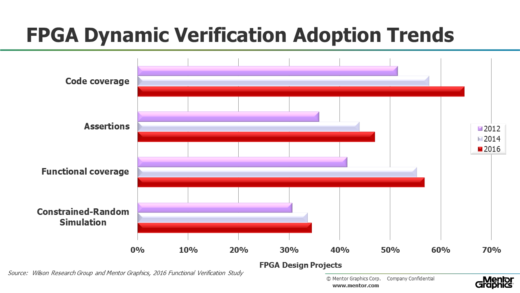

В качестве инструментов тестирования все чаще используют ассерты, функциональное и кодовое покрытие и случайно-ограниченное симулирование:

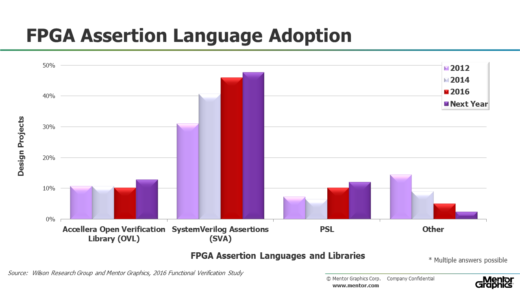

47% проектов адаптированы под верификацию ассертами как стратегия верификации кода.

HDL языки и не только

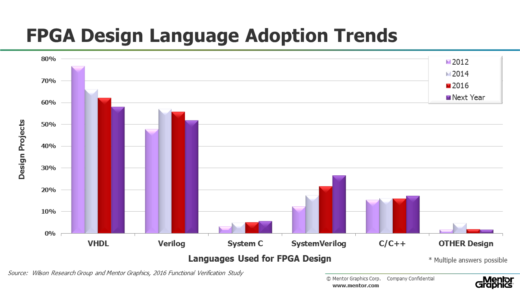

Языки, которые используют для проектирования RTL.

Здесь наблюдается снижение количества VHDL кода в проектах. И это общемировой тренд. Но это снижение в меньшей степени касается европейских разработчиков, где FPGA проекты на 79% написаны на VHDL, когда в среднем по миру этот показатель 62%.

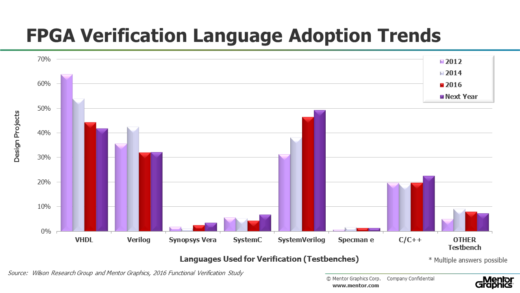

Языки, использующиеся в тестах

Здесь несомненным лидером является SystemVerilog. Но тут европейские разработчики очень сильно отличаются от остального мира. В Европе VHDL для верификации используется в 66% случаев, в то время как SystemVerilog в 41%.

Так что VHDL в некотором роде жив. Не понятно, конечно, почему именно в Европе статистика отличается от общемировой. Возможно, это связано с обучением в университетах. Хотя с другой стороны мне приходилось фрилансить и были заказы американских студентов, причем почти все они были на VHDL.

На этом все.

Надеюсь, статья была вам чем-то полезна.

Подробнее почитать можно здесь —

Источники по FPGA:

Источники по ASIC:

Автор: 6lock