Всем привет! Надеюсь, все хорошо провели праздники и готовы с новыми силами покорять высоты FPGA разработки.

Сегодня я хочу написать небольшой гайд по запуску тестбенчей на Verilog/SystemVerilog в ModelSim без использования GUI.

План будет такой:

- Добавление пути к ModelSim в PATH.

- Написание скрипта с объяснением команд.

- Запуск ModelSim с исполнением написанного скрипта.

Поехали! Чтобы начать, на руках нужно иметь следующее:

- установленный ModelSim;

- готовый проект на Verilog/SystemVerilog;

- готовый тестбенч на Verilog/SystemVerilog;

В качестве примера будем рассматривать проект HappyNY

Итак, приступим.

1. Добавление пути к исполняемому файлу modelsim в PATH

Проверить, нужно ли это делать, можно легко: наберите в командной строке modelsim, если после этого запустится ModelSim, значит, текущий пункт можно пропустить. В противном случае, для Windows это делается следующим образом: открывается командная строка и пишется команда

set PATH=%PATH%; C:ProgsModelSim10_5win64в которой указан путь к исполняемому файлу modelsim (после; вам нужно указать свой путь к исполняемому файлу). После выполнения команды проведите проверку, указанную в начале этого пункта, если что-то не так, то повторите пункт.

2. Написание скрипта для запуска

ModelSim имеет командую строку, в которой вы может набирать разнообразные команды для запуска и управления симуляцией. Довольно подробный гайд по командам можно посмотреть вот здесь или здесь. Для скриптов ModelSim принят формат файла *.do. Создаём файл с указанным расширением в любом текстовом редакторе (блокнот, sublime text, vim, notepad++, НО НЕ WORD!!!), и пишем туда следующие команды:

if {[file exists sim]} {

cd sim

if {[file exists rtl_work]} {

vdel -lib rtl_work -all

}

} else {

mkdir sim

cd sim

}

vlib rtl_work

vmap work rtl_workРазберём этот кусочек скрипта.

Команда transcript с флагом on — это тоже самое что echo, т.е. после указания этой команды все последующие команды, указанные в скрипте, печатаются при выполнении в командной строке ModelSim, т.е. становится видно, какая команда когда исполнялась и после какой из них возникла ошибка (если возникла).

Далее мы проверяем, не существует ли в директории проекта директория sim, если существует, заходим в неё, проверяем, нет ли уже в списке библиотеки с именем rtl_work, и если есть, удаляем её целиком командой vdel с флагом -all. Eсли директория sim не существует, создаём её и переходим в неё, чтобы не засорять директорию проекта рабочими файлами симулятора.

Команда vlib создаёт библиотеку проекта с именем rtl_work.

Команда vmap устанавливает соответствие между библиотекой rtl_work и текущей директорией (которая доступна по команде pwd). Текущая директория в данном случае — это директория sim. Сменить текущую директорию можно командой cd (например, cd D:/Git/FPGA/HappyNY/simulation).

Продолжаем:

vlog -sv -work work +incdir+../ {../happyNY.sv}

vlog -sv -work work +incdir+../ {../tb.sv}Команда vlog с флагами — это вызов компилятора Verilog.

Флаг -sv, как вы уже догадались, указывает компилятору использовать стандарт SystemVerilog. Компилируются файлы все независимо, в отличие например от Quartus, поэтому если вы делаете, например, import каких-то частей package, то нужно делать их в каждом файле, где они используются, либо прямо внутри файла, содержащего package (Quartus, если не предусмотреть стражей включения, выкинет в этом случае ошибку).

Флаг -work говорит, в какую библиотеку нужно компилировать указанный файл.

Флаг +incdir+../ показывает, где компилятор должен искать включаемые файлы (т.е. файлы, указанные в коде с директивой `include).

В фигурных скобочках идёт имя компилируемого файла.

Продолжаем:

vsim -t 1ns -L rtl_work -L work -voptargs="+acc" tbКоманда vsim — это запуск симуляции.

Флаг -t задаёт точность временной сетки.

Флаг -L указывает, из какой библиотеки нужно работать.

Флаг -voptargs получает аргументы для последующего автоматического вызова оптимизатора vopt, т.е. произойдёт вызов vopt +acc. Этот флаг включает оптимизации для разных объектов в проекте и включает видимость этих объектов в симуляторе. Подробнее прочитать про него можно здесь на стр. 154.

В конце идёт имя top-level тестбенча, в данном примере оно совпадает с именем файла.

И, наконец, последняя часть скрипта:

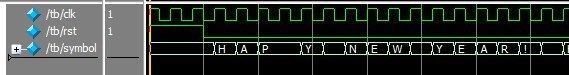

add wave /tb/clk

add wave /tb/rst

add wave -radix ASCII /tb/symbol

configure wave -timelineunits us

run -all

wave zoom fullСначала мы добавляем нужные нам сигналы на форму Wave Window командой add wave. Обратите внимание, что у одного из сигналов изменён формат отображения на символьный с помощью флага -radix ASCII.

Далее мы устанавливаем единицы шкалы временной сетки. Запускаем симуляцию по сценарию, написанному в тестбенче. Растягиваем (или сжимаем) картинку в Wave Window так, чтобы она поместилась точно в размер окна.

3. Запуск ModelSim с исполнением скрипта

Первым делом нужно открыть командную строку или терминал и перейти в директорию, где лежит ваш скрипт и файлы проекта. Затем нужно запустить исполняемый файл modelsim с ключом -do <script_name>, в нашем случае:

modelsim -do happyNY.doБольше ничего делать не нужно. Если по какой-то причине вы не смогли добавить путь к ModelSim в переменные среды, вместо modelsim можно указать полный путь к исполняемому файлу. Если и это не сработало, то, запустив ModelSim вручную, можно в командной строке ModelSim перейти в директорию проекта и запустить наш скрипт командой:

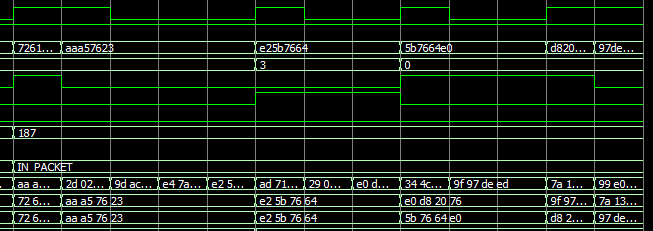

do happyNY.doПосле всех описанных процедур вы должны увидеть вот такую картинку:

Спасибо за внимание, удачи!

Автор: GREGOR_812