Думаю многие, кто работал с FPGA думали — а не сделать ли свой компьютер полностью на ней, с x86 процессором, периферией и прочим? 8-и битные компьютеры часто реализовывали в FPGA, но вот целый PC…

Думаю многие, кто работал с FPGA думали — а не сделать ли свой компьютер полностью на ней, с x86 процессором, периферией и прочим? 8-и битные компьютеры часто реализовывали в FPGA, но вот целый PC…

Для успешной работы помимо x86 процессора нужен еще BIOS со всеми реализованными прерываниями (включая доступ к «диску» на SD карте), BIOS VGA-совместимой видеокарты, вся периферия, контроллер памяти, таймер и многое другое. Задача намного сложнее чем кажется на первый взгляд, но тем не менее, в проекте ZetCPU она решена.

Из ограничений — работает только 16-и битный режим на 12.5Mhz, без математического сопроцессора.

Железо

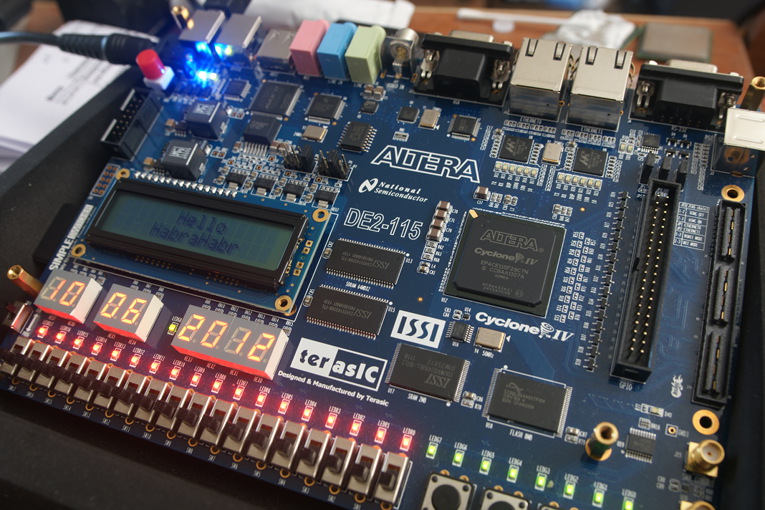

Для запуска нам понадобится отладочная плата с FPGA. Мне очень понравились плата Terasic DE2-115 (на Altera Cyclone IV с 115тыс. LE). Студенческая цена — 299$, меньше чем розничная цена одного чипа.

Также проект можно запустить на DE0 Nano со студенческой ценой 59$, но там будет работать только текстовый режим.

Запускаем

В установке есть несколько не очевидных моментов, не описанных в инструкции:

- Загружаем в плату прошивку DE2_115_ControlPanel.sof

- Запускаем DE2 ControlPanel и заливаем BIOS и загрузочную дискету во флеш память по инструкции

- Записываем образ жесткого диска на SD карту с помощью win32-image-writer, а не WinImage — он ломает загрузочный образ с большими картами

- Компилируем BIOS/VGA BIOS или берем из установочного архива готовые

- Компилируем нашу PC-шку в Quartus или берем готовый kotku.sof и прошиваем в плату

Теперь можно подключать к плате монитор, PS/2 клавиатуру — и включаем :-)

Можно добавлять свои инструкции в процессоре, свою периферию, посмотреть реализацию любых инструкций в verilog-исходниках…

module zet_div_uu(clk, ena, z, d, q, s, div0, ovf);

//

// parameters

//

parameter z_width = 16;

parameter d_width = z_width /2;

//

// inputs & outputs

//

input clk; // system clock

input ena; // clock enable

input [z_width -1:0] z; // divident

input [d_width -1:0] d; // divisor

output [d_width -1:0] q; // quotient

output [d_width -1:0] s; // remainder

output div0;

output ovf;

reg [d_width-1:0] q;

reg [d_width-1:0] s;

reg div0;

reg ovf;

//

// functions

//

function [z_width:0] gen_s;

input [z_width:0] si;

input [z_width:0] di;

begin

if(si[z_width])

gen_s = {si[z_width-1:0], 1'b0} + di;

else

gen_s = {si[z_width-1:0], 1'b0} - di;

end

endfunction

function [d_width-1:0] gen_q;

input [d_width-1:0] qi;

input [z_width:0] si;

begin

gen_q = {qi[d_width-2:0], ~si[z_width]};

end

endfunction

function [d_width-1:0] assign_s;

input [z_width:0] si;

input [z_width:0] di;

reg [z_width:0] tmp;

begin

if(si[z_width])

tmp = si + di;

else

tmp = si;

assign_s = tmp[z_width-1:z_width-d_width];

end

endfunction

//

// variables

//

reg [d_width-1:0] q_pipe [d_width-1:0];

reg [z_width:0] s_pipe [d_width:0];

reg [z_width:0] d_pipe [d_width:0];

reg [d_width:0] div0_pipe, ovf_pipe;

//

// perform parameter checks

//

// synopsys translate_off

initial

begin

if(d_width !== z_width / 2)

$display("div.v parameter error (d_width != z_width/2).");

end

// synopsys translate_on

integer n0, n1, n2, n3;

// generate divisor (d) pipe

always @(d)

d_pipe[0] <= {1'b0, d, {(z_width-d_width){1'b0}} };

always @(posedge clk)

if(ena)

for(n0=1; n0 <= d_width; n0=n0+1)

d_pipe[n0] <= d_pipe[n0-1];

// generate internal remainder pipe

always @(z)

s_pipe[0] <= z;

always @(posedge clk)

if(ena)

for(n1=1; n1 <= d_width; n1=n1+1)

s_pipe[n1] <= gen_s(s_pipe[n1-1], d_pipe[n1-1]);

// generate quotient pipe

always @(posedge clk)

q_pipe[0] <= 0;

always @(posedge clk)

if(ena)

for(n2=1; n2 < d_width; n2=n2+1)

q_pipe[n2] <= gen_q(q_pipe[n2-1], s_pipe[n2]);

// flags (divide_by_zero, overflow)

always @(z or d)

begin

ovf_pipe[0] <= !(z[z_width-1:d_width] < d);

div0_pipe[0] <= ~|d;

end

always @(posedge clk)

if(ena)

for(n3=1; n3 <= d_width; n3=n3+1)

begin

ovf_pipe[n3] <= ovf_pipe[n3-1];

div0_pipe[n3] <= div0_pipe[n3-1];

end

// assign outputs

always @(posedge clk)

if(ena)

ovf <= ovf_pipe[d_width];

always @(posedge clk)

if(ena)

div0 <= div0_pipe[d_width];

always @(posedge clk)

if(ena)

q <= gen_q(q_pipe[d_width-1], s_pipe[d_width]);

always @(posedge clk)

if(ena)

s <= assign_s(s_pipe[d_width], d_pipe[d_width]);

endmodule

Переходим к тестированию

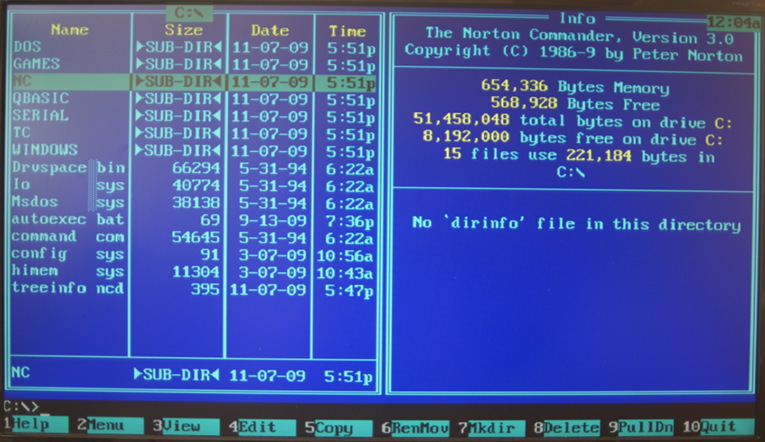

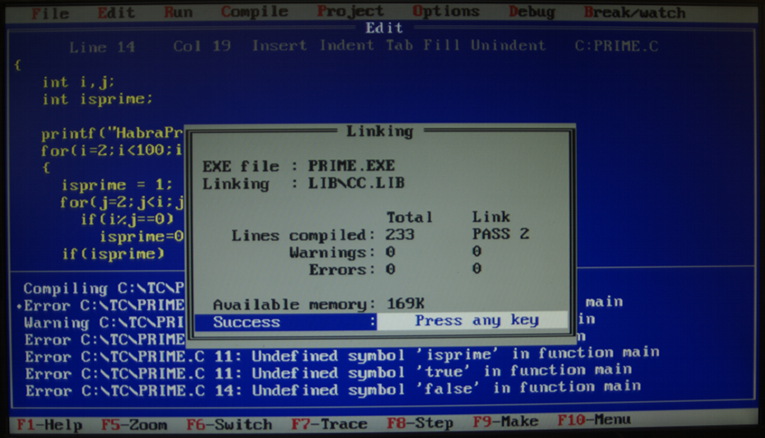

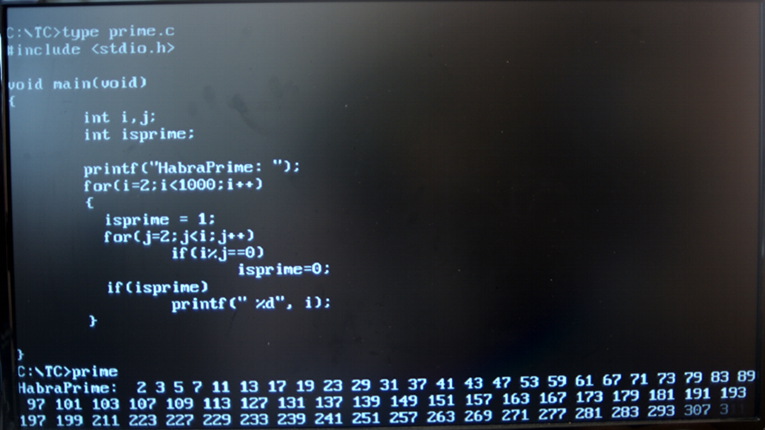

Заранее прошу прощения за экранные копии:

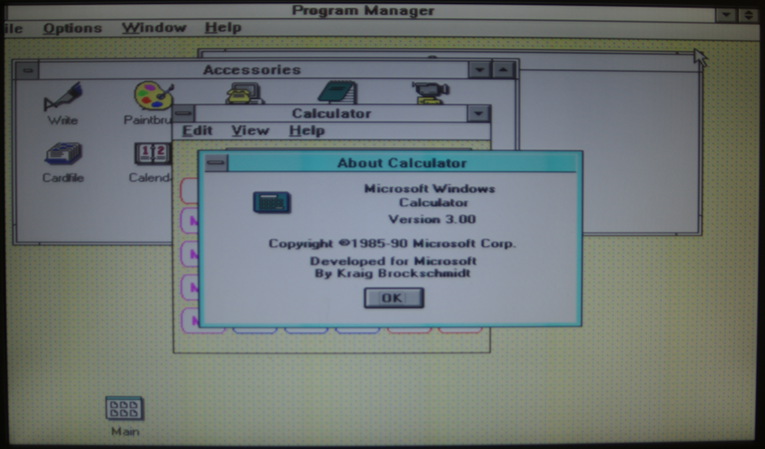

Далее — программирование. Скорость компиляции и выполнения навивает ностальгию…

Заключение

Надеюсь статья заставила вас поверить в силу FPGA и продолжить изучение Verilog.

А у кого-то возможно теперь исполнится мечта сделать свою PC-шку с блекджеком :-)

Вопросы/комментарии?

Автор: BarsMonster