На днях решил систематизировать знания, касающиеся принципов отображения оперативной памяти на кэш память процессора. В результате чего и родилась данная статья.

Кэш память процессора используется для уменьшения времени простоя процессора при обращении к RAM.

Основная идея кэширования опирается на свойство локальности данных и инструкций: если происходит обращение по некоторому адресу, то велика вероятность, что в ближайшее время произойдет обращение к памяти по тому же адресу либо по соседним адресам.

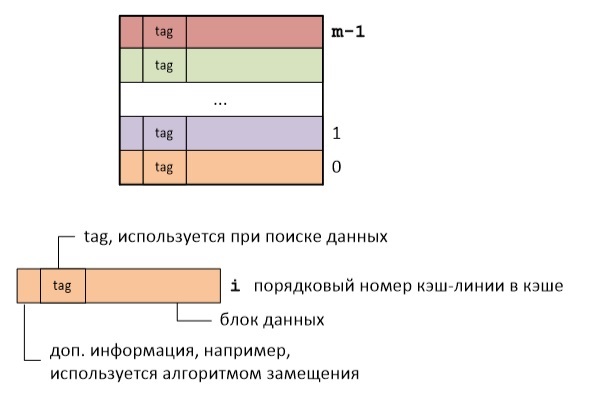

Логически кэш-память представляет собой набор кэш-линий. Каждая кэш-линия хранит блок данных определенного размера и дополнительную информацию. Под размером кэш-линии понимают обычно размер блока данных, который в ней хранится. Для архитектуры x86 размер кэш линии составляет 64 байта.

Так вот суть кэширования состоит в разбиении RAM на кэш-линии и отображении их на кэш-линии кэш-памяти. Возможно несколько вариантов такого отображения.

DIRECT MAPPING

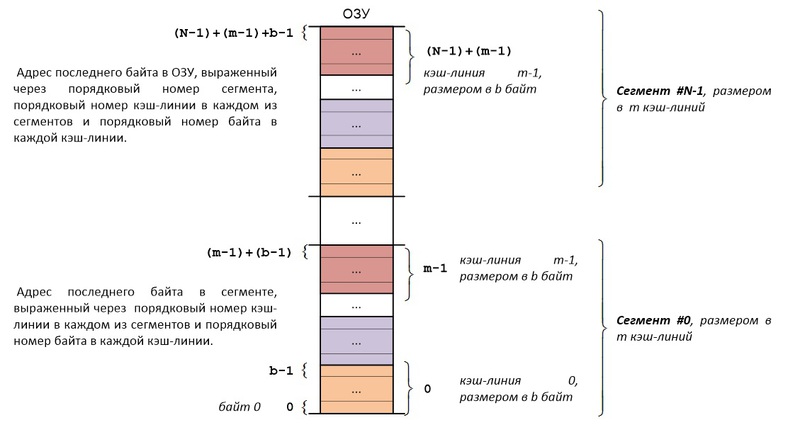

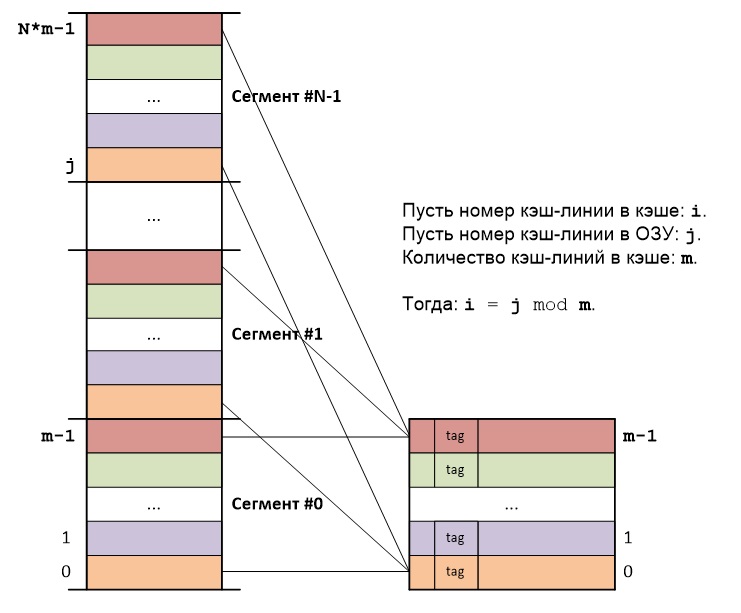

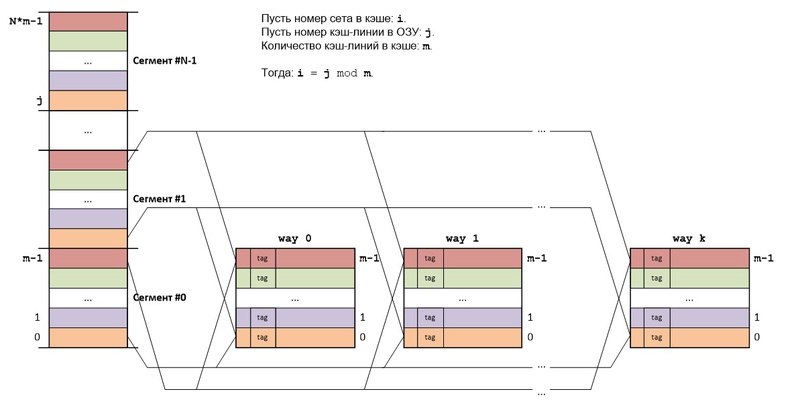

Основная идея прямого отображения (direct mapping) RAM на кэш-память состоит в следующем: RAM делится на сегменты, причем размер каждого сегмента равен размеру кэша, а каждый сегмент в свою очередь делится на блоки, размер каждого блока равен размеру кэш-линии.

Блоки RAM из разных сегментов, но с одинаковыми номерами в этих сегментах, всегда будут отображаться на одну и ту же кэш-линию кэша:

Адрес каждого байта представляет собой сумму порядкового номера сегмента, порядкового номера кэш-линии внутри сегмента и порядкового номера байта внутри кэш-линии. Отсюда следует, что адреса байт различаются только старшими частями, представляющими собой порядковые номера сегментов, а порядковые номера кэш-линий внутри сегментов и порядковые номера байт внутри кэш-линий — повторяются.

Таким образом нет необходимости хранить полный адрес кэш-линии, достаточно сохранить только старшую часть адреса. Тэг (tag) каждой кэш-линии как раз и хранит старшую часть адреса первого байта в данной кэш-линии.

b — размер кэш-линии.

m — количество кэш-линий в кэше.

Для адресации b байт внутри каждой кэш-линии потребуется: log2b бит.

Для адресации m кэш-линий внутри каждого сегмента потребуется: log2m бит.

m = Объем кэш-памяти/Размер кэш линии.

Для адресации N сегментов RAM: log2N бит.

N = Объем RAM/Размер сегмента.

Для адресации байта потребуется: log2N + log2m + log2b бит.

Этапы поиска в кэше:

1. Извлекается средняя часть адреса (log2m), определяющая номер кэш-линии в кэше.

2. Тэг кэш-линии с данным номером сравнивается со старшей частью адреса (log2N).

Если было совпадение по одному из тэгов, то произошло кэш-попадание.

Если не было совпадение ни по одному из тэгов, то произошел кэш-промах.

FULLY ASSOCIATIVE MAPPING

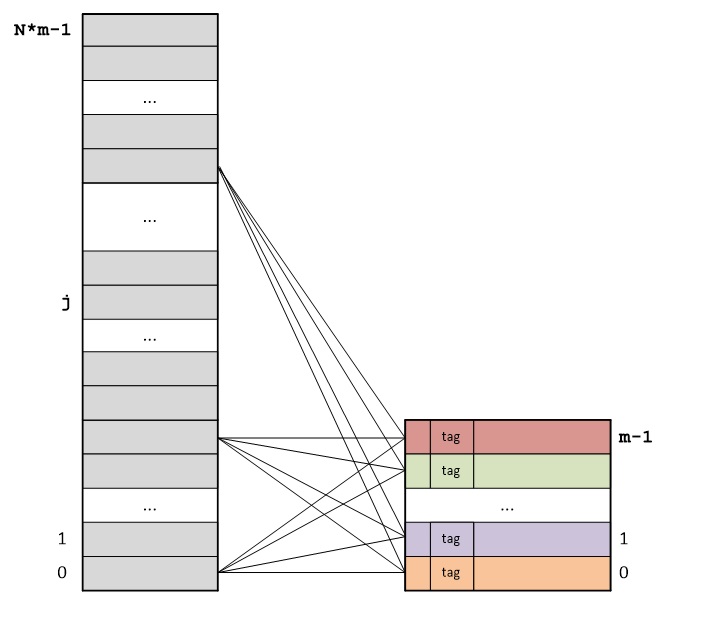

Основная идея полностью ассоциативного отображения (fully associative mapping) RAM на кэш-память состоит в следующем: RAM делится на блоки, размер которых равен размеру кэш-линий, а каждый блок RAM может сохраняться в любой кэш-линии кэша:

Адрес каждого байта представляет собой сумму порядкового номера кэш-линии и порядкового номера байта внутри кэш-линии. Отсюда следует, что адреса байт различаются только старшими частями, представляющими собой порядковые номера кэш-линий. Порядковые номера байт внутри кэш-линий повторяются.

Тэг (tag) каждой кэш-линии хранит старшую часть адреса первого байта в данной кэш-линии.

b — размер кэш-линии.

m — количество кэш-линий, умещающихся в RAM.

Для адресации b байт внутри каждой кэш-линии потребуется: log2b бит.

Для адресации m кэш-линий: log2m бит.

m = Размер RAM/Размер кэш-линии.

Для адресации байта потребуется: log2m + log2b бит.

Этапы поиска в кэше:

1. Тэги всех кэш-линий сравниваются со старшей частью адреса одновременно.

Если было совпадение по одному из тэгов, то произошло кэш-попадание.

Если не было совпадение ни по одному из тэгов, то произошел кэш-промах.

SET ASSOCIATIVE MAPPING

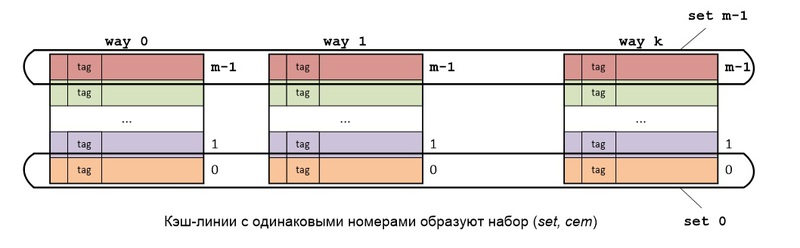

Основная идея наборно ассоциативного отображения (set associative mapping) RAM на кэш-память состоит в следующем: RAM делится также как и в прямом отображении, а сам кэш состоит из k кэшей (k каналов), использующих прямое отображение.

Кэш-линии, имеющие одинаковые номера во всех каналах, образуют set (набор, сэт). Каждый set представляет собой кэш, в котором используется полностью ассоциативное отображение.

Блоки RAM из разных сегментов, но с одинаковыми номерами в этих сегментах, всегда будут отображаться на один и тот же set кэша. Если в данном сете есть свободные кэш-линии, то считываемый из RAM блок будет сохраняться в свободную кэш-линию, если же все кэш-линии сета заняты, то кэш-линия выбирается согласно используемому алгоритму замещения.

Структура адреса байта в точности такая же, как и в прямом отображении: log2N + log2m + log2b бит, но т.к. set представляет собой k различных кэш-линий, то поиск в кэше немного отличается.

Этапы поиска в кэше:

1. Извлекается средняя часть адреса (log2m), определяющая номер сэта в кэше.

2. Тэги всех кэш-линий данного сета сравниваются со старшей частью адреса (log2N) одновременно.

Если было совпадение по одному из тэгов, то произошло кэш-попадание.

Если не было совпадение ни по одному из тэгов, то произошел кэш-промах.

Т.о количество каналов кэша определяет количество одновременно сравниваемых тэгов.

Автор: FeRViD