Продолжение предновогодней серии приключений маленькой ПЛИС Altera EPM7064 на отладочной плате — Франкенштейн. В предыдущей серии...

Настала пора сравнить две ПЛИС из одной весовой категории: Altera EPM7064 и Lattice LC4064v. Хотя, один у них — только вес — это 64 макроячейки. В остальном, судя по параметрам, у этих ПЛИС совсем разные назначения. ПЛИС от Altera, судя по документации 2005 года, является просто не молодой, от этого и обладает низким количеством ячеек. Так же, обладает популярным по тем временам напряжением питания — 5 вольт. Максимальная рабочая частота не превышает 200 МГц. В то же время Lattice может работать до частот в 400 МГц, но при этом, питается от напряжения — 3.3 вольта. Да, это не так удобно, как 5 вольт, если мы хотим взаимодействовать со старыми схемами (однако, заявлена толерантность к 5В). В документации на Lattice этой серии указан 2014 год, поэтому я предположу, что это современные высокоскоростные ПЛИС, но малого объема, и судя по "SuperFAST CPLD" в описании, позиционируются они несколько иначе.

Настала пора сравнить две ПЛИС из одной весовой категории: Altera EPM7064 и Lattice LC4064v. Хотя, один у них — только вес — это 64 макроячейки. В остальном, судя по параметрам, у этих ПЛИС совсем разные назначения. ПЛИС от Altera, судя по документации 2005 года, является просто не молодой, от этого и обладает низким количеством ячеек. Так же, обладает популярным по тем временам напряжением питания — 5 вольт. Максимальная рабочая частота не превышает 200 МГц. В то же время Lattice может работать до частот в 400 МГц, но при этом, питается от напряжения — 3.3 вольта. Да, это не так удобно, как 5 вольт, если мы хотим взаимодействовать со старыми схемами (однако, заявлена толерантность к 5В). В документации на Lattice этой серии указан 2014 год, поэтому я предположу, что это современные высокоскоростные ПЛИС, но малого объема, и судя по "SuperFAST CPLD" в описании, позиционируются они несколько иначе.

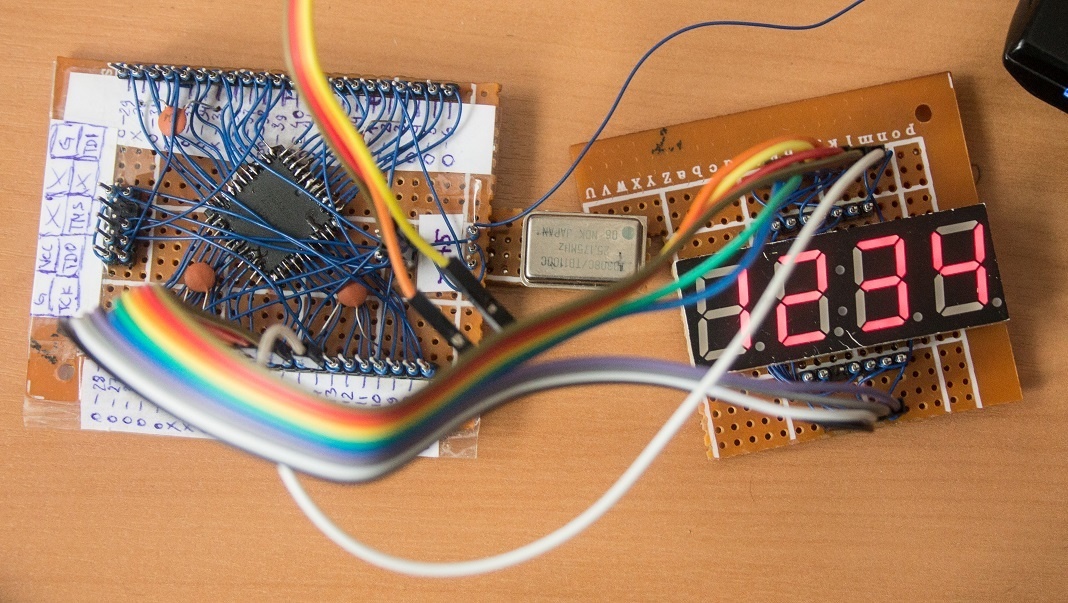

Как нам их сравнить? Попробуем решить на них одну и ту же задачу. Часы на Lattice LC4064v мы уже попробовали сделать и у нас получилось. Теперь попробуем сделать часы на Altera EPM7064 — на нашем Франкенштейне.

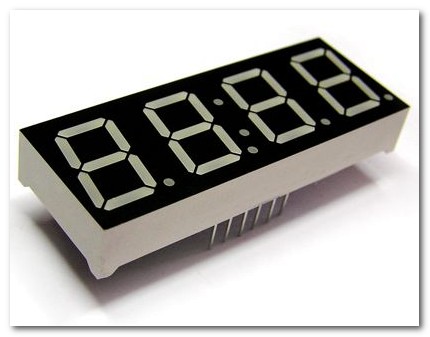

Индикатор

Плата у нас уже готова, поэтому нам нужно добавить к ней индикатор. Естественно, динамический. Для чистоты эксперимента, конечно, нужно было бы применить тот же самый индикатор, что и на Lattice (или идентичный). Но такого же у меня нет, а снимать детали с рабочих устройств, я считаю плохой привычкой. Поэтому я взял другой, подходящий для изготовления часов индикатор, который мне недавно подарили.

Выглядит он совсем, как этот, однако имеет другую распиновку.

Найти ее мне не удалось. Описывать ее не вижу смысла, т.к. таких экранов много и они могут быть разными. С помощью тестера можно легко установить назначения выводов. А с помощью макетной платы и своего любимой технологии монтажа накруткой, я упорядочил последовательность выводов индикатора (1-2-3-4, A-B-C-D-E-F-G).

В часах на Lattice я использовал транзисторы, для разгрузки линий, выбирающих группы. Тут же я решил ничего этого не делать, а подключить светодиоды напрямую к выводам ПЛИС, даже не используя токоограничивающих резисторов (вообще так делать не правильно). Логика примерно, как на этом рисунке:

В итоге, тестовая конфигурация отобразила цифры 1-2-3-4. Светодиоды достаточно яркие. ПЛИС почти не греется. Надеюсь, Френки доживет до светлых дней и не выйдет из строя от такой нагрузки. А чтобы снизить эту вероятность, уменьшим период, в течение которого индикаторы будут включены, тем самым, снизив и яркость индикатора.

В целом, код весь тот же самый, кроме логики вывода на экран.

module epm7064_clock(clk, dig_sel, segs, btn_HH, btn_MM, btn_SS, btn_SAFE, led_second_tick);

...

output wire [3:0] dig_sel; // выбор номера цифры

output wire [6:0] segs; // номера сегментов

...

//номера цифр чередуются, для этого возьмем несколько бит счетчика-делителя тактовой частоты

//конкретные номера бит выбираются из расчета полученной частоты

//младшие биты равные нолю я выбрал для того, чтобы светодиоды работали только 1/4 времени.

//цифры выбираются по очереди 0001 -> 0010 -> 0100 -> 1000

wire [3:0] top_bits = clk_div[6:3]; //

wire [4:0] t_dig_sel = (top_bits == 4'b0000 && h_show &&(!SAFE_MODE)) ? 4'b0001 :

(top_bits == 4'b0100 &&(!SAFE_MODE)) ? 4'b0010 :

(top_bits == 4'b1000 &&(!SAFE_MODE)) ? 4'b0100 :

(top_bits == 4'b1100 &&(!SAFE_MODE)) ? 4'b1000 : 4'b0000;

//значения семисегментных индикаторов соответствующего разряда

//выбираются в зависимости от номера цифры, которая сейчас выводится

...

bcd2seg0_2 sseg_1( .sin(hh), .sout(s_m1));

bcd2seg0_9 sseg_2( .sin(h), .sout(s_m2));

bcd2seg0_5 sseg_3( .sin(mm), .sout(s_m3));

bcd2seg0_9 sseg_4( .sin(m), .sout(s_m4));

wire [6:0] t_segs = (top_bits == 4'b0000) ? ~s_m1 :

(top_bits == 4'b0100) ? ~s_m2 :

(top_bits == 4'b1000) ? ~s_m3 :

(top_bits == 4'b1100) ? ~s_m4 : 7'b0000000;

...

//остальной код не отличается

Проект полностью — https://github.com/UA3MQJ/epm7064_clock

Тактовый генератор

В часах на Lattice я пытался запустить генератор на логических элементах самой ПЛИС. В этот раз я тоже попробовал запустить генератор, только уже на Altera. В сети есть упоминания о том, что генераторы успешно запускались на max и даже на cyclone. Но мне запустить генератор на 32768 так и не удалось. Может это кварц неудачный попался, либо я его в процессе экспериментов попортил, или параметры не те. Пробовал как схему с одним инвертором, так и с двумя. Инверторы брал как буфером, так и без. В общем, целый выходной был потрачен зря, запустить генератор не удалось.

Вообще считается, что такие генераторы — это плохая идея. Готовые генераторы стабильнее, разработка быстрее. С другой стороны, те, кто сумел все правильно рассчитать и стабильно запустить генератор на ПЛИС, пользуются таким решением.

Вообще считается, что такие генераторы — это плохая идея. Готовые генераторы стабильнее, разработка быстрее. С другой стороны, те, кто сумел все правильно рассчитать и стабильно запустить генератор на ПЛИС, пользуются таким решением.

А пока, я не смог запустить генератор, я подожду, может это сумеет сделать мой товарищ. А я пока закажу 32.768KHz OSC Active Crystal Oscillator.

Схема из [1] почему-то тоже не заработала. Вернее, генерация там была, но амплитуда была мала, и стабильности формы сигнала было недостаточно, чтобы с ней смог синхронизироваться мой осциллограф. Возможно, всетаки, проблема с конкретным кварцем.

Для проверки, можно использовать генератор часов на Lattice, что мы и сделаем

Выводы

Внутри ПЛИС от Altera мы реализовали ту же самую логику, за исключением вывода на светодиодный экран (т.к. он другого типа). Интересно заметить, что затраченные ресурсы ПЛИС Altera составили 61 ячейку, в то время, как у Lattice было потрачено 59. Я думаю, что причина как раз в разных экранах. У Lattice для управления экраном используется 16 линий, а для экрана на Altera требуется 11 линий. Возможно, на меньшее количество линий получилось сложнее дешифровать. Так что можно считать, что синтезаторы и аппаратные возможности у них равны. Выходной ток Altera немного выше, и другой тип экрана, поэтому удалось обойтись без дополнительных транзисторов, и светодиодный индикатор подключился и заработал вообще на прямую.

Ток потребления Altera EPM7064 составил в среднем 100 мA и в 66 мА в safe_mode (без учета тока генератора 32768 Гц), в то время, как Lattice потребляет 125 мА при 3.3 вольтах. Потребление примерно одного порядка. В целом, питание от 5 вольт более удобное. Однако в этом проекте это только вопрос стабилизатора напряжения, т. к. взаимодействия с другими микросхемами пяти-вольтовой логики нет. Поэтому и преимущества перед 3.3В питанием тоже нет.

Генератор на 32768 собрать не удалось ни на Lattice ни на Altera. Убежден, что генератор можно соорудить, в данном проекте такой аппаратный хак был бы весьма эффектен, но не получилось.

И мы не будем задерживаться, потому что хотим увидеть Френки в других проектах!

Список использованных источников

- СЕМИСЕГМЕНТНЫЙ ИНДИКАТОР. ОРГАНИЗАЦИЯ ДИНАМИЧЕСКОЙ ИНДИКАЦИИ

- Калейдоскоп схем кварцевых НЧ генераторов

Автор: UA3MQJ