На днях я встретился и взял короткое видеоинтервью у Kathy Giori, Vice President Operations Arduino USA. Мы обсудили с Кати новое веяние, которое уже коснулось и Ардуино-коммьюнити: так как программированию микроконтроллеров с помощью Ардуино уже все более-менее научены, то пора делать следующий шаг: учить школьников использовать язык описания аппаратуры Verilog и микросхемы ПЛИС / FPGA, матрицы логических элементов с изменяемыми функциями. А для того, чтобы сделать освоение FPGA проще, стоит воскресить упражнения с микросхемами малой степени интеграции, популярные в 1970-х, в качестве приквела к современным FPGA. Все это закроет брешь между физикой и программированием, дискретными элементами и микроконтроллерами, транзистором и Ардуино.

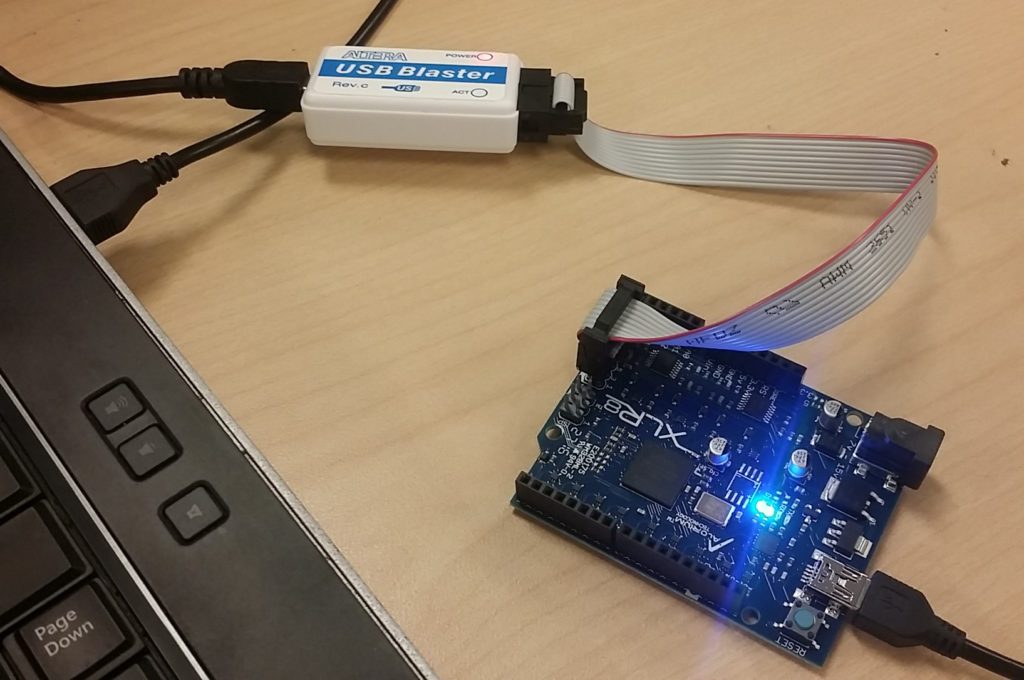

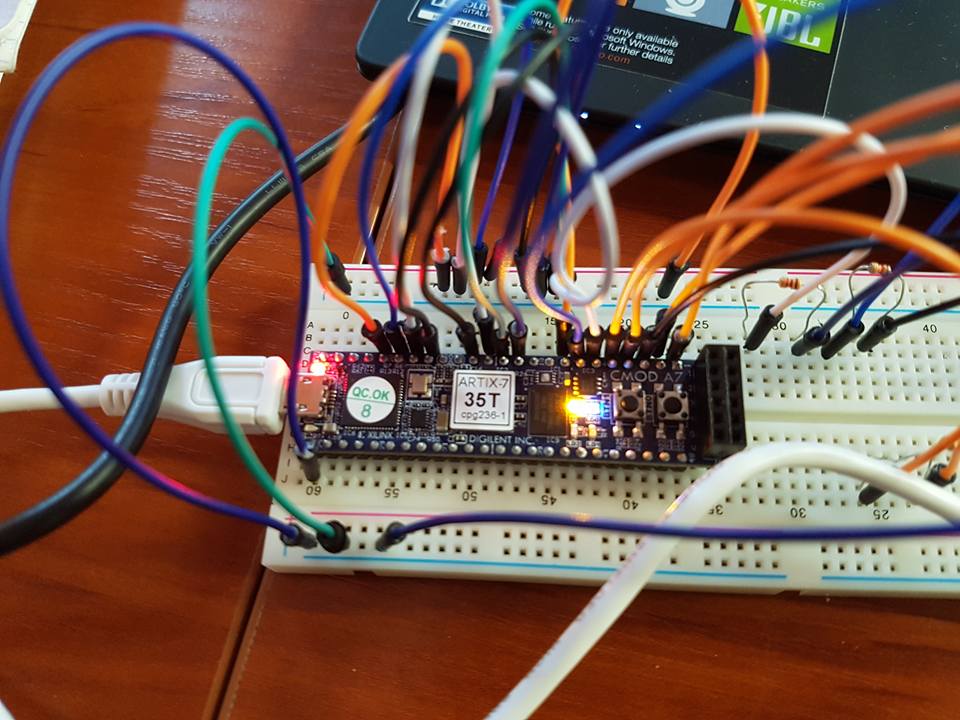

FPGA и платы можно использовать от любого производителя (Xilinx, Altera, Lattice, Digilent, Terasic), все что я пишу ниже, не имеет привязки к той или иной компании.

В разговоре с Кати принимала участие преподаватель Стенфорда Светлана Хутка, которая рассказала Кати об эксперименте по бесплатному обучению школьников использованию FPGA в Киеве, силами преподавателей-энтузиатов из нескольких киевских вузов. После этого я поделился с Кати планами проведения следующего такого эксперимента на известной еще с советских времен летней школе юных программистов в Новосибирске, а также поговорил с другими присутствующими товарищами из Ардуино-коммьюнити о внедрении FPGA в двух школах и одном коледже Silicon Valley.

Плата c FPGA, которую сейчас рекомендует Кати, и которую я несколько переделываю, чтобы приспособить к своим нуждам (про это будет отдельный пост):

Ниже я приведу как информацию по результатам киевского эксперимента, так и некоторые планы на будущее, которые сейчас разрабатывают активисты — преподаватели физматшкол и вузов Киева, Чернигова, Новосибирска, Москвы, Нижнего Новгорода, Самары, Санкт-Петербура, Алматы и других городов. На киевском семинаре участники дошли до создания конечных автоматов кодового замка и интеграции с простыми периферийными устройствами (16-кнопочная клавиатура, динамик). На летней школе в Новосибирске у нас времени будет больше и мы попробуем построить со школьниками процессор. В перспективе из этого планируется сделать годовой курс основ цифровой электроники на FPGA для физматшкол, который может обогатить школьное образование, как в 1980-х его обогатило введение элементов программирования.

Обсудим это детально:

1. Зачем учить школьников языкам описания аппаратуры и использованию ПЛИС? Обоснование программы.

В картине мира, представляемой школьным образованием, существует “слепое пятно” в области принципов проектирования цифровой электроники, между физикой и программированием. Курсы роботики и ардуино это слепое пятно не закрывают, так как сводятся к программированию готовых чипов. Упражнения с дискретными элементами и микросхемами малой степени интеграции, хотя и эффективны во введении в основные принципы, базируются на технологиях 1960-1970-х годов и не содержат привязки к современному проектированию. Слепое пятно можно закрыть с помощью введения элементов языков описания аппаратуры (ЯОА) и доступные для школьного экспериментирования микросхемы ПЛИС (программируемые логические интегральные схемы) — матрицы реконфигурируемых логических элементов. Тем самым картина мира становится цельной, и способствует созданию среды для появления большого количества молодых инженеров, имеющих представление о всех сторонах современных микросхем для приложений типа самоуправляемых автомобилей, и способных в будущем специализироваться для проектирования того или иного аспекта таких устройств.

Введение ЯОА и ПЛИС в школьную программу также хорошо привязывается к курсу математики и физики физматшкол — булевская алгебра, арифметические схемы, конечные автоматы.

Заметим, что ЯОА и ПЛИС, несмотря на поверхностное сходство с программированием, используют другие базовые концепции:

Программирование: последовательное исполнение, ветви выбора, циклы, переменные, выражения, массивы (c моделью плоской адресуемой памяти), функции (на основе использования стека), рекурсия.

Проектирование цифровой логики: комбинационный логический элемент; построение из этих элементов облаков комбинационной логики, включающей примитивы выбора с помощью мультиплексоров, а также блоки для реализации арифметических выражений; концепция тактового сигнала для синхронизации вычислений и повторения, концепция D-триггера для хранения текущего состояния между тактами; конечный автомат; параллельность операций, иерархия модулей, концепция конвейера (не только для процессора, но и для арифметических блоков).

2. Общий план таких курсов:

-

Секция 1. Соединение с физикой, с лабораторными на дискретных компонентах.

-

Секция 2. Основы цифровой логики и арифметики, с лабораторными на микросхемах малой степени интеграции.

-

Секция 3. Проектирование схем на основе синтеза языка описания аппаратуры, с лабораторными на ПЛИС Xilinx или Altera.

-

Секция 4. Архитектура процессора: вид со стороны программиста, с лабораторными с помощью симулятора RISC-процессора на уровне инструкций, например MARS MIPS.

-

Секция 5. Микроархитектура: строим процессор.

-

Индивидуальный проект: интеграция датчика или другого периферийного устройства с схемой, реализованной в ПЛИС.

3. Итоги киевского эксперимента.

Развернутый текст с итогами киевского эксперимента написал преподаватель Киевского Политехнического Института Евгений Короткий. Я дополню его своими личными выводами. Предыстория — посты на Хабре и Geektimes — 1, 2, 3, 4). В тех постах были заданы вопросы. Вот какие получились ответы:

-

Гипотеза, что школьники могут использовать Verilog, подтвердилась

-

Verilog также оказался достаточному количеству школьников интересен (до Киева некоторые коллеги в этом сомневались, утверждая, что детям более интересны проекты типа роботической руки с микроконтроллером)

-

Идея, что перед использованием Verilog полезно показать школьникам логические элементы и D-триггер на микросхемах малой степени интеграции — не то чтобы однозначно подтвердилась, но получила большее обоснование.

-

Всего после дня опыта с верилогом некоторые школьники начали задавать вразумительные вопросы — например когда применять блокирующее, а когда неблокирующее присваивание.

-

Довести школьников от нуля до конечных автоматов, реализующих протоколы типа SPI — за одну неделю по-видимому нереально, а вот до конечного автомата кодового замка или светофора — реально.

-

Также нереально довести за одну неделю по конструирования процессора, но мы попробуем это сделать за две недели в Новосибирске.

-

Во время киевского эксперимента мы пробовали рассказать и про FPGA, и про встроенные процессоры (MediaTek MT7688, находящийся где-то посередине между Ардуино и Интел Галилео или Расбери Пай по производительности). Потом мы сделали хакатон (в Киевско-Могилянской Академии) и пронаблюдали, сколько школьников выбрали для хакатона проект с FPGA и сколько — проект с встроенным процессором. Выяснилось — 50 на 50. Это интересно — до хакатона у меня не было вообще никакого предположения, какая будет разбивка.

-

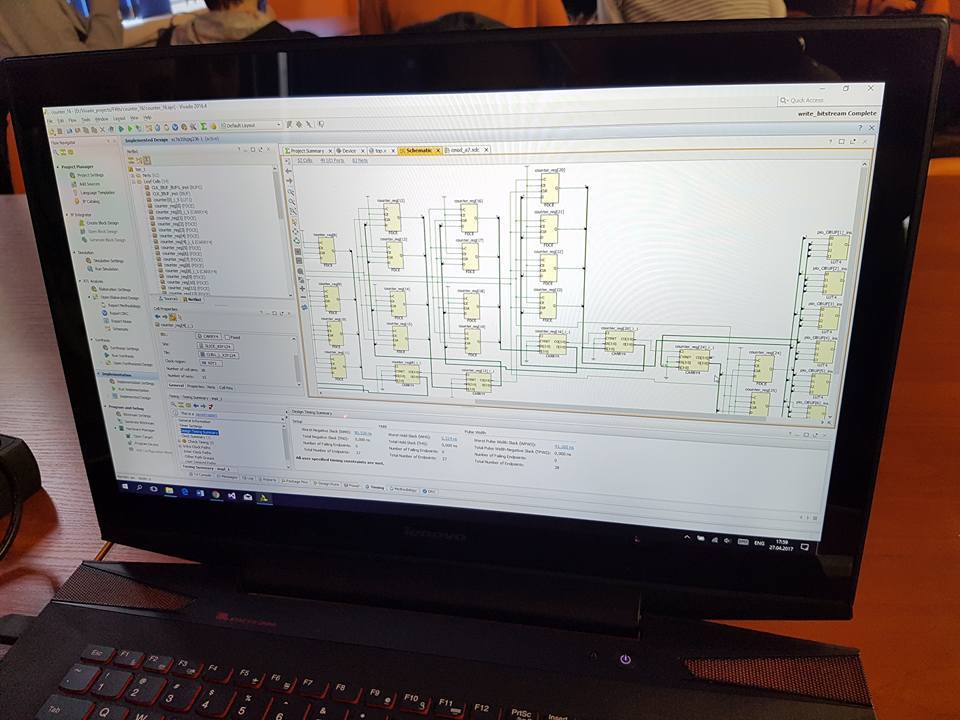

У меня было опасение, что школьников может запутать пользовательский интерфейс в Xilinx Vivado, с кучей опций и элементов интерфейса. Но оказалось, что школьникам все равно — сложный GUI их не пугает.

-

Большинство школьников используют Windows. У меня вместе с моим коллегой Александром Белицем есть идея заготовить для таких мероприятий пару десятков bootable SSD-драйвов с Линуксом (Ubuntu или CentOS) и носить их от мероприятия к мероприятияю. Алекс даже написал скрипт для клонирования таких драйвов. Ubuntu более дружелюбен, но CentOS более официально поддерживается средствами автоматизации проектирования схем на FPGA, в частности Xilinx Vivado и Altera Quartus. Можно ли делать одновременно ликбез по Линуксу и ликбез по Verilog / FPGA во время летнего лагеря? Непонятно, но это можно попробовать.

-

Оказывается, Xilinx Vivado нещадно глючит приконфигурации Artix-7 FPGA, если использовать дешевые плохо экранированные микро-USB кабели. По какому-то мистическому наитию я перед поездкой в Киев засунул в чемодан дюжину качественных шнуров, и это спасло семинар.

-

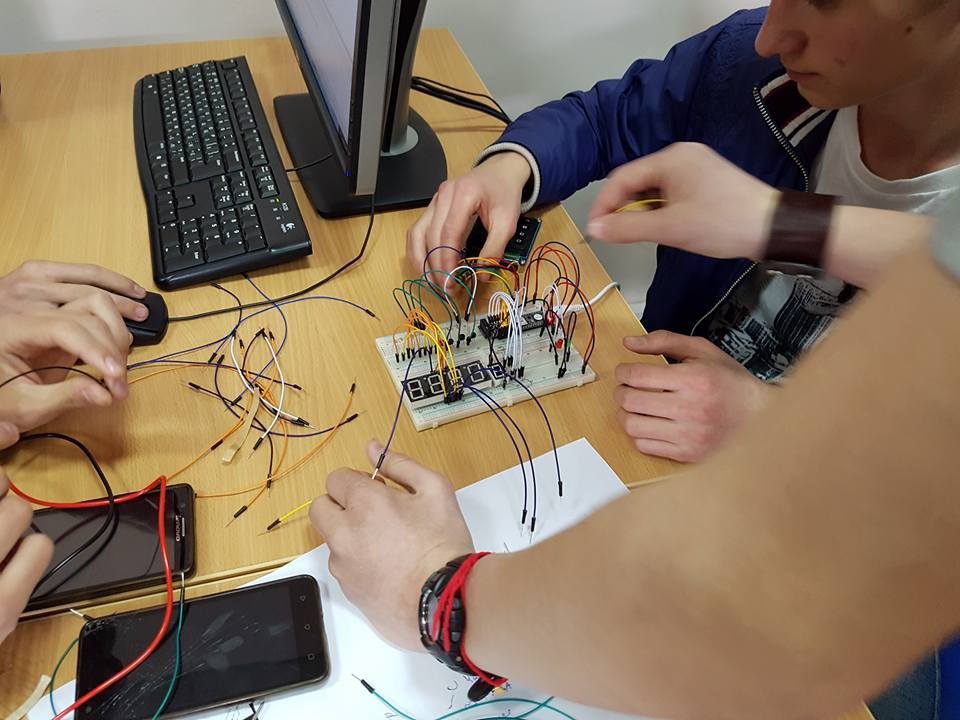

У меня была идея, что использование breadboardable FPGA modules (FPGA плат, которые втыкаются в макетные платы), например Digilent Cmod A7 35T, может облегчить школьникам переход с упражнений с микросхемами малой степени интеграции на упражнения с FPGA. Верна ли эта идея, я так и не понял. Возможно использование более крупных плат с богатым набором периферии, например Terasic DE10-Lite, будет ничуть не хуже. Все равно при переходе с микросхем малой степени интеграции (CMOS 4000 или 74HC) на FPGA — нужно менять напряжение питания (с 9 V или 5 V на 3.3 V), поэтому нельзя воткнуть Cmod A7 вместо скажем CMOD 4013 в одну и ту же макетную плату с лампочками и кнопками, и ожидать, что все будет продолжать работать.

-

Я подтвердил свое наблюдение, что для проведения краткосрочных (1 неделя) образовательных мероприятий критично, чтобы на месте находилась бригада студентов местного университета, которая бы осуществляла менторство школьников. В киевском случае такую бригаду обеспечил преподаватель Киевского Политехнического Института Евгений Короткий.

-

Стало более-менее понятно, в каких случаях и в каком объеме стоит включать в программу подобных мероприятий часть про уровень транзисторов и про производства микросхем. Эту часть преподавал доцент Киевского Национального Университета Александр Барабанов, переводчик материалов по курсу Nanometer ASIC для студентов. По-видимому, этот материал стоит в полном объеме включать в годовой курс для школьников, в небольшом — в двухнедельный курс в формате летнего лагеря, но при продолжительности меньше недели нужно наверное сразу (в течение 1 часа после начала) давать школьникам микросхемы малой степени интеграции (например CMOS 4000) и про транзистор упомянуть вскользь, в виде «транзистор — это устройство, в котором ток течет из пукта A в пункт B, если в C стоит напряжение 1 (или 0). Из транзисторов можно строить логические элементы И, ИЛИ, НЕ (показать на картинку)».

-

Во время лекций перед большой аудиторией школьникам можно показывать схемы, собранные на макетной плате из микросхем малой степени интеграции. Это наглядно, вызывет интерес, а также не требует подключения конструкции к компьютеру — только с батарейке 9 V. Я показывал три таких схемы, наиболее критичных для понимания — логический элемент XOR, комбинационный 4-битный сумматори D-триггер с частотой порядка 1 Герц (т.е. такт в секунду).

-

Остается открытым вопрос, можно ли преподавать школьникам идею конвейерной обработки, одну из самых мощных идей в цифровом проектировании и организации вычислений вообще. Для этого необязательно строить конвейерный процессор, можно сделать и конвейерное арифметическое устройство. Наверное это можно упомянуть в самом конце курса, когда дети наиграются с простыми комбинационными и последовательностным схемами и конечными автоматами. Скорее всего это будет интересно очень небольшому подмножеству школьников, но попробовать стоит.

-

Для мероприятий подлиннее можно использовать индивидуальные проекты и проверочные работы.

Код на GitHub использованный для киевского мероприятия

4. Источники информации для разработки будущих материалов.

Источники информации для преподавателей физматшкол, которые по-видимому будут разрабатывать большую часть детальных материалов, после начальных экспериментов со школьниками на Украине, в России и в Silicon Valley:

-

Учебник Дэвида Харриса и Сары Харрис “Цифровая схемотехника и архитектура компьютера”, 2-е издание, русский перевод. Этот учебник можно скачать бесплатно, см. статьи на Хабре о нем — 1, 2, 3. Недавно также вышло новое бумажное издание с улучшенной цветной полиграфией

-

Слайды для преподавателей, дополнение к учебнику Харрис & Харрис. Бесплатное скачивание.

-

Материалы по курсу From NAND to Tetris, который был создан в Израиле и внедрен в некоторые американские университеты. При этом, имхо, от курса стоит использовать идеи и скелет, но реализацию делать на подмножествах “взрослых” средств проектирования, а не искуственных “детских” средствах, как делает это курс. Ключевые части скачиваются бесплатно.

-

Книга Чарльза Петзольда “Код”, которая адекватно объясняет на пальцах многие концепции и уровень которой соответствует школьному (идея подсказана преподавателем киевской школы ОРТ Сергеем Дзюбой). Опять же, с моей точки зрения, из книги стоит использовать идеи и скелет, но бОльшую часть материала заменить на более корректный (вместо защелок (D-latch) использовать D-триггеры (D-flip-flop)) и современный, например вместо accumulator-based 6800 и архаичного 8080 использовать подмножество RISC-архитектуры.

-

Наборы для конструирования схем на макетной плате на основе дискретных компонент и микросхем малой степени интеграции от американской компании ETron Circuit Labs, российской компании Киберфизика, украинской компании Радиомаг (я могу объяснить различия между этими наборами в комментариях, если кому интересно).

-

Материалы компаний-производителей микросхем ПЛИС (Xilinx, Altera) и образовательных плат с микросхемами ПЛИС (Digilent, Terasic).

-

Примеры кода, контрольные работы и рекомендации по проектам, разработанные Антоном Моисеевым, Юрием Панчулом, Евгением Коротким, Александром Барабановым и другими инженерами компаний и преподавателями университетов для различных мероприятий в Калифорнии, Казахстане, России и Украине.

5. План на будущее номер 1. Формат годового курса на 35 учебных часов, раскиданных на учебный год по часу в неделю

-

От физики к дискретным элементам

-

Что такое ток, напряжение и сопротивление. Как устроена макетная плата. Упражнение: первая схема с батарейкой, светодиодом и резистором. Зачем включать резистор в цепь со светодиодом. Чтение маркировки резисторов. Переменные резисторы, фоторезисторы.

-

Что такое транзистор. Обзор переключающих элементов от реле, радиоламп, дискретных транзисторов до транзисторов на микросхемах. Упражнения с тиристором (SCR — silicon controlled rectifier — нагляднее чем транзистор), биполярным p-n-p и n-p-n транзисторами.

-

Контрольная работа.

-

-

От дискретных элементов к комбинационной логике

-

Булева алгебра и алгебра логики. Операции, выражения, аксиомы и тождества, включая законы де Моргана. Таблицы истинности.

-

Комбинационные логические элементы И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ, ИСКЛЮЧАЮЩЕЕ-ИЛИ (AND, OR, NOT, NAND, NOR, XOR). Как комбинационные элементы строятся из транзисторов. Упражнение: построить AND, NAND или NOR из дискретных элементов.

-

Логические элементы в микросхемах малой степени интеграции. Индивидуальное упражнение: каждому ученику выдается персональная микросхема логики серии CMOS 4000, с техническим описанием от производителя, с задачей нарисовать таблицу истинности, продемонстрировать ее работу и словесно описать функцию. Микросхемы содержат логические элементы AND, OR, XOR, NOR, NAND с различным числом входов. Что такое такое подтягивающие резисторы и зачем они нужны. Добавляем к предыдущему упражнению кнопки и подтягивающие резисторы.

-

Контрольная работа.

-

-

Двоичная арифметика и ее реализация

-

Двоичные числа. Преобразование из двоичных в десятичные числа и наоборот. Операции сложения и умножения. Отрицательные числа и дополнительный код.

-

Реализация полусумматора и полного сумматора с помощью логических элементов. Перенос. Многоразрядный сумматор с последовательным переносом. Упражнение на макетной плате. Упоминание о длинной временной задержке и схемах с более оптимальной задержкой.

-

Использование 4-битного полного сумматора CMOD 4008. Построение из него 8-битного сумматора и схемы вычитания. Домашнее задание для продвинутых студентов: изучить и сделать презентацию о реализации быстрых сумматоров с ускоренным групповым переносом.

-

Контрольная работа.

-

-

Последовательностная логика

-

Построение генератора тактового сигнала на основе микросхемы 555. Изучение влияния конденсаторов и сопротивлений на частоту и длительности высокого и низкого уровней.

Так как в обвязку 555 входят конденсаторы, могут понадобится дополнительные объяснения, что такое конденсаторы, зачем они нужны в обвязке 555 и как они маркируются. Также может быть полезным и вспомогательное упражнение с зарядкой и разрядкой конденсаторов разной емкости.

-

Схемы с внутренним состоянием. Построение RS-защелки из логических элементов NAND. Изучение поведения D-триггера с помощью микросхемы CMOS 4013 и тактового сигнала от 555 с частотой 1 Гц.

-

Последовательностные блоки — счетчик (CMOS 4029) и сдвиговый регистр (4015). Семисегментный индикатор и его драйвер 4511. Упражнения с этими микросхемами.

-

-

Экзамен.

-

От микросхем малой степени интеграции к ПЛИС — комбинационная логика

-

Понятие о ПЛИС (программируемой логической интегральной схеме) — матрице реконфигурируемых логических элементов. Понятие о языке описания аппаратуры Verilog, процедурах синтеза, размещения, трассировки и конфигурации. Упражнение: синтез простейшего комбинационного модуля с конфигурацией ПЛИС на учебной плате.

-

Продолжение изучения языка Verilog. Типы данных, выражения, присваивания. Always-блоки и основные операторы. Упражнение: вывод первых букв своего имени и фамилии на семисегментный индикатор, переключаясь между ними с помощью кнопки.

-

Продолжение изучения языка Verilog. Иерархия модулей. Упражнение: построение мультиплексоров и сумматоров из подмодулей. Домашнее задание для продвинутых студентов: изучить и сделать презентацию о реализации быстрых сумматоров с ускоренным групповым переносом.

-

Моделирование кода на Verilog без ПЛИС. Подмножества языка для реализации схемы и для ее тестирования / верификации. Моделирование временных задержек. Упражнение: создание среды для проверки работы схемы, описанной на языке Verilog. Использование симулятора Icarus Verilog для моделирования и программы GTKWave для просмотра временных диаграмм.

-

Презентация группы продвинутых студентов: реализация быстрых сумматоров с ускоренным групповым переносом, моделирование в них временных задержек и сравнение их с сумматорами с последовательным переносом (количество логических элементов и задержки).

-

Контрольная работа

-

-

Проектирование последовательностной логике на языке Verilog с реализацией на ПЛИС

-

Конструкции языка Verilog, которые порождают D-триггеры по время синтеза. Объяснение правил методологии проектирования на уровне регистровых передач: блокирующие и неблокирующие присваивания в различных always-блоках. Моделирование последовательностных схем на симуляторе Icarus Verilog.

-

Упражнения: реализация D-триггера, счетчика и сдвигового регистра на ПЛИС. Анализ результатов программы статического анализа о максимальной частоте. Демонстрация: использование последовательностной логики для генерации сигналов звуковой частоты и вывода их на динамик.

-

Концепция конечного автомата. Диаграммы изменения состояний. Упражнения: конечные автоматы светофора и кодового замка.

-

Конечные автоматы для протоколов шин. Выбор самостоятельного проекта (со сдачей в конце курса) по интеграции датчиков и других периферийных устройств с платой c ПЛИС. Самостоятельная работа: индивидуальный проект, модифицирующий поведение одного из примеров с последовательностной логикой: счетчика, сдвигового регистра или конечного автомата.

-

Концепция конвейерной обработки. Сравнение конвейерной реализации арифметических блоков, вычисляющих степень и квадратный корень.

-

Контрольная работа.

-

-

Архитектура процессора: вид со стороны программиста, с лабораторными с помощью симулятора RISC-процессора на уровне инструкций, например MARS MIPS.

-

Концепция фон-Нейманновской машины. Введение в ассемблер: команды, операнды, регистры, константы. Арифметические и логические операции. Кодирование инструкций. Упражнение с симулятором процессора на уровне инструкций — MARS MIPS. Простые программы на ассемблере для вычисления выражений.

-

Условные и безусловные переходы, метки, циклы. Пример: вычисление чисел Фибоначчи. Индивидуальное упражнение на основе модификации примера.

-

Концепция адресуемой памяти. Инструкции загрузки и сохранения в память. Конструкции ассемблера для выделения памяти. Упражнение: программа, заполняющая память вычисленными данными. Индивидуальное упражнение на основе модификации примера.

-

Контрольная работа.

-

-

Микроархитектура: строим процессор

-

Реализация на Verilog подмножества архитектуры MIPS с памятью инструкций, с регистрами общего назначения, но без памяти данных. Минимальный набор инструкции, достаточный, чтобы вычислять числа Фибоначчи и целочисленный квадратный корень итеративным способом. Однотактовая микроархитектура. Простейшая среда тестирования с закодированным вручную массивом инструкций.

-

Продолжение 9.1

-

-

Представление студенческих проектов по интеграции с датчиками

-

Экзамен

6. План на будущее номер 2. Формат двухнедельного летнего лагеря

-

Знакомство с макетной платой, сопротивлениями и логическими элементами.

-

Первая схема с батарейкой, светодиодом и резистором. Зачем включать резистор в цепь со светодиодом. Чтение маркировки резисторов.

-

Комбинационные логические элементы. Каждому ученику выдается персональная микросхема логики серии CMOS 4000, с техническим описанием от производителя, с задачей нарисовать таблицу истинности, продемонстрировать ее работу и словесно описать функцию. Микросхемы содержат логические элементы AND, OR, XOR, NOR, NAND с различным числом входов. Входы подключаются к питанию и земле переходниками, и входы и выходы подключаются к светодиодам.

-

Вариант упражнения 2 с кнопками и подтягивающими резисторами, с объяснением их функции.

-

-

Знакомство с двоичной арифметикой

-

Использование 4-битного сумматора на микросхеме CMOD 4008.

Построение 8-битного сумматора из двух 4-битных. -

Построение схемы вычитания используя тождество -a == ~ a + 1

-

-

Знакомство с последовательностной логикой

-

Построение генератора тактового сигнала на основе микросхемы 555. Изучение влияния конденсаторов и сопротивлений на частоту и длительности высокого и низкого уровней.

-

Изучение поведения D-триггера с помощью микросхемы CMOS 4013 и тактового сигнала от 555 с частотой 1 Гц.

-

Использование сдвигового регистра для генерации “бегущих огоньков” на основе микросхемы CMOS 4015.

-

Строим счетчик (CMOS 4029) и подсоединяем к нему семисегментный индикатор через драйвер 4511.

-

-

Знакомство с ПЛИС (программируемой логической интегральной схеме) — матрицей реконфигурируемых логических элементов. Понятие о языке описания аппаратуры Verilog, процедурах синтеза, размещения, трассировки и конфигурации. Типы данных языка Verilog, выражения, присваивания. Always-блоки и основные операторы.

-

Синтез простейшего комбинационного модуля с конфигурацией ПЛИС на учебной плате.

-

Вывод первых букв своего имени и фамилии на семисегментный индикатор, переключаясь между ними с помощью кнопки.

-

Продолжение изучения языка Verilog. Иерархия модулей. Моделирование кода на Verilog без ПЛИС. Подмножества языка для реализации схемы и для ее тестирования / верификации. Моделирование временных задержек.

-

Упражнение: построение мультиплексоров из подмодулей.

-

Создание среды для проверки работы схемы, описанной на языке Verilog. Использование симулятора Icarus Verilog для моделирования, а также программы GTKWave для просмотра временных диаграмм.

-

-

Проектирование последовательностной логике на языке Verilog. Конструкции языка Verilog, которые порождают D-триггеры по время синтеза. Объяснение правил методологии проектирования на уровне регистровых передач: блокирующие и неблокирующие присваивания в различных always-блоках. Моделирование последовательностных схем на симуляторе Icarus Verilog. Анализ результатов программы статического анализа о максимальной частоте.

-

Реализация счетчика на ПЛИС.

-

Реализация сдвигового регистра на ПЛИС.

-

Использование последовательностной логики для генерации сигналов звуковой частоты и вывода их на динамик.

-

Модификация упражнения 2 или упражнения 3 на основе индивидуального задания.

-

-

Концепция конечного автомата. Диаграммы изменения состояний. Конечные автоматы для протоколов шин. Выбор самостоятельного проекта (со сдачей в конце школы) по интеграции датчиков и других периферийных устройств с платой c ПЛИС.

-

Конечный автомат “улыбающаяся улитка”.

-

Конечный автомат кодового замка на основе индивидуального задания.

-

Конечный автомат для работы с датчиком освещения.

-

-

Архитектура процессора: вид вычислительной установки со стороны программиста. Концепция фон-Нейманновской машины. Использование симулятора процессора на уровне инструкций MARS MIPS.

-

Введение в ассемблер: команды, операнды, регистры, константы. Арифметические и логические операции. Кодирование инструкций. Простые программы для вычисления выражений.

-

Условные и безусловные переходы, метки, циклы. Программа вычисляющая числа Фибоначчи.

-

Концепция адресуемой памяти. Инструкции загрузки и сохранения в память. Конструкции ассемблера для выделения памяти. Программа, заполняющая память вычисленными данными. Индивидуальное упражнение на основе модификации примера.

-

-

Микроархитектура: строим процессор.

-

Реализация на Verilog подмножества архитектуры MIPS с памятью инструкций, с регистрами общего назначения, но без памяти данных. Минимальный набор инструкции, достаточный, чтобы вычислять числа Фибоначчи и целочисленный квадратный корень итеративным способом. Однотактовая микроархитектура. Простейшая среда тестирования с закодированным вручную массивом инструкций.

-

Больше о процессорах.

-

-

Работа над индивидуальным проектом

-

Сдача индивидуального проекта

Приложение A. Что такое язык описания аппаратуры Verilogи как он связан с проектированием микросхем

Из поста на Geektimes Оруженосцы микроэлектроники. Видеорепортаж с конференции по проектированию электроники в Сан-Франциско.

В последние 25 лет дизайн микросхемы чаще всего пишется на языке описания аппаратуры Verilog (в Европе и у военных — VHDL), после чего специальная программа (logic synthesis) превращает дизайн в граф из проводов и логических примитивов, другая программа (static timing analysis) сообщает дизайнеру, вписывается ли он в бюджет скорости, а третья программа (place-and-route) раскладывает этот дизайн по площадке микросхемы.

Когда дизайн проходит все этапы: кодирование на верилоге, отладка, верификация, синтез, static timing analysis, floorplanning, place-n-route, parasitics extraction и т.д. — получается файл под названием GDSII, который отправляют на фабрику, и фабрика выпекает микросхемы. Самые известные фабрики этого типа принадлежат компании Taiwan Semiconductor Manufacturing Company или TSMC.

Приложение B. Что такое ПЛИС / FPGA и почему изучение ПЛИС нельзя заменить более глубоким изучением Ардуино или Расберри Пай

Из поста на Хабре Как начать разрабатывать железо, используя ПЛИС — пошаговая инструкция:

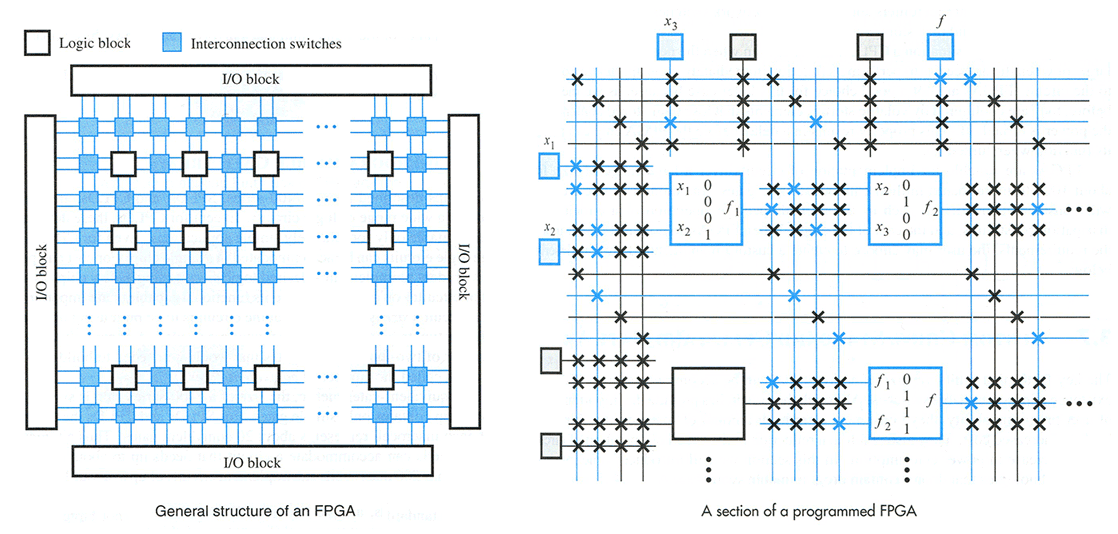

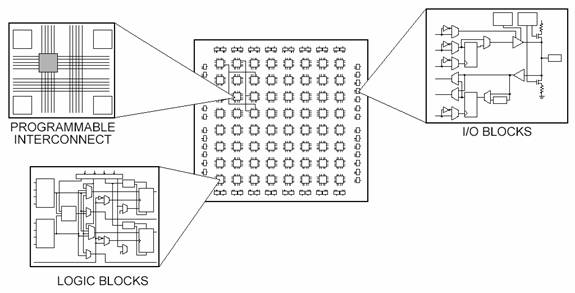

В самом простом варианте FPGA состоит из матрицы однородных ячеек, в функцию каждой из которых можно поменять с помощью мультиплексоров, подсоединенных к битам конфигурационной памяти. Одна ячейка может стать гейтом AND с четырьмя вводами и одним выводом, другая — однобитным регистром и т.д. Загружаем в конфигурационную память последовательность битов из памяти — и в FPGA образуется заданная электронная схема, которая может быть процессором, контроллером дисплея и т.д.

ПЛИС-ы / FPGA — не процессоры, «программируя» ПЛИС (заполняя конфигурационную память ПЛИС-а) вы создаете электронную схему (хардвер), в то время как при программировании процессора (фиксированного хардвера) вы подсовываете ему цепочку написанных в память последовательных инструкций программы (софтвер).

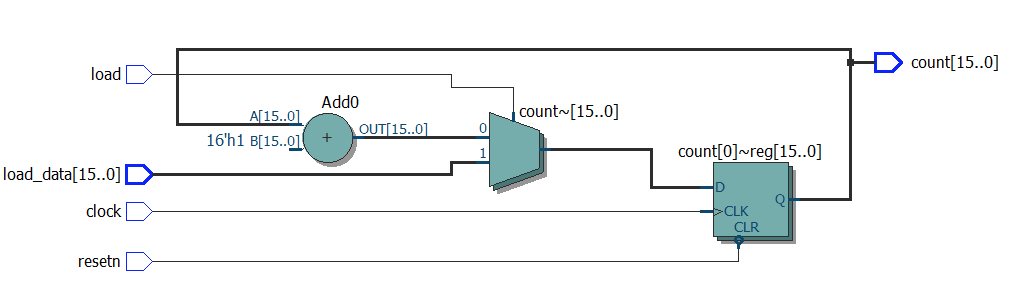

Внизу — схема простейшего блока FPGA, в который входит look-up table (LUT) и flip-flop. Правда в этой схеме не показаны мультиплексоры, которые меняют функцию ячейки, и соединения с конфигурационной памятью.

Диаграммы, иллюстрирующие структуру FPGA:

И еще одна:

Приложение C. Отрывок из заметки про конференции в Томске про то, как образование школьников в данной области привязано к образованию студентов

Системы на кристалле (system on chip, SoC), проектирование высокоинтегрированных микросхем с гетерогенными IP-блоками (CPU, GPU, DSP) — технологическая основа для многих культурных феноменов современного мира, включая смартфоны и быстрый интернет. Значение этой группы технологий еще больше увеличивается с лавинообразным внедрением в автомобильную промышленность чипов для ADAS (advanced driver-assistance systems) и последующим распостранением самоуправляемых автомобилей.

К сожалению, появление ключевых технологий, на которых базируется проектирование систем на кристалле, в мире по времени пришлось аккурат на период коллапса СССР (конец 1980-х — начало 1990-х годов). Западные университеты довольно быстро внедрили в программу обучения языки описания аппаратуры (hardware description languages — HDL), методологию проектирования на уровне регистровых передач (register transfer level — RTL), маршрут проектирования RTL-to-GDSII, превращающий код на языках Verilog и VHDL в геометрическое представление дорожек и транзисторов на кремнии, а также лабораторные работы с использованием реконфигурируемых микросхем FPGA (field-programmable gate arrays). Все эти технологии были внедрены в России гораздо позже, и сейчас их преподавание сконцентрировано в небольшом количестве топ-университетов, таких как МИЭТ в Зеленограде и ИТМО в Санкт-Петербурге. Игнорируется возможность интеграции концепций HDL и RTL в программы физматшкол, где их можно было бы привязать к математической логике, теории конечных автоматов и электричеству, подобно тому, как обогатило советские школьные программы введение в середине 1980-х годов элементов программирования.

Помимо конференции в Томске и планируемого следующего эксперимента в июле а Новосибирске, который поддерживается Новосибирской Летней Школой Юных Программистов, есть еще ранний план организовывать такой эксперимент в Казахстане (этом в частности заинтересована Венера Жаналина посещавшая киевский семинар).

Приложение D. Примеры простейшего кода на Verilog и порождаемые им схемы

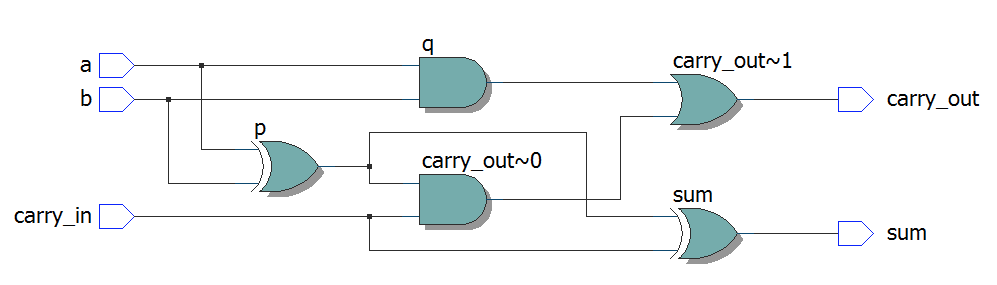

module adder

(

input a,

input b,

input carry_in,

output reg sum,

output reg carry_out

);

reg p, q;

always @*

begin

p = a ^ b;

q = a & b;

sum = p ^ carry_in;

carry_out = q | (p & carry_in);

end

endmodule

module counter

(

input clock,

input resetn,

input load,

input [15:0] load_data,

output reg [15:0] count

);

always @ (posedge clock or negedge resetn)

begin

if (! resetn)

count <= 0;

else if (load)

count <= load_data;

else

count <= count + 1;

end

endmodule

Как оно работает:

Подробное объяснение — в тексте «Введение в дизайн харвера микросхем для тех программистов, которые этим никогда не занимались».

Если вы преподаватель и хотите принять участие в разработке таких материалов (это все на общественных началах, без связи с той или иной компанией), сообщите мне в комментариях. Также интересна любая критика.

Автор: YuriPanchul