Всем привет! В данной статье речь пойдет о подключении микросхем АЦП к кристаллам ПЛИС. Будут рассмотрены основные особенности соединения узлов схем, представлены современные АЦП и их характеристики. В статье будут даны практические советы по быстрому и правильному подключению АЦП к ПЛИС с минимальными временными затратами. Кроме того, речь пойдет о принципах подключения тех или иных АЦП, будет рассмотрен входной буфер ПЛИС и его базовые компоненты – триггеры, узлы задержки IODELAY, сериализаторы ISERDES и т.д. Более детально с примерами программного кода на языке VHDL будет проведен обзор основных элементов, требуемых для качественного приёма данных от АЦП. Это входной буфер, узел упаковки данных для одноканальных и многоканальных систем, модуль синхронизации и передачи данных на базе FIFO, узел программирования АЦП по интерфейсу SPI, узел синтеза частоты данных – MMCM/PLL. Также в статье будет представлен обзор законченных устройств (в стандарте FMC) от ведущих зарубежных и отечественных производителей аналоговых и цифровых схем. В конце статьи вы найдете ссылку на исходные коды универсального узла приёмника данных от многоканальных схем АЦП. Код простой и гибкий в конфигурировании, он представлен на языке VHDL и заточен на микросхемы ПЛИС Xilinx 7 серии и выше, но может быть применен и в других кристаллах ПЛИС.

План статьи

- АЦП (общий обзор, назначение, элементная база)

- Примеры законченных АЦП модулей различных фирм производителей

- Подключение АЦП к ПЛИС. Выбор ПЛИС. Количество контактов, объем логических ресурсов, интерфейс передачи данных

- Входной буфер ПЛИС. Состав, основные узлы. Назначение

- Упаковщик данных для одноканальных и многоканальных схем

- Узел синхронизации данных (FIFO)

- Управление АЦП по SPI интерфейсу (пример)

- Внутренняя шина. Подключение ПЛИС к удаленному устройству

- Исходные коды приёмника данных АЦП

- Список литературы

Аналого-цифровые преобразователи

АЦП применяются для широкого класса задач радиотехники – в любых устройствах, где требуется преобразовать аналоговый сигнал в цифровую форму. Они могут использоваться в аудио- и видео-системах, применяются в задачах гидроакустики и гидросвязи (низкая частота дискретизации, высокая разрядность данных), в устройствах преобразования радиочастотного диапазона (схемы DDC/DUC), в радиолокации и радионавигации (высокие частоты дискретизации, средняя разрядность данных). АЦП применяются в цифровых вольтметрах и мультиметрах, в платах видеовхода компьютеров, видеокамерах, системах распознавания речи и звуковых устройствах. Быстрые АЦП используются в осциллографах и спектроанализаторах, применяются в лабораторном оборудовании и медицинской технике. Очень часто АЦП используется в задачах сбора и обработки данных на высоких скоростях.

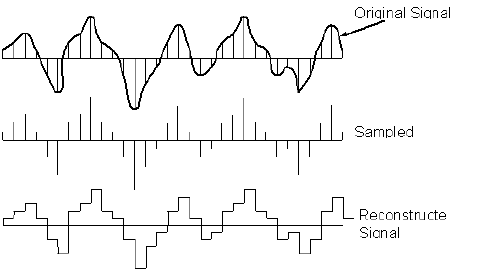

Как видно, микросхемы АЦП – неотъемлемая часть аналого-цифровых устройств. В современном мире очень непросто найти устройство, в котором бы отсутствовали АЦП. Классический вид АЦП представлен на следующем рисунке.

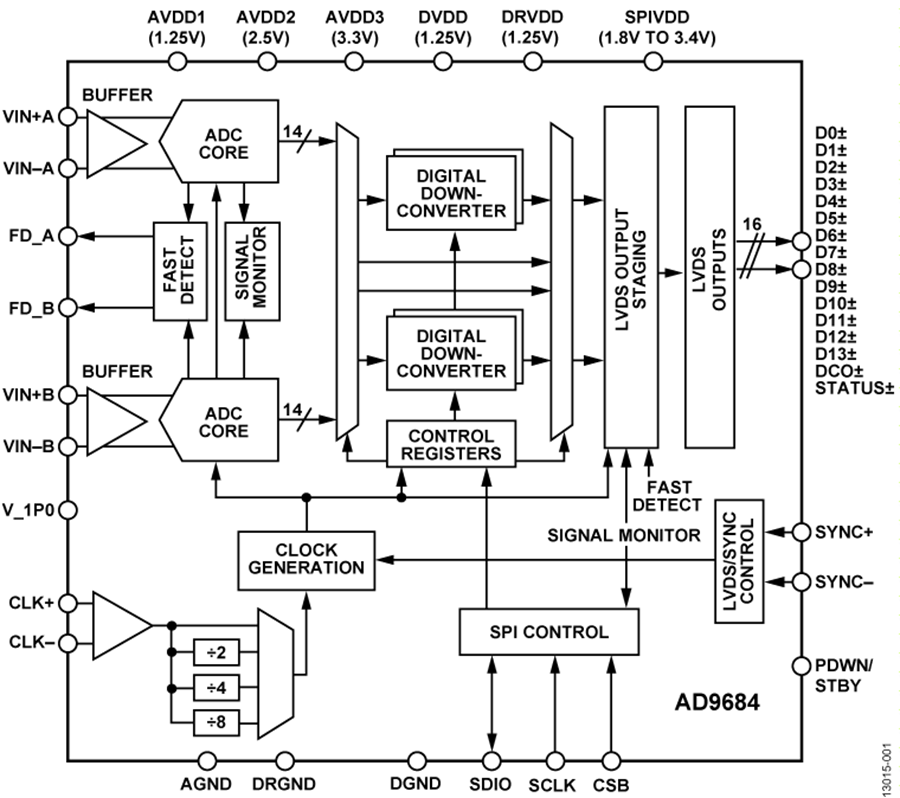

Это упрощенная схема, взятая из даташита на микросхему AD9684. Она содержит два дифференциальных аналоговых входа VINA и VINB, вход тактовой частоты CLK, управление по интерфейсу SPI, выходную шину в параллельной форме D0-D13, точки напряжения питания различных узлов микросхемы, блок синхронизации SYNC и другие управляющие сигналы.

Очевидно, что микросхемы АЦП характеризуется набором определенных параметров, от которых зависит конечный выбор пользователя и который определяет область применения АЦП. По цифровой части – это скорость передачи данных (эффективная тактовая частота), которая может находиться в диапазоне от нескольких десятков кГц до нескольких ГГц. Разрядность данных на выходе АЦП – в современных устройствах от 8 до 32 бит данных. Со стороны аналоговых характеристик – это отношение сигнал-шум (SNR) и динамический диапазон, свободный от паразитных составляющих (SFDR), выражаемые, как правило, в децибелах (типовые уровни SNR лежат в пределах 70-80 дБ, а уровни SFDR в районе 90 дБ). Немаловажными параметрами при выборе АЦП являются – рассеиваемая мощность (Вт), количество каналов в одном корпусе, интерфейс обмена с цифровым узлом и, разумеется, стоимость компонента.

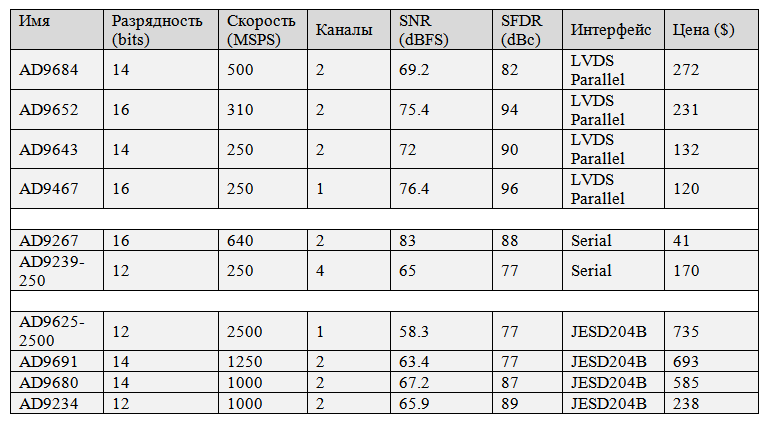

Рассмотрим современные быстродействующие АЦП и их характеристики на примере таблицы, взятой с известного сайта Analog Devices – гиганта в области производства всевозможных микросхем АЦП и ЦАП. В таблицу для удобства сведены самые важные характеристики микросхем, они разделены по типу интерфейса обмена с цифровым устройством и выстроены по скорости передачи информации (тактовой частоте) от большего значения к меньшему.

В таблице представлены 4 топовые микросхемы, передающие данные в параллельной форме по стандарту LVDS. Разрядность данных 14-16, каналов 1-2, максимальная частота дискретизации 500МГц. Средние значения SNR и SFDR – 70 dBFS и 90 dBc, соответственно. Для некоторых микросхем с последовательной шиной передачи данных (Serial) характеристики практически схожие. Для современных микросхем АЦП, которые используют интерфейс передачи JESD204B и подключаются к ПЛИС через гигабитные линии, тактовые частоты значительно выше, но аналоговые характеристики несколько хуже (по меньшей мере из-за того, что разрядность цифровых данных ниже – 12 и 14 бит). В данной статье не будет рассматриваться подключение АЦП к кристаллам FPGA через гигабитные линии. Я остановлюсь на простом и хорошо изученном варианте подключения микросхем – последовательная и параллельная шина с интерфейсами передачи данных типа LVTTL, LVDS, LVCMOS, LVPECL. В частности, интересен способ передачи данных по LVDS шине, который отличается простотой трассировки печатных плат, дешевизной исполнения, низким уровнем помех и рассеиваемой мощности, а также высокой скоростью передачи данных. Для приема данных по последовательной шине в ПЛИС используются сериалайзеры / десериалайзеры. Для параллельной шины все намного проще и данные принимаются как есть.

В ходе работы по сопряжению аналоговых и цифровых устройств мне приходилось осваивать следующие микросхемы АЦП. Это уже устаревшие, но всё еще используемые – AD9224, AD6644ST-65, AD9244, LCT2207, ADS5474, AD9432BST-105, AD7475BR, микросхемы современного уровня – AD9430BSV, ADS54RF, AD9467, ADC12D1800, AD9680 и другие. Поскольку область моей работы лишь частично связана с аналоговой схемотехникой, я вряд ли расскажу вам о способах улучшениях характеристик законченных аналого-цифровых модулей. Также я не смогу дать советы по качественному построению аналоговых трактов и методике выбора тех или иных компонентов схемы для достижения наилучших аналоговых показателей (SNR, SFDR). Но на вопросы подключения АЦП к кристаллам FPGA и дальнейшей обработки данных я постараюсь ответить в рамках данной статьи.

Примеры модулей АЦП

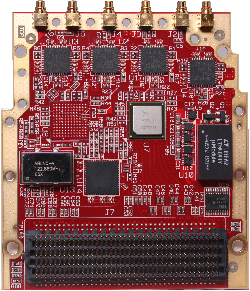

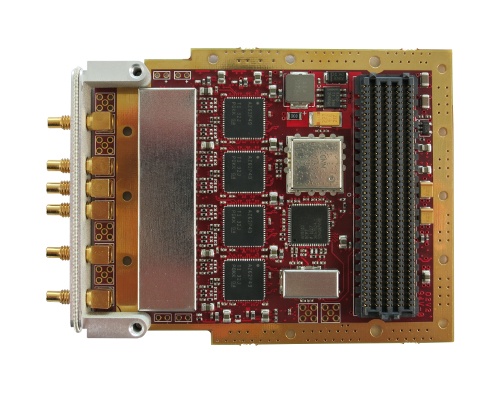

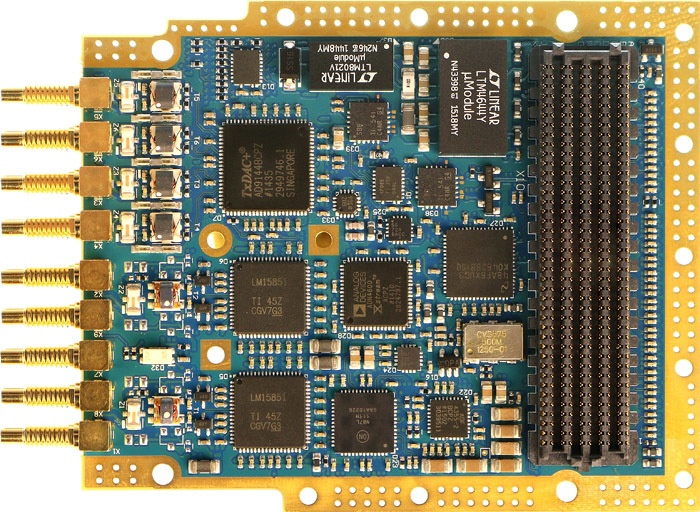

На следующих рисунках будут представлены современные примеры законченных и качественных модулей аналого-цифрового преобразования данных от российских и зарубежных производителей. Все они имеют один или несколько аналоговых входов подключения и разъем-переходник FMC (FPGA Mezzanine Card) для подключения к несущей плате, на которой устанавливается обработчик данных (как правило, это FPGA). FMC – это один из основных стандартов для подключение изделий по модульной архитектуре. На мезонинный модуль (mezzanine board) зачастую устанавливается аналоговая часть, а на несущий модуль (carier board) устанавливается центральное устройство, осуществляющее обработку данных – это одна или несколько ПЛИС и/или сигнальные процессоры. Из зарубежных производителей устройств следует выделить две лидирующие фирмы-производителя – это 4dsp и hitechglobal. Из отечественных производителей гугл в первых строках поиска выдает ЗАО «Скан инжиниринг Телеком», ЗАО «Инструментальные системы» и другие. Автор статьи не несет ответственности за представленные модули и не использует статью в целях рекламы продукта той или иной фирмы.

HTG-ADC16. Обладает следующими характеристиками (взяты с официального сайта):

- 16-Bit Resolution, Dual-Chanel, 1-GSPS ADC

- Noise Floor: –159 dBFS/Hz

- Spectral Performance (fIN = 170 MHz at –1 dBFS):

- SNR: 70 dBFS

- SFDR: 86 dBc

- SFDR: 96 dBc (Except HD2, HD3, and Interleaving Tones)

- Spectral Performance (fIN = 350 MHz at –1 dBFS):

- SNR: 67.5 dBFS

- NSD: –154.5 dBFS/Hz

- SFDR: 75 dBc

- SFDR: 85 dBc (Except HD2, HD3, and Interleaving Tones)

- Channel Isolation: 100 dBc at fIN = 170 MHz

- Input Full-Scale: 1.9 VPP

- Input Bandwidth (3 dB): 700 MHz

- On-Chip Dither

- Integrated Wideband DDC Block

- JESD204B Interface with Subclass 1 Support:

- 2 Lanes per ADC at 10.0 Gbps

- 4 Lanes per ADC at 5.0 Gbps

- Support for Multi-Chip Synchronization

- Power Dissipation: 1.35 W/ch at 1 GSPS

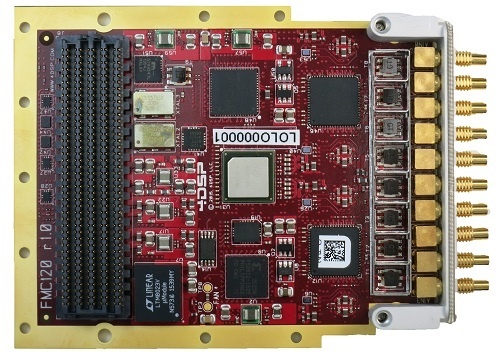

FMC104: 4-Channel 250 MSPS @ 14-bit. Характеристики (некоторые удалены за избыточностью информации):

- Four Channel 14-bit 250 MSPS A/D conversion

- Available as air cooled and conduction cooled

- VITA 57.1-2010 compliant

- Based on TI ADS62P49

- LVDS or 1.8V LVCMOS output operation

- Single ended AC- or DC-coupled analog input

- Flexible clock tree enables

- LPC (low-pin count) compatible

Особенность модуля – четыре канала АЦП, напряжение питания 1.8В (используются HP-банки FPGA Xilinx).

FMC120: 4-Channel 250 MSPS @ 14-bit. Характеристики:

- Quad — A/D — D/A Channel Operation

- Quad Channels 16-bit 1.00 GSPS A/D

- Quad Channels 16-bit 1.25 GSPS D/A

- Simultaneous sampling on all channels up to 1 GSPS

- VITA 57.1-2010 compliant

- Conduction Cooled – Standard Option

- Single ended DC or AC-coupled analog input.

- Clock Source, Sampling Frequency, and Calibration through an SPI communication bus

- HPC – High Pin Count Connector

- 2Kbit EEPROM (24LC02B) accessible from the Host via I2C bus

- JTAG – CPLD device is included in the JTAG chain accessible from the FMC connection

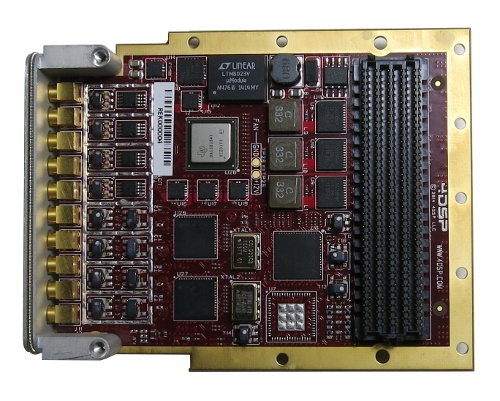

FMC140: 4-channel 16-bit 370MSPS A/D. Обладает следующими характеристиками:

- Four-channel, 16-bit A/D up to 370 MSPS

- VITA 57.1-2010 compliant

- JESD204B serial interface

- AC or DC-coupled analog signals

- Clock source, sampling frequency, and calibration through SPI communication busses

- Flexible clock tree enables

- Power-down modes to switch off unused functions for system power savings

- HPC — High Pin Count connector

Особенность модуля – 4 высокоскоростных канала АЦП, разрядность данных 16 бит, обмен по интерфейсу JESB204B.

Модуль SFM-4A1000. Характеристики:

- Четыре канала АЦП: 14 бит 1000 МГц

- Широкополосный трасформаторный вход с полосой до 2 ГГц

- Интерфейс с несущим модулем JESD204B

- Поддержка встроенных в АЦП функций цифровой децимации и АРУ

- Высокостабильный опорный генератор, вход внешнего опорного тактирования

- Программное управление настройками АЦП и схемой тактирования

- Форм-фактор FMC одиночной ширины с воздушным или кондуктивным охлаждением

Особенность модуля – отечественная разработка, 4 высокоскоростных канала АЦП, полоса 2ГГц, обмен по интерфейсу JESB204B.

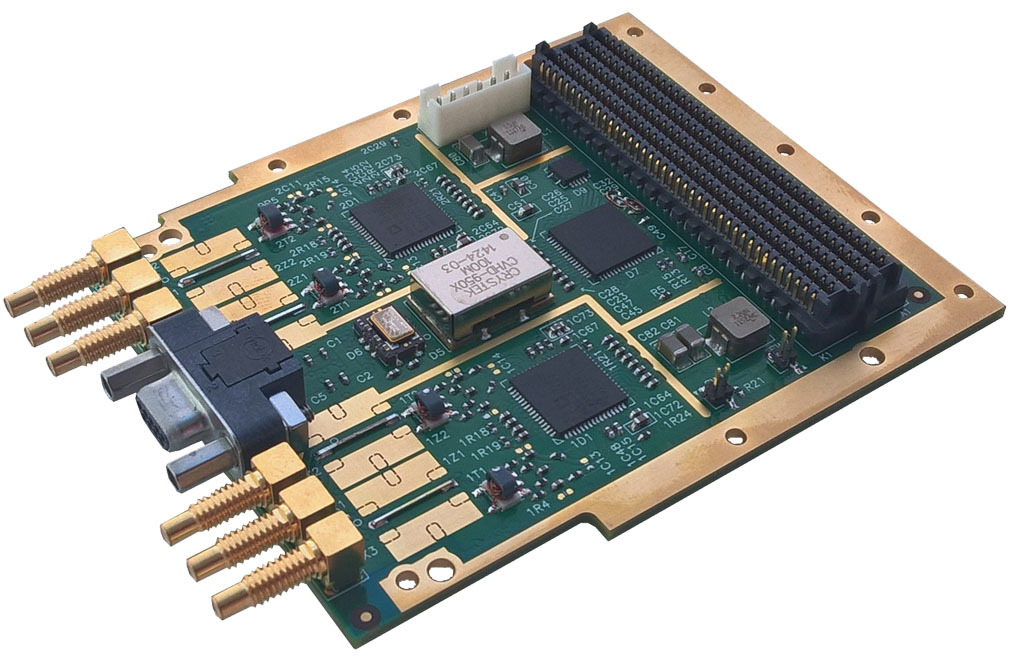

Модуль FMC212x4GDA. Характеристики:

- Два канала АЦП 12 бит

- Частота преобразования: от 1 до 4 GSPS

- Аналоговая входная полоса: от 5 до 2000 МГц

- Входное сопротивление: 50 Ом

- DDC, встроенный в АЦП

- Максимальная ширина полосы DDC: 800 МГц

- Коэффициент децимации DDC: от 4 до 32

- Четыре канала ЦАП 16 бит 2,8 GSPS

- Интерполяция: х2, х4, х8

- Частотный диапазон выходных сигналов ЦАП: от 0,5 до 400 МГц

- Максимальная амплитуда выходного сигнала: ±0,5 В

- Выходное сопротивление: 50 Ом

- Синтезатор тактовых частот АЦП и ЦАП с низким фазовым шумом

- ANSI/VITA 57.1 FMC модуль 69x76,5 мм

Особенность модуля – 2 высокоскоростных канала АЦП, полоса сигнала до 2ГГц, обмен по интерфейсу JESB204B, встроенные микросхемы DDC, 4 канала ЦАП.

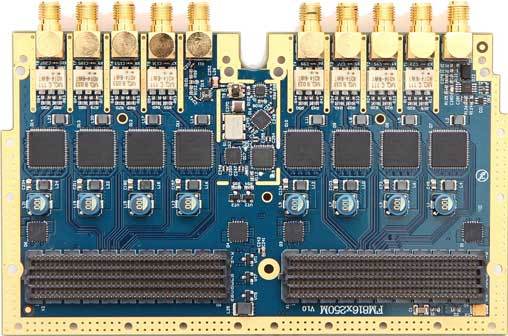

Модуль FMC816x250M. Характеристики:

- ANSI/VITA 57.1 FMC модуль двойной ширины 139x76.5мм

- 8 АЦП 16 бит

- Частота преобразования: от 50 МГц до 250 МГц

- Аналоговая входная полоса 0,1…250МГц

- Шкалы преобразования: ±0,8В; ±0,65В

- Входное сопротивление: 50 Ом

- Внутреннее/внешнее тактирование

- Перестраиваемый тактовый генератор 10…250МГц

Особенность модуля – 8 каналов АЦП, сдвоенный модуль.

Как видно, многие из модулей аналого-цифрового преобразования в стандарте FMC похожи и обладают практически идентичными характеристиками, которые определяются установленными микросхемами АЦП и ЦАП. Окончательный выбор того или иного модуля определяется задачей, которую требуется решить конечному пользователю.

Подключение АЦП к ПЛИС

Перейдем к основному разделу статьи – подключение микросхем АЦП к кристаллам ПЛИС. Рассмотрим подключение АЦП по параллельной и последовательной шине, с интерфейсами передачи данных – LVTTL, LVCMOS, LVDS. В статье не будет рассмотрено подключение АЦП по интерфейсу JESD204B, поскольку это материал отдельной темы, который займет не одну полноценную статью. Кроме того, JESD204B существенно отличается в реализации от «классических» вариантов подключения микросхем АЦП и требует более детального рассмотрения.

Как известно, банки (группы пинов) ввода/вывода ПЛИС могут конфигурироваться на различное напряжение питания, границы которого определяются производителем кристаллов. В современных ПЛИС типа Xilinx диапазон подаваемых напряжений зависит от типа банка. Существует два основных типа банка (Xilinx) – HP (высокопроизводительные) и HR (банки с большим числом пинов). Например, в микросхемах 7 серии Xilinx диапазон напряжений для банков HR – от 1.2 до 3.3В, а для банков HP – от 1.2 до 1.8В. Помимо этого, пины банков могут программироваться на широкий диапазон стандартных интерфейсов передачи данных, но конечный выбор стандарта определяется двумя правилами: напряжение питания банка ПЛИС и способ подключения удаленного устройства и ПЛИС. С другой стороны, немаловажным фактором выбора напряжения питания банка ПЛИС является семейство кристаллов. Так, для Kintex-7 возможно использовать стандарт LVDS 25 и питать банк напряжением 2.5В, а для многих микросхем ПЛИС Virtex-7 стандарт подключения исключительно LVDS 18, и банк запитывается напряжением 1.8В. В связи с этим, возникает проблема сопряжения некоторых аналоговых модулей и несущих плат с разными семействами ПЛИС. Поэтому при покупке у стороннего производителя модуля АЦП и/или несущей платы нужно убедиться, что они совместимы по стандарту и напряжению питания. Как правило, интерфейс передачи данных прописывается в файле ограничений (UCF или XDC), а не в исходных кодах проекта, что обеспечивает гибкость конфигурации и повторное использование файлов исходных кодов в других проектах.

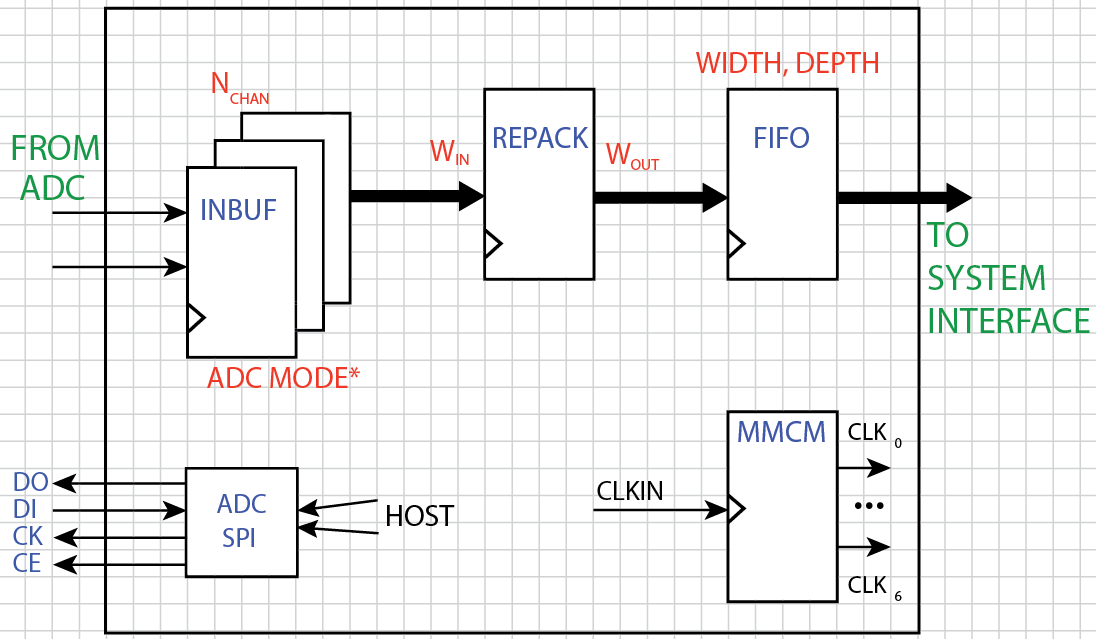

Структурная схема файла верхнего уровня проекта (а также внутренних блоков, используемых для приёма данных от микросхем АЦП по стандарту LVTTL / LVCMOS / LVDS) представлена на следующем рисунке.

Она включает следующие элементы:

- Входной приемник

- Упаковщик данных

- Синхронизатор потока данных (FIFO)

- Блок управления микросхемами АЦП

Помимо этих узлов, на верхнем уровне используется модуль синтеза частоты на основе MMCM – стандартный ресурс ПЛИС. Также для управления задержками в узлах IODELAY применяется компонент IDELAYCTRL.

Основные параметры файла верхнего уровня, от которых зависит конфигурация схемы в ПЛИС:

- NCHAN — количество независимых каналов АЦП,

- DATA_WIDTH — разрядность данных АЦП,

- FIFO_ADDR — глубина FIFO: DEPTH = 2**ADDR,

- DATA_RATE — режим приёма данных: SDR / DDR,

- PACK_OUT — ширина выходной шины упаковщика (системная шина),

- CLK_SEL — выбор основного источника тактовой частоты для многоканальной схемы,

- USE_MMCM — использование узла MMCM вместо BUFR для деления частоты CLKDIV на SERDES,

- DIFF_TERM — использование дифференциальных входных сигналов (TRUE/FALSE),

- IOSTANDARD — стандарт напряжения для LVDS линий,

- DATA_IOBDELAY_TYPE — режим работы узла задержки IODELAY,

- DATA_IOBDELAY_VALUE — значение задержки по умолчанию,

- DIFF_CLOCK — использование дифференциального тактового сигнала на входе (TRUE/FALSE),

- OVR_PRES — использование линий переполнения АЦП (overflow),

- STR_PRES — использование линий сигнала внешнего старта АЦП (start),

- RESYNC_OUT — включение механизма первичной пересинхронизации данных на входном буфере (YES/NO).

И некоторые другие параметры.

Часть код файла верхнего уровня приёмника АЦП выглядит примерно следующим образом:

xFIFO: CTRL_FIFO_CONFIG

generic map (

DATA_WIDTH => PACK_OUT,

ADDR_WIDTH => FIFO_ADDR

)

port map (

reset => reset,

wr_clk => clk_pack,

rd_clk => sys_clk,

data_i => do_pack,

data_o => do_fifo,

rd_en => cs_fifo,

wr_en => dv_pack,

empty => ef_fifo,

full => ff_fifo

);

Здесь подключается узел FIFO для синхронизации данных с системной шиной устройства. Программирование задержек для IODELAY в многоканальной и многоразрядной схеме буфера выглядит следующим образом:

---- Data delays ----

x_dat_dd <= x_dat_do(conv_integer(unsigned(dl_chan))) when rising_edge(dl_clk);

x_dat_in(conv_integer(unsigned(dl_chan)))(conv_integer(unsigned(dl_muxs))) <= dl_dat_in when rising_edge(dl_clk);

x_dat_ce(conv_integer(unsigned(dl_chan)))(conv_integer(unsigned(dl_muxs))) <= dl_dat_ce when rising_edge(dl_clk);

x_dat_ld(conv_integer(unsigned(dl_chan)))(conv_integer(unsigned(dl_muxs))) <= dl_dat_ld when rising_edge(dl_clk);

Где dl_chan — выбранный канал АЦП, dl_muxs — выбранный разряд АЦП. Это сделано для независимого программирования каждого бита данных.

Рассмотрим каждый узел детально.

Замечание: для подключения ПЛИС и ЦАП (цифро-аналоговых преобразователей) ситуация зеркальна. Необходимо сделать все тоже самое, но в обратном порядке. В рамках данной статьи подключение ПЛИС к ЦАП не рассматривается.

Входной приемник

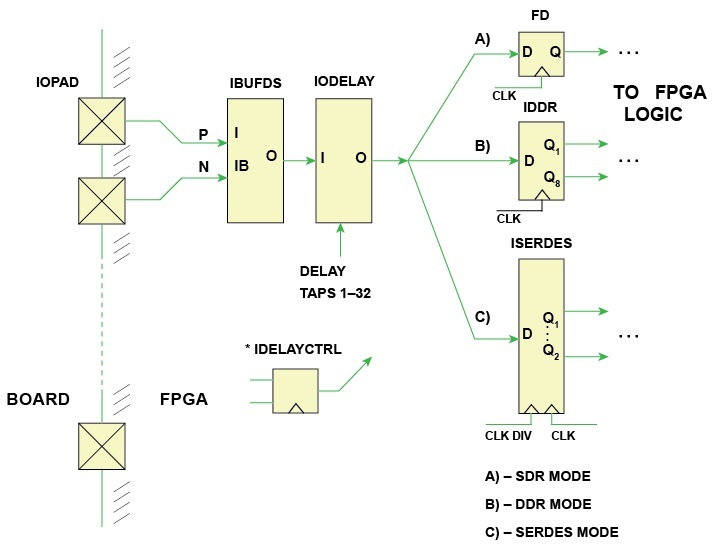

Содержит первичные элементы подключения между внешними сигналами печатной платы и логикой ПЛИС. Это буфер IPAD от контакта ПЛИС к логике входного буфера IOBUF. В зависимости от интерфейса передачи данных буфер может быть дифференциальный – IBUFDS и однополярный – IBUF. Для многих буферов возможна жесткая привязка к требуемому стандарту, либо возможна установка типа выходного сигнала через атрибуты. Например, для IBUFDS с помощью атрибута IOSTANDARD можно заранее в исходных кодах определить и задать стандарт «LVDS_25».

Следом за буфером устанавливается узел регулирования задержки прохождения сигнала IODELAY для выравнивания фронтов параллельной шины данных и первичного согласования многоканальных узлов подключения АЦП к ПЛИС. IODELAY – программируемый ресурс ПЛИС, величина задержки может быть фиксирована и определяться установкой по умолчанию, либо программироваться в диапазоне от 0 до 31 условных величин времени (цифра определяется даташитом на микросхему ПЛИС). Программирование осуществляется примитивным образом с помощью нескольких сигналов. Останавливаться на детальном разборе алгоритма программирования не будем, за дополнительной информацией можно обратиться к документу из списка литературы в конце статьи. Для узлов IODELAY необходимо подключать специальный узел контроля задержек IDELAYCTRL, который в режиме реального времени калибрует задержки для каждого тактового региона ПЛИС. Для устранения влияния температуры кристалла, напряжения питания и загруженности ПЛИС, узел IDELAYCTRL тактируется независимым сигналом REFCLK. Этот тактовый сигнал обеспечивает равную величину задержки (TAP) во всех узлах IODELAY каждого тактового региона ПЛИС. Если в каждом тактовом регионе необходимы свои величины подстройки – в кристалле ПЛИС инициализируются несколько узлов IDELAYCTRL. Тактовый сигнал REFCLK может подаваться с внешнего генератора, установленного вне ПЛИС, либо может быть получен путем синтеза частоты в узле MMCM кристалла ПЛИС.

Следом за узлом задержки IODELAY возможна установка FD триггера, если режим передачи данных DATA_RATE = «SDR». Этот триггер опционально помещается во входной буфер и тактируется частотой АЦП, сопровождающей данные с аналогового модуля. В режиме DATA_RATE = «DDR» триггер заменяется на усложненный вариант IDDR, который имеет один вход данных и два выхода. С выхода возможна выдача данных в нескольких режимах, но на практике я использовал только один – это «SAME_EDGE_PIPELINED», при котором данные с выхода Q1 и Q2 выдаются по одному и тому же фронту тактового сигнала.

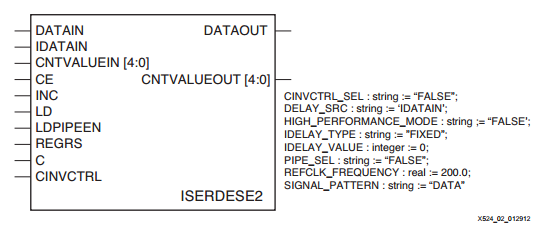

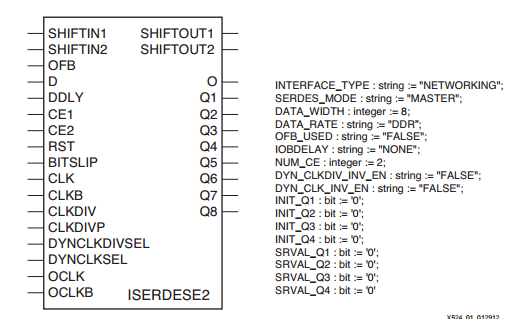

Ну и наконец, самый интересный вариант – это подключение узла IODELAY к модулю десериализации данных ISERDES. Узел сериалайзера – сложный элемент входного буфера ПЛИС, он содержит следующие опции:

- DATA_RATE – определяет режим выходных данных (SDR/DDR),

- DATA_WIDTH – определяет разрядность шины данных на выходе узла (от 1 до 8),

- INTERFACE_TYPE – тип интерфейса передачи данных. Для подключения микросхем АЦП используется режим «NETWORKING».

- SERDES_MODE – режим подключения ISERDES в случае использования нескольких сериалайзеров для приема данных от одного контакта ПЛИС.

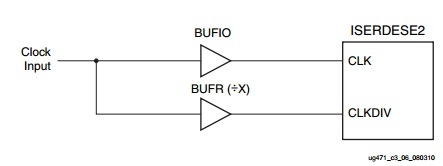

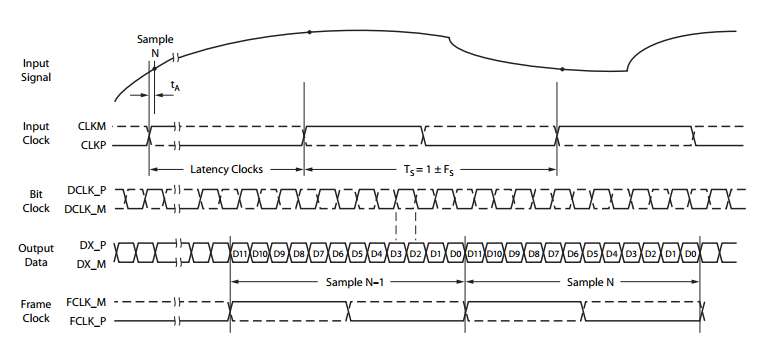

Тактирование узла осуществляется несколькими сигналами – это сигнал на высокой частоте принимаемых данных CLK и сигнал CLKDIV, деленный на число, определяемое параметром DATA_WIDTH. Деление может происходить вне ПЛИС, но на практике используются синтезаторы частоты в самом кристалле ПЛИС, которые носят название MMCM. Таким образом, на вход узла ISERDES поступает последовательный сигнал на частоте CLK, а на выходе узла ISERDES получается параллельный поток данных на сниженной частоте CLKDIV = CLK / DATA_WIDTH. Тактовую частоту можно поделить с помощью регионального буфера BUFR, значение коэффициента деления BUFR_DIVIDE = 1-8, или на узле синтезатора частоты MMCM, программируемого в широком диапазоне.

Для устранения эффекта совпадения фронта тактовой частоты и данных не всегда хватает узлов IODELAY и подстройки частоты в MMCM. Зачастую приходится искать альтернативные пути решения этой проблемы. К счастью, это решение было найдено моим коллегой, о чем он недавно рассказал в своей статье (Полезные свойства джиттера).

Все перечисленные выше узлы (за исключением MMCM) входят в состав входного буфера ПЛИС и не занимают логических ресурсов кристалла. С выхода FD / IDDR / ISERDES данные поступают уже на логические элементы – это триггер или FIFO небольшого размера для первичной пересинхронизации данных на частоту, полученную после прохождения частоты дискретизации АЦП в узле MMCM. В некоторых случаях пересинхронизация не используется, а данные синхронизируются напрямую частотой дискретизации АЦП. На следующем рисунке приведена временная диаграмма обработки последовательных данных с микросхемы АЦП на устройстве ISERDES. Показана входная тактовая частота, последовательная форма входных данных и преобразованные данные в параллельный код.

Таким образом, в зависимости от конфигурации, во входном буфере возможно три пути прохождения сигнала, как показано на рисунке:

A) режим SDR — данные принимаются по параллельной шине, для каждого бита данных используется свой буфер ПЛИС,

B) режим DDR — данные принимаются по параллельной шине, данные тактируются удвоенной частотой.

C) режим SERDES — данные принимаются по последовательной шине

Упаковщик данных

Этот узел используется в одноканальных и многоканальных схемах приема данных от АЦП. Основное его назначение – упаковать данные в удобный формат внутренней шины, используемый внутри ПЛИС. Разрядность внутренней шины определяется разработчиком или корпоративным стандартом. Типовые значения разрядности на выходе упаковщика – 32, 64, 128, 256, 512 бит данных. В некоторых случаях упаковщик не может быть сконфигурирован. Это зависит от количества входных каналов, разрядности входной и выходной шины данных упаковщика. Например, для четырехканального источника с разрядностью входных данных = 16 бит невозможно организовать перепаковщик с выходной шиной разрядностью менее WOUT = WIN * NCHAN = 16 * 4 = 64 бит. Для одноканального источника данных с той же разрядностью на входе и выходе данные будут последовательно упакованы пачками по 16 бит в разрядную сетки 64 бита. То есть первый отсчет АЦП займет битовое поле [15:0], второй отсчет – [31:16], третий – [47:32], а четвертый – [63:48]. Далее отсчеты циклически будут занимать битовые поля от младшего к старшему в выходной сетке данных. Другой пример. Используется 2 канала данных, разрядности на входе и выходе остаются те же самые – 16 и 64 бит соответственно. Если система сбора данных на удаленном устройстве включает только один канал, то упаковка происходит, как показано в примере выше, причем неважно, какой из каналов включен. Если система сбора включает оба канала, то данные упаковываются попарно от младшей части разрядной сетки к старшей. Первый отсчет первого канала займет позицию [15:0], первый отсчет второго канала займет позицию [31:16], второй отсчет первого канала – [47:32], второй отсчет второго канала – [63:48]. Как показала практика, это самый удобный вариант упаковки данных при многоканальной обработке, в случае отключения тех или иных каналов передачи. Замечание: количество каналов должно быть кратно степени двойки – 1, 2, 4, 8 и т.д. Может показаться, что этот узел – сложный в реализации и понимании, но после нескольких применений в своих проектах вы найдете для себя, что ничего сложного и необычного здесь нет.

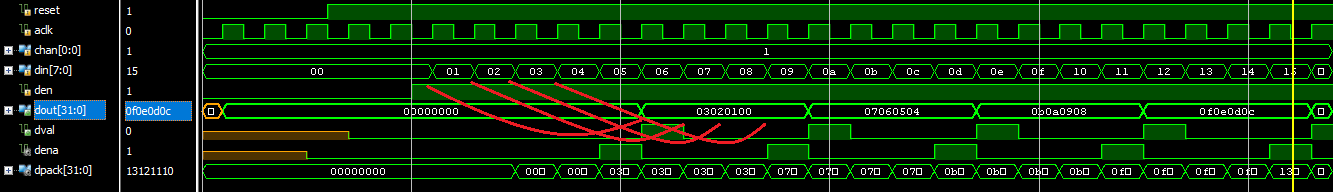

На следующем рисунке приведены временные диаграммы работы узла упаковщика данных в режиме: NCHAN = 1, WIN = 8, WOUT = 32.

Красными линиями показан процесс упаковки данных на выходную шину, которая сопровождается сигналом разрешения DVAL = 1 после приёма 4 отсчетов данных.

Синхронизатор потока данных

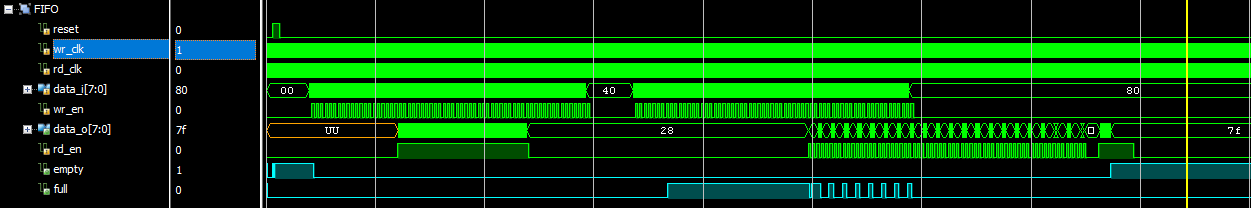

Этот узел строится на базе примитивной схемы FIFO и имеет одно важное и простое назначение – преобразование потока данных с частоты дискретизации CLK_ADC на частоту обработки или частоту работы внутренней шины устройства SYS_CLK (системная тактовая частота). Для простоты можно создать узел FIFO в Xilinx Core Generator, но в идеале лучше написать свой модуль, который будет гибок в конфигурации на произвольную ширину шины (FIFO_WIDTH) и глубину памяти (FIFO_DEPTH). На следующем рисунке приведены временные диаграммы работы узла FIFO, показаны входные и выходные данные, а также флаги пустого (empty) и полного (full) FIFO. Следует отметить, что для нормальной работы FIFO АЦП флаг заполненности FULL должен быть всегда равен 0, что говорит о правильности принятия данных от АЦП и отсутствии переполнения. Если флаг FULL = 1, то скорость приема данных удаленным обработчиком недостаточна, либо скорость работы АЦП слишком велика для выбранной системы.

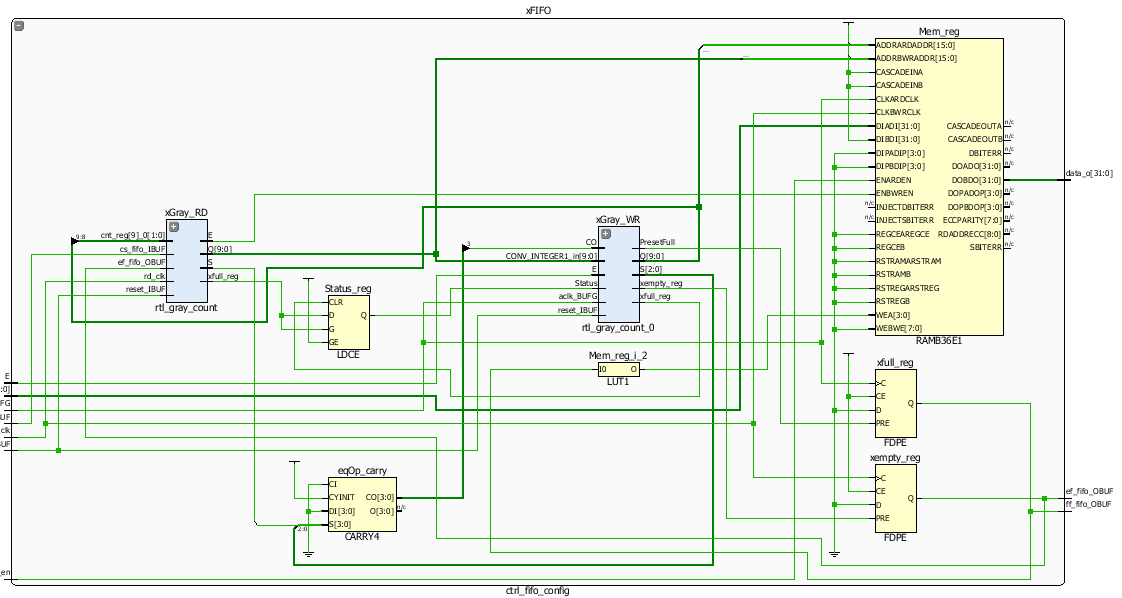

На следующем рисунке изображено схематическое представление узла FIFO в среде Plan Ahead.

Видно, что FIFO строится на базе двухпортовой памяти. На шины адреса памяти отправляются данные в коде Грея — на схеме это два узла для чтения и записи. Это позволяет снизить битовую ошибку на высоких частотах, т.к. соседние значения в коде Грея отличаются всего лишь одной битовой позицией. Логика флагов FIFO определяется значениями в модулях счетчика Грея, а для увеличения тактовой частоты узла на выходе используются регистры.

Внутренняя шина

Возникает вопрос — а куда дальше идут собранные и упакованные данные? Ответ прост: с помощью интерфейсов PCI / PCIe, USB, Ethernet, SRIO, SATA данные достигают конечной цели, где проходят последующую обработку и где осуществляется сбор всей информации. До этого звена внутри ПЛИС может находиться узел цифровой обработки сигналов (DSP), например — DDC, DUC, FFT / IFFT и т. д. Кроме того, данные могут буферизироваться на внешней памяти большого объема, типа DDR3 / DDR4. Это частый приём, который применяется для обработки большого потока информации на высоких скоростях. В данном случае внешняя память имитирует FIFO большого размера. Для соединения ПЛИС с внешней памятью применяются специальные контроллеры, которые, как правило, доступны и открыты для использования. В случае Xilinx они находятся в IP Core Generator.

Помимо прочего, разработчику необходимо создать собственный конечный автомат управления всеми ресурсами приёмника АЦП: это конфигурация задержек в IODELAY, программирование синтезатора частоты MMCM, передача команд по SPI на АЦП и ЦАП модули, управление началом и концом сбора данных с АЦП, управление количеством активных каналов, использование внешней памяти DDR и многое другое. У всех это своя уникальная архитектура, но базовые принципы остаются одинаковыми. На фирме, в которой я работаю, используются узлы управления под названием "тетрады". Подробно о них рассказывал мой коллега здесь.

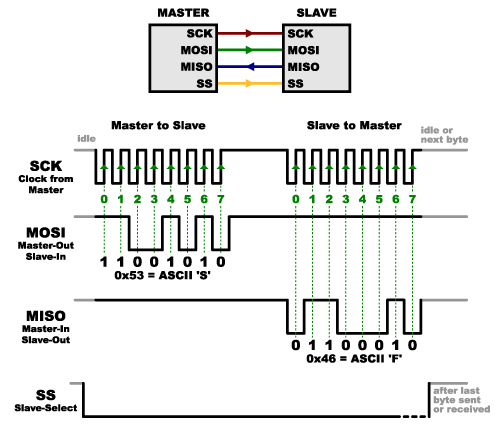

Управление модулем АЦП

Как правило, управление аналоговым модулем осуществляется через SPI-подобные интерфейсы. Реализовать SPI-интерфейс под силу любому студенту старшего курса, в программе которого есть изучение программируемой логики и ПЛИС. Заострять внимание на узле SPI я не буду. В конце статьи в качестве примера приведен исходный код управления удаленной микросхемой HI-6131, которая обрабатывает сообщения в формате MIL-STD-1553. Код не параметризируемый и заточен конкретно на выбранную микросхему. Для разминки вы можете написать свой узел SPI, который будет конфигурироваться на разные параметры. Временная диаграмма управления по SPI-интерфейсу имеет следующий вид:

Исходный код

Исходный код всех компонентов и узлов представлен на языке VHDL и предназначен для микросхем FPGA Xilinx 7 серии (и выше). Исходные коды открыты для использования и доступны по ссылке на гитхабе — см. здесь. Все компоненты по возможности сделаны гибкими в конфигурации и не требуют существенного вмешательства в исходный код (за исключением узла SPI — простите, было лень). К сожалению, невозможно подстроиться под все существующие решения, но данный пример успешно отработал для всех аналоговых модулей, с которыми я работал.

Например, операции чтения и записи в FIFO, а также подключение узлов преобразования двоичного кода в код Грея выглядит следующим образом:

---- Read data ----

pr_rd: process(rd_clk) begin

if (rising_edge(rd_clk)) then

if (rd_en = '1' and xempty = '0') then

data_o <= Mem(conv_integer(pNextWordToRead));

end if;

end if;

end process;

---- Write data ----

pr_wr: process (wr_clk) begin

if (rising_edge(wr_clk)) then

if (wr_en = '1' and xfull = '0') then

Mem(conv_integer(pNextWordToWrite)) <= data_i;

end if;

end if;

end process;

---- Gray counters ----

xGray_WR : rtl_gray_count

generic map ( COUNTER_WIDTH => ADDR_WIDTH )

port map (

cnt => pNextWordToWrite,

ena => NextWriteAddressEn,

rst => reset,

clk => wr_clk

);

xGray_RD : rtl_gray_count

generic map ( COUNTER_WIDTH => ADDR_WIDTH )

port map (

cnt => pNextWordToRead,

ena => NextReadAddressEn,

rst => reset,

clk => rd_clk

);

Список литературы

- 7 Series FPGAs Overview (DS180) (xilinx.com)

- Xilinx 7 Series Libraries Guide for Schematic Designs (xilinx.com)

- 7 Series FPGAs SelectIO Resources User Guide (UG471) (xilinx.com)

- 7 Series FPGAs Clocking Resources User Guide (UG472) (xilinx.com)

- Serial LVDS High-Speed ADC Interface (xilinx.com)

- Analog for Xilinx ® FPGAs Selection Guide (ti.com)

- HSC-ADC-FPGA High Speed Deserialization (analog.com)

- Interfacing Analog to Digital Converters to FPGAs (latticesemi.com)

и т.д.

Продолжение следует...

Автор: capitanov