Резерв повышения степени интеграции путем уменьшения технологических норм близок к исчерпанию. Дальнейший прогресс в этой области может быть связан с внедрением объемной компоновки. Пока она применяется ограниченно, например, в микросхемах памяти HBM, где логический чип находится в одной стопке с несколькими чипами памяти.

На открывшейся сегодня конференции IEEE 3DIC давно занимающаяся технологией объемной компоновки компания Tezzaron Semiconductor и ее дочернее производственное предприятие Novati Technologies на представили первую в мире восьмислойную микросхему, в которой объединены логические чипы.

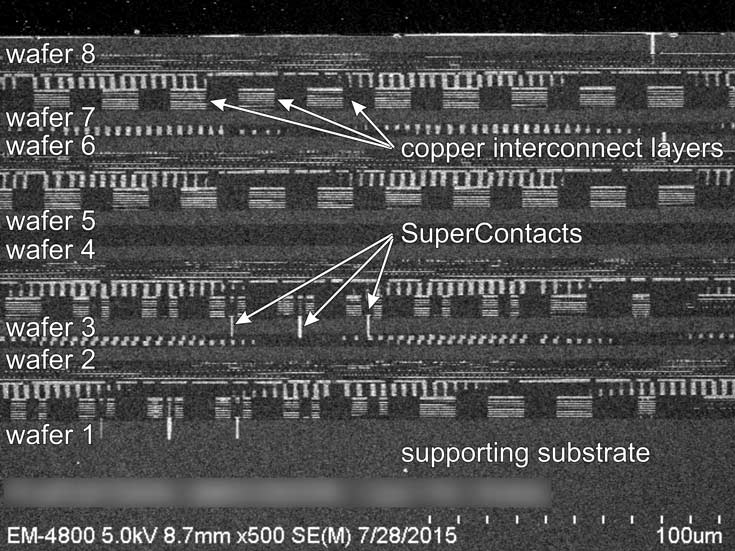

Эта микросхема имеет наибольшую на сегодняшний день плотность компоновки. Каждая пластина с высокопроизводительной логической схемой CMOS содержит десять слоев медных внутренних соединений, так что суммарное число слоев транзисторов равно восьми, а соединений — 80. При этом итоговый стек по толщине не отличается от обычного кристалла, поскольку толщина каждого слоя — всего 20 мкм.

Для соединения чипов между собой используется технология DBI, разработанная компанией Ziptronix и лицензированная Tessera для использования в производстве. Производитель отмечает, что имеет место настоящая трехмерная компоновка, без использования проводных соединений, шариковых выводов и прочих черт интеграции на уровне упаковки. Чипы соединены непосредственно друг с другом, что существенно улучшает электрические, механические и термические показатели микросхемы.

Малая толщина слоев позволяет использовать прямые вольфрамовые соединения SuperContacts диаметром 1,2 мкм, а не медные, используемые в TSV. Поскольку соединения SuperContacts можно располагать с шагом 2,4 мкм, и для них не требуется выделять зоны без транзисторов поблизости, плотность соединений может превышать 170 тысяч на квадратный миллиметр. Это в 350 раз больше лучшего показателя TSV.

В Novati Technologies подчеркивают, что речь идет не о лабораторной разработке, а о технологии, освоенной на производстве.