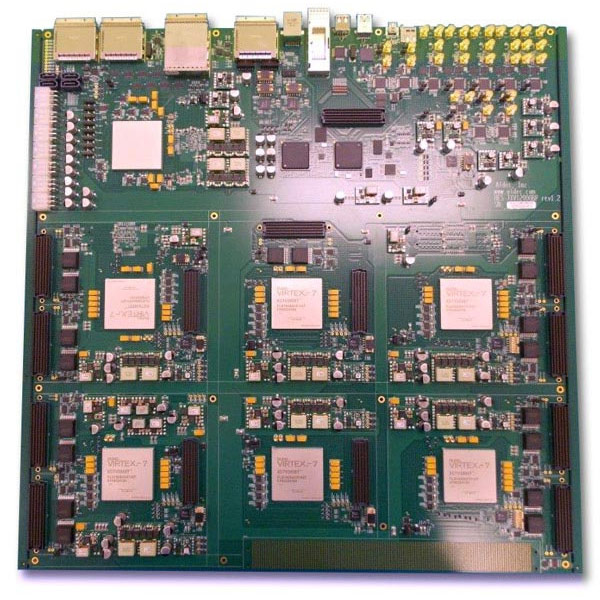

Компания Aldec, предлагающая решения для разработчиков электронных систем, включая специализированные интегральные схемы (ASIC), представила крупнейшую в отрасли систему для создания прототипов микросхем с использованием программируемой вентильной матрицы (FPGA) Xilinx Virtex-7. Ее возможности оцениваются в 288 млн вентилей ASIC. Ключевым компонентом системы является плата, получившая обозначение HES-7 (HES7VX12000BP), на которой находятся шесть FPGA Xilinx Virtex-7 2000T в корпусах FLG1925. Это 72 млн вентилей ASIC. Возможность объединения до четырех плат HES-7 с помощью объединительной платы Aldec Backplane (HES7-BPx4) позволяет увеличить суммарное число вентилей до 288 млн.

На плате HES-7 есть девять разъемов для плат FMC (FPGA Mezzanine Card) с 648 парами выводов для дифференциальных сигналов. Для внешних подключений есть 977 пар для дифференциальных сигналов в дополнение к общей шине, используемой в целях отладки. Оснащение платы включает высокоскоростные интерфейсы, такие, как Gigabit Ethernet и 40 GbE (QSFP+), USB3.0 и PCIe x16/x8, подключенные к управляющей FPGA Xilinx Virtex-7 690T.

По словам производителя, HES-7 можно использовать в рамках традиционной методики изготовления прототипов, предусматривающей программирование FPGA и конфигурирование платы с помощью специального ПО. В то же время, HES-7 обладает уникальной возможностью — плата может служить аппаратной платформой для передовых режимов верификации, доступных в среде разработки Aldec HES-DVM.

Источник: Aldec