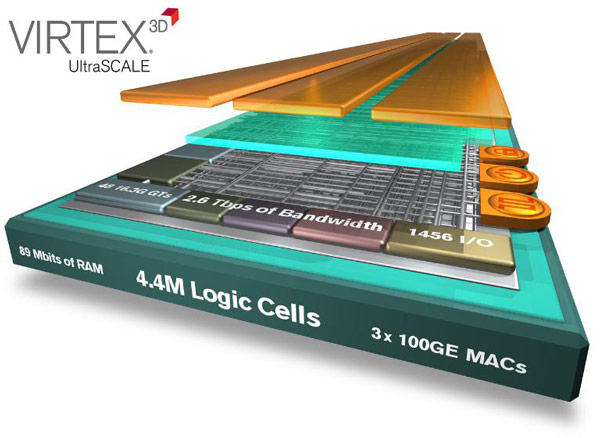

Компания Xilinx, специализирующаяся на FPGA, объявила о выпуске изделия с рекордно большим количеством логических ячеек — 4,4 млн. Это более чем вдвое превосходит прежний рекорд, принадлежавший FPGA Virtex-7 2000T. По словам производителя, новые FPGA Virtex UltraScale на целое поколение опережают изделия конкурентов.

Микросхема Virtex UltraScale VU440 с объемной компоновкой выпускается по нормам 20 нм. За счет объемной компоновки удалось получить более высокую плотность, чем заявлена конкурентами для продукции, которую планируется выпускать по нормам 14 или 16 нм.

По подсчетам Xilinx, возможности Virtex UltraScale VU440 соответствуют ASIC с 50 млн. логических вентилей. Программируемые логические матрицы Virtex UltraScale предназначены для разработки прототипов высокопроизводительных микросхем. Они позволяют реализовать средствами одного кристалла блоки MuxSAR, Transponder и MAC-Interlaken с пропускной способностью 400 Гбит/с.

В числе достоинств Virtex UltraScale производитель отмечает «архитектуру класса ASIC», обеспечивающую высокий уровень масштабируемости и утилизации блоков — за счет технологии проектирования топологии нового поколения ее удается довести до 90%. Кроме того, механизмы синхронизации, управления питанием и внутренних соединений, используемые в Virtex UltraScale, подобны тем, что используются в ASIC. В FPGA интегрированы приемопередатчики с пропускной способностью 33 Гбит/с, а также IP-ядра Ethernet MAC 100 Гбит/с и Interlaken 150 Гбит/с.

Матрицы Xilinx UltraScale поддерживаются средой разработки Vivado Design Suite 2013.4. Поставки ознакомительных образцов Virtex UltraScale должны начаться в первой половине 2014 года.

Источник: Xilinx