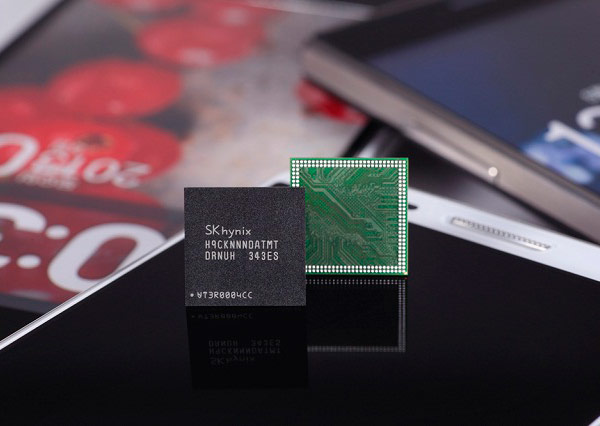

Компания SK Hynix объявила о разработке микросхем памяти LPDDR3 (Low Power DDR3) плотностью 6 Гбит, рассчитанных на выпуск по технологии 20-нанометрового класса. Эта память предназначена для мобильных устройств верхнего сегмента, поскольку в ней объединено малое энергопотребление и высокая плотность. Она рассчитана на напряжение питания 1,2 В.

Четыре чипа LPDDR3 плотностью 6 Гбит можно компоновать в стопку, получая 3 ГБ оперативной памяти. При этом потребляемая мощность у такого решения будет примерно на 30% меньше, чем у собираемого сейчас из чипов плотностью 4 Гбит. Производитель отмечает, что по высоте сборки получаются одинаковыми.

Память поддерживает скорость 1866 Мбит/с по одной линии. Это означает, что один 32-разрядный контроллер памяти позволит ежесекундно передавать по шине до 7,4 ГБ данных, а двухканальный — до 14,8 ГБ. Новая память будет доступна в виде самостоятельных изделий или компонентов для компоновки PoP (Package on Package). Ознакомительные образцы уже доступны. Массовый выпуск стартует в начале будущего года.

Источник: SK Hynix