В начале 2020-го года в сети появляется новость о том, что РЖД собирается купить 15 тысяч компьютеров на базе процессоров Эльбрус, потратив на это около 1 млрд руб. Никого не смущает, что тендер заявлен на пятое февраля 20-го года, а конечная дата поставки 25 мая того же года, - кто работал с МЦСТ, тот поймет почему срок нереальный, партии процессоров там "копеечные" и ждать надо долго пока наберут заказов.

7 февраля 2020 года в СМИ пишут об отмене ФАС тендера по жалобе некоей компании "Смарт текнолоджис". Причиной отмены явилось то, что "заявитель настаивал на неправомерности установления заказчиком в документации требований к техническим и функциональным характеристикам товара, «указывающим на конкретного производителя товара АО “МЦСТ”". Вся общественность, которая лояльно относится к импортозамещению начинает проклинать ФАС. ФАС демонизируется чуть ли не как главный враг отечественной электроники. Люди находят и другие решения по которым ФАС отменяет закупки отечественной продукции.

14 февраля того же года РБК пишет новость о том, что производители электроники в лице некоей ассоциации «Консорциум дизайн-центров и предприятий радиоэлектронной промышленности» обратились к вице-премьеру Юрию Борисову с просьбой о расширении для них преференций при закупках их продукции госкомпаниями. Сама статья ни о чем, классический плач отечественного бизнеса на тему «дайте преференций, запретите», но в статье есть комментарий заместителя руководителя ФАС Михаила Евраева о злополучном тендере: «РЖД имеют полную возможность по закону купить российскую технику, выставив соответствующие требования в неконкурентной закупке», подчеркнул замглавы ФАС. «Вместо этого заказчик проводит конкурентную закупку, включив в нее требования, ограничивающие конкуренцию, понимая при этом, что при поступлении жалобы ФАС такую закупку отменит. Это говорит либо о недостаточной квалификации заказчика, либо о его нежелании покупать российскую продукцию, либо о чем-то еще». Вот это поворот! Оказывается, если сильно хочется, то можно и не проводить фарс в виде тендера, а просто купить их. Истинных причин такого поведения нам скорее всего не удастся узнать, но, как я полагаю, это просто была показательная порка отечественных производителей, мол, смотрите, нам ФАС не дает закупать у вас, отстаньте от нас.

Тем временем, в конце минувшего года, по итогам тестирования серверов на базе процессора Эльбрус 8с «Сбербанк» остался недоволен их производительностью, заявив о катастрофически не выполненных функциональных требованиях. Сбер не раскрыл результатов тестирования производительности, но показатели их «неожиданно и очень приятно удивили» - ожидаемое отставание в 20-30 раз сменилось значениями лишь в несколько раз медленнее западных альтернатив. МЦСТ в своём ответе на комментарии Сбербанка пообещала улучшить показатели «железа» для поколения серверов на базе «Эльбрус-8СВ» и рассказала о планах на будущие поколения серверов.

Разработка микропроцессора Эльбрус 8с была начата в конце 2011 года. За основу был взят дизайн микропроцессора предыдущего поколения Эльбрус 4с с переработанными структурными элементами, включая процессорные ядра, подсистемы памяти и ввода-вывода, иерархии кэш-памяти. Первые инженерные образцы микропроцессора были получены в ноябре 2014-го года, а серийный выпуск начался в 2016-м году.

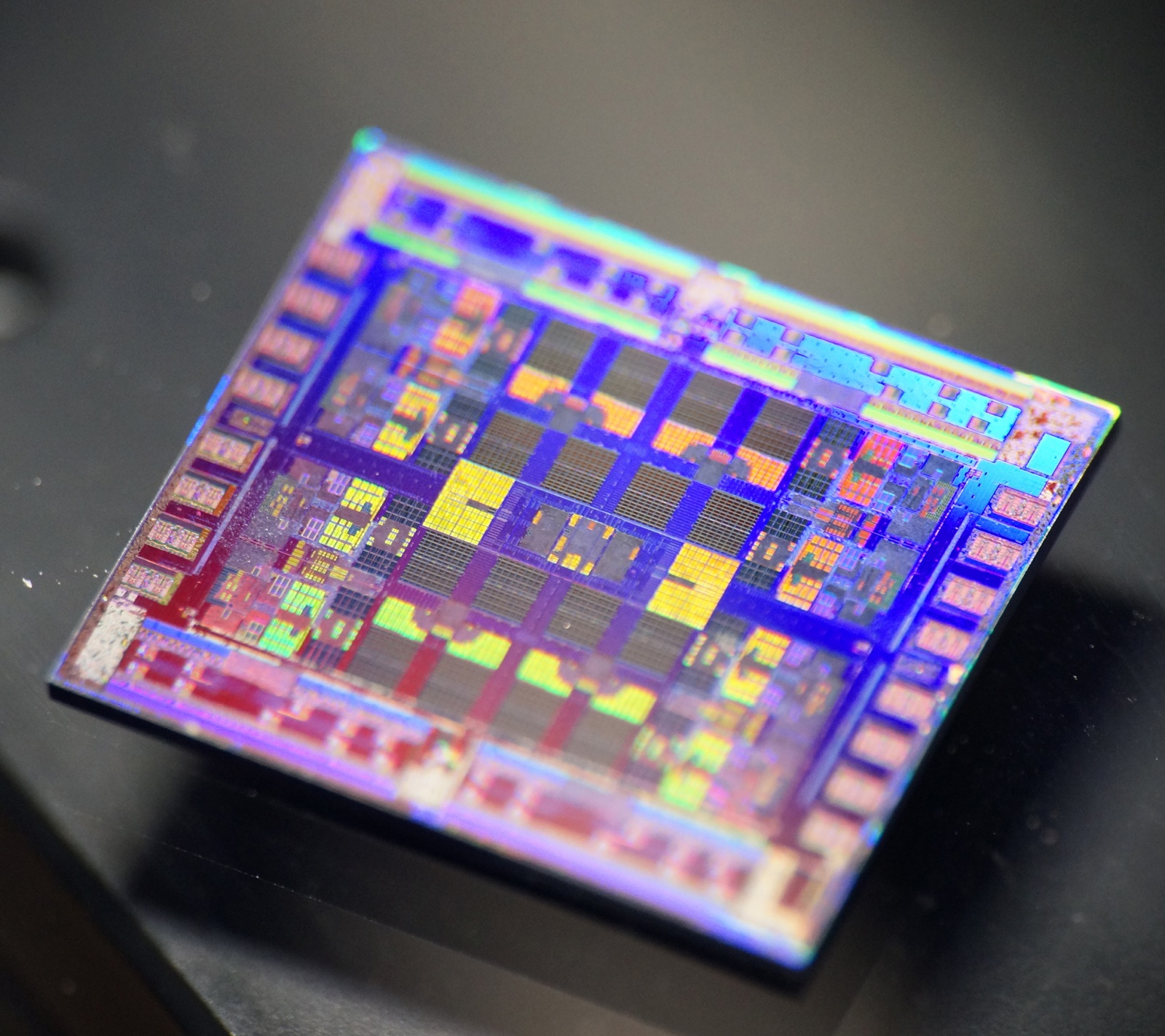

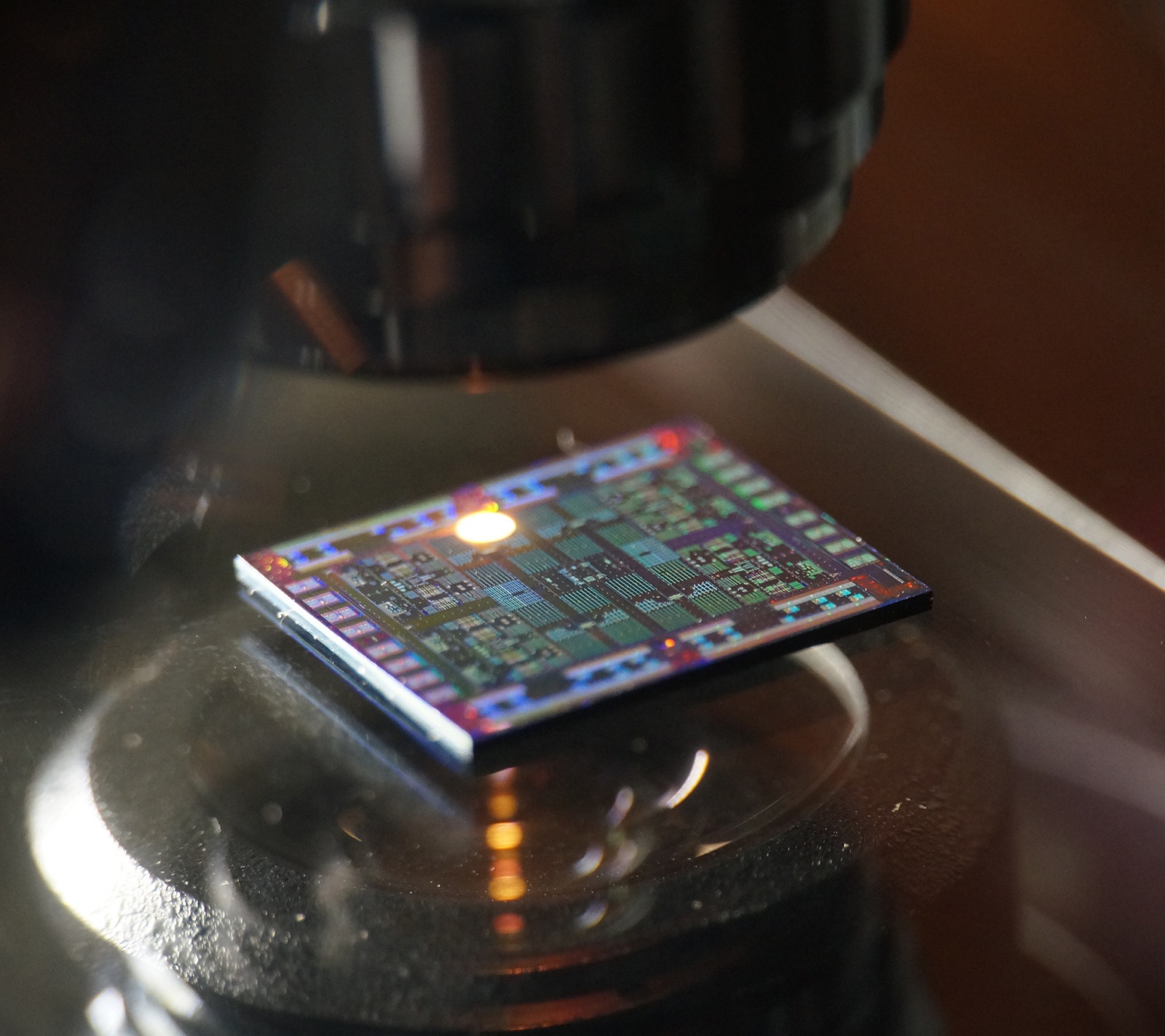

Внутреннее строение

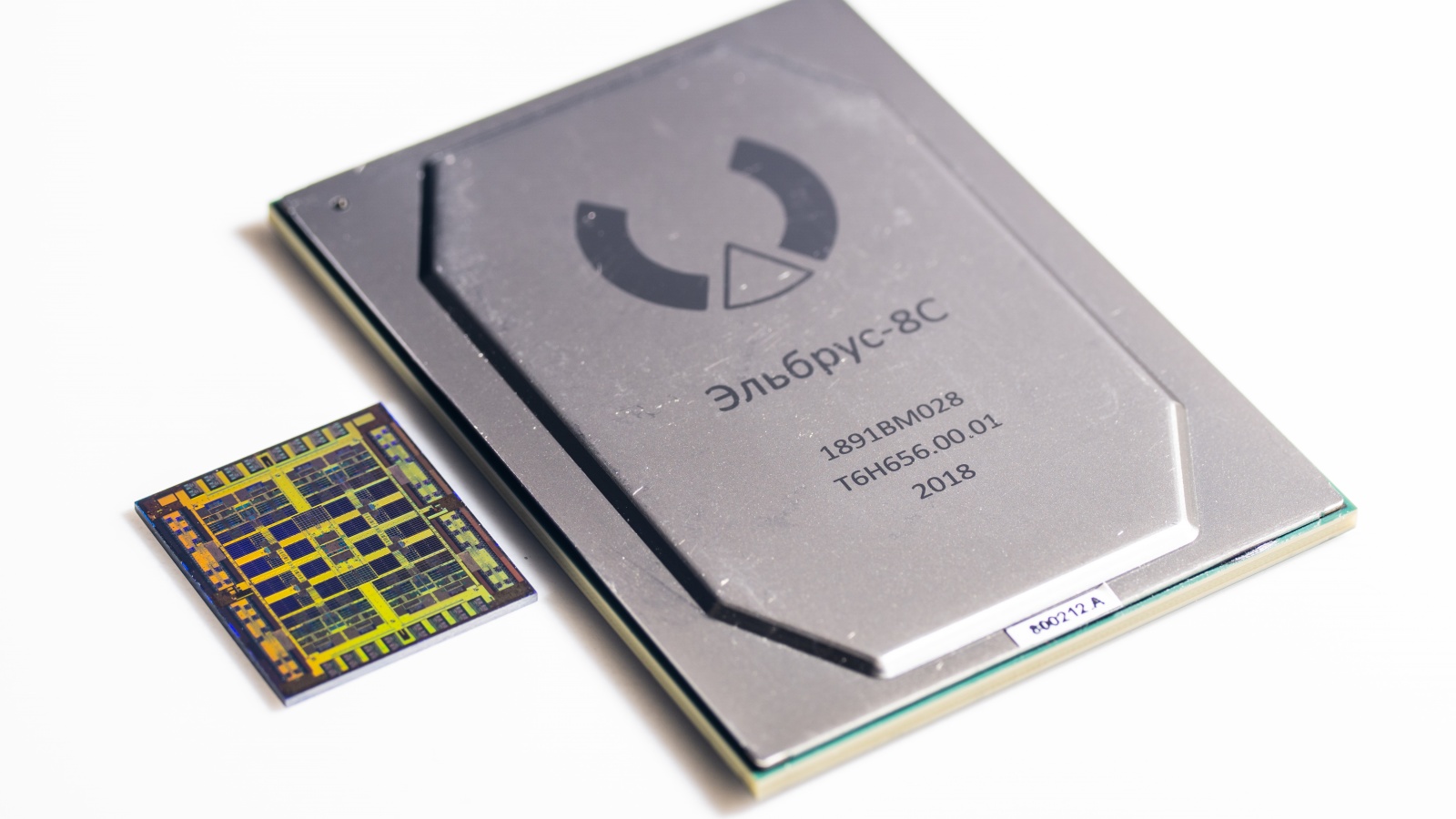

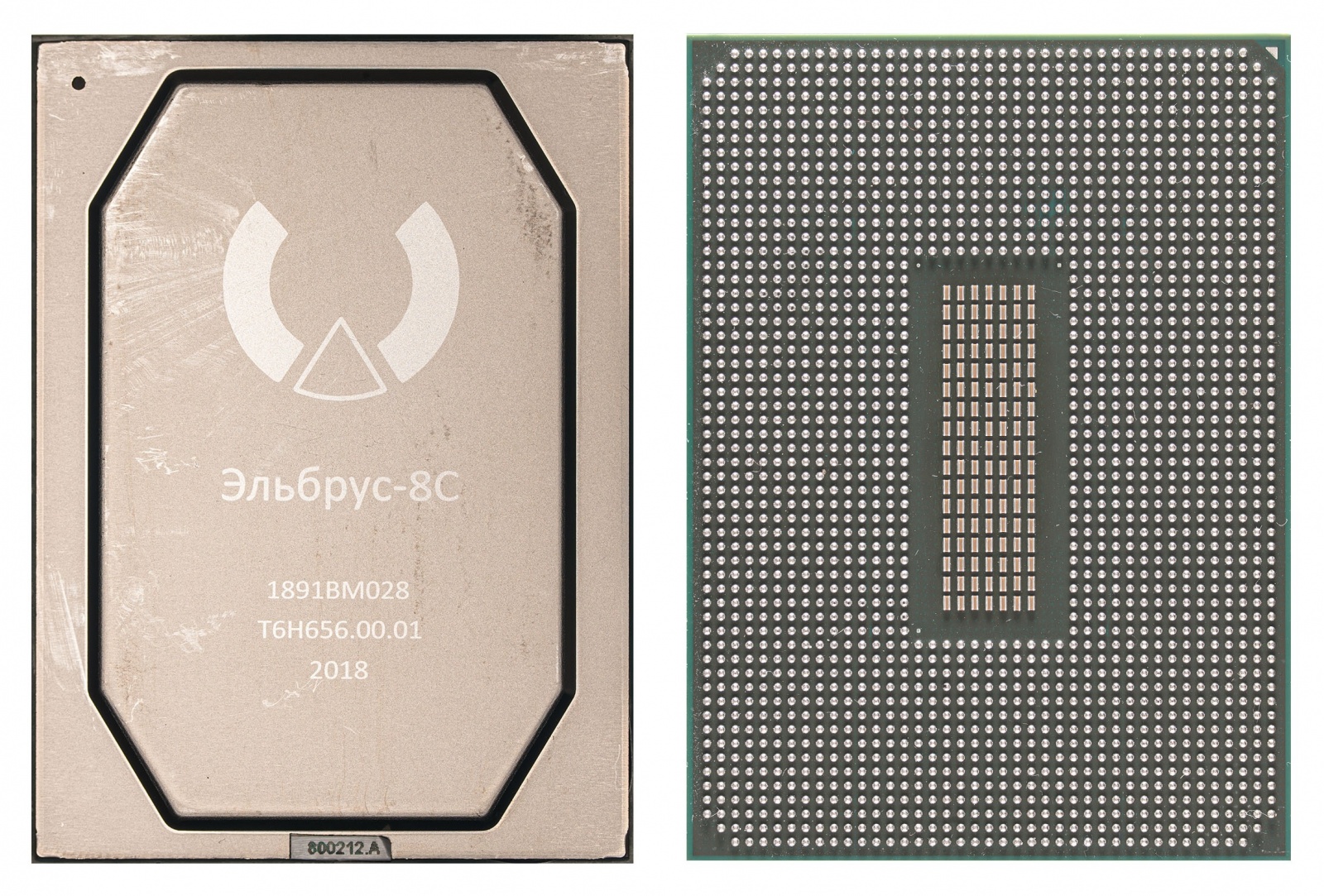

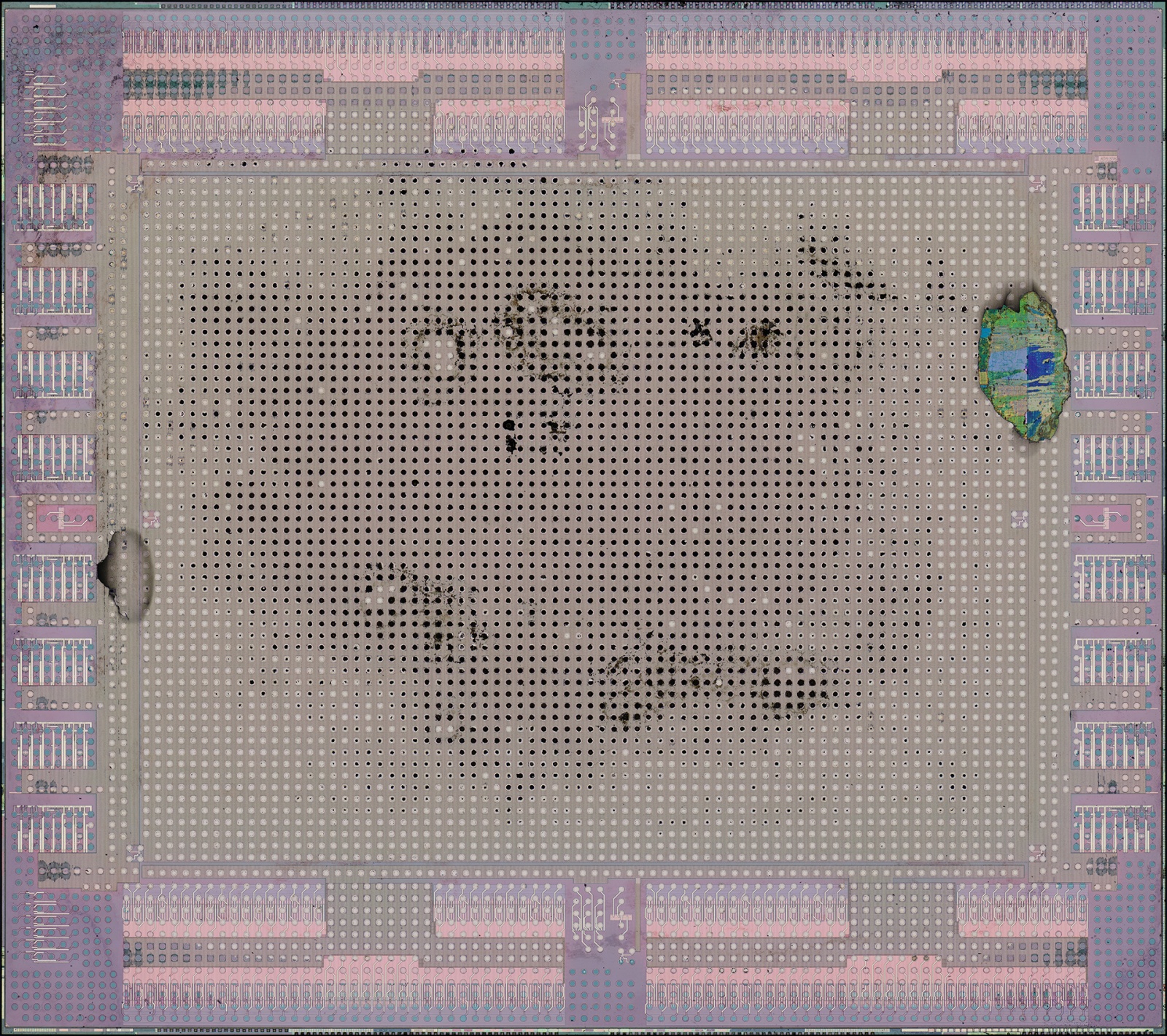

Эльбрус 8с представляет собой типичную микросхему общего назначения, выполненную в 2028-контактном BGA-корпусе с размером подложки 43 на 59 мм.

Процессор спроектирован и изготовлен по технологическим нормам 28 нм на заводах тайваньской компании TSMC с вытравленными двумя миллиардами семьсот тридцатью миллионами транзисторов.

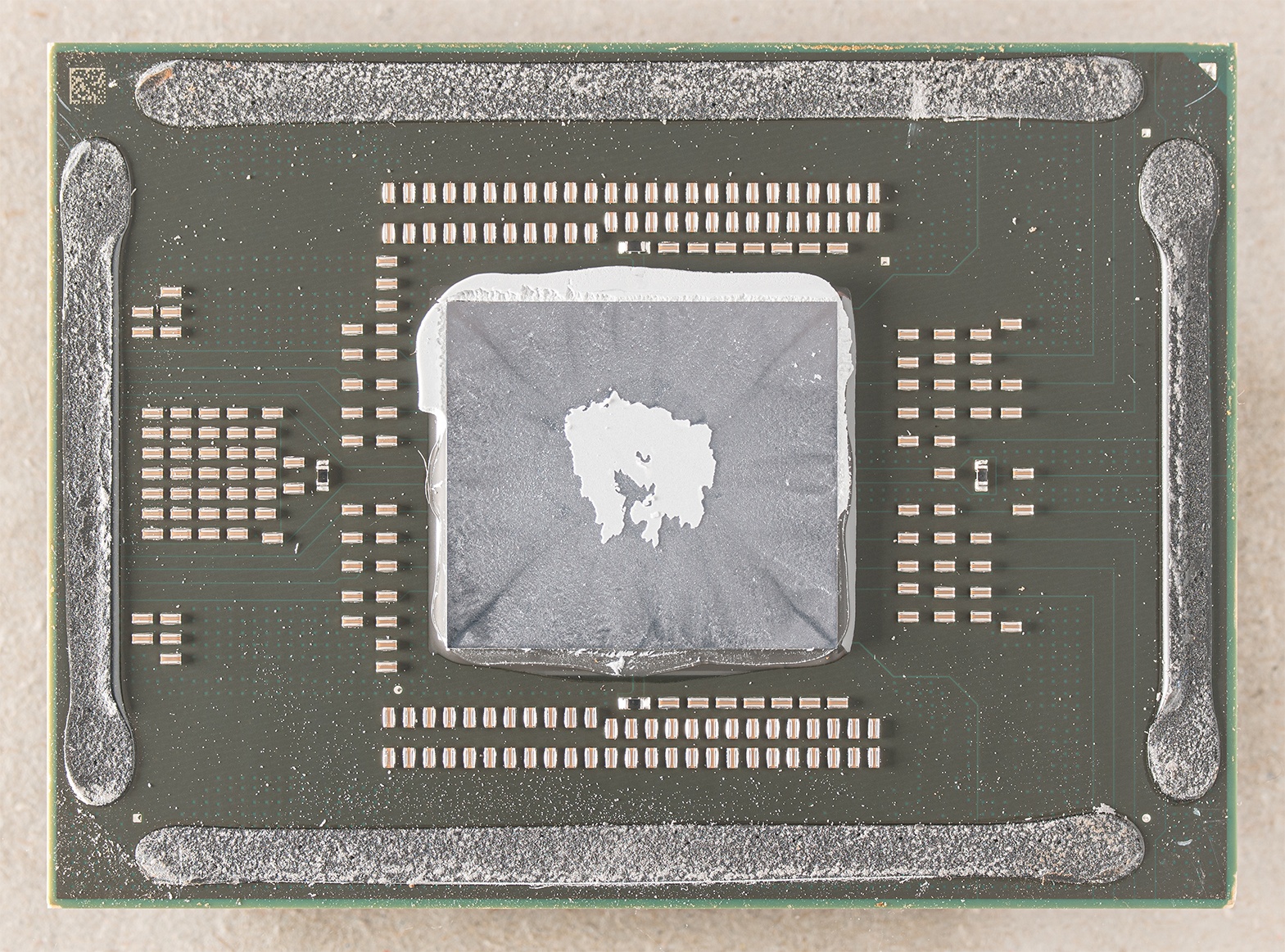

Сняв крышку процессора, мы видим кристалл с нанесённой на него термопастой и SMD-компоненты на подложке.

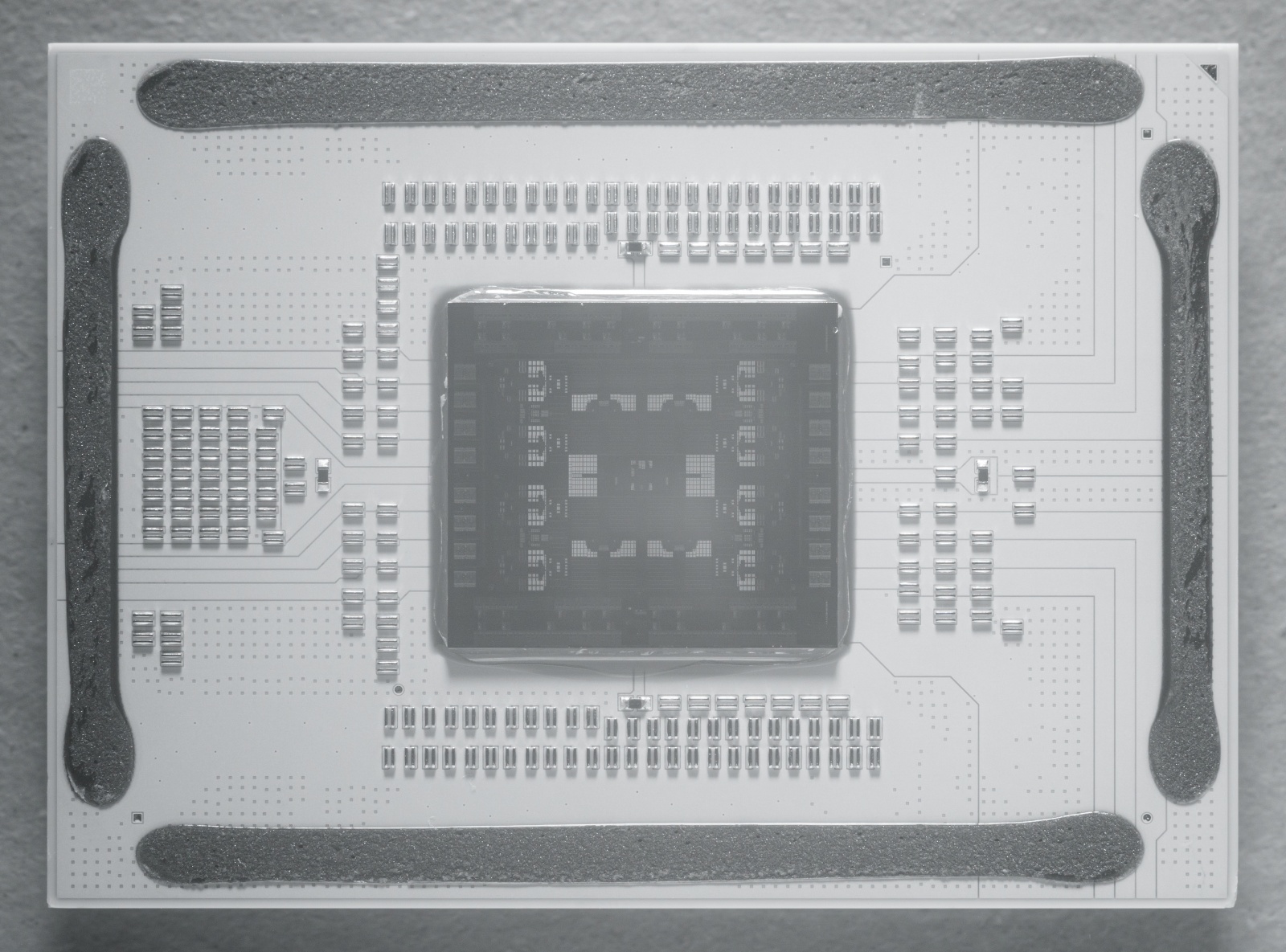

Площадь кристалла составляет 330,416 квадратных миллиметров.

Сразу после отделения кристалла от подложки мы видим металлический слой, соединяющий составные части чипа с BGA-шарами на подложке. Как и в большинстве современных микропроцессоров каждый контакт выполняет свою функцию (в основном для подачи питания по всей поверхности чипа).

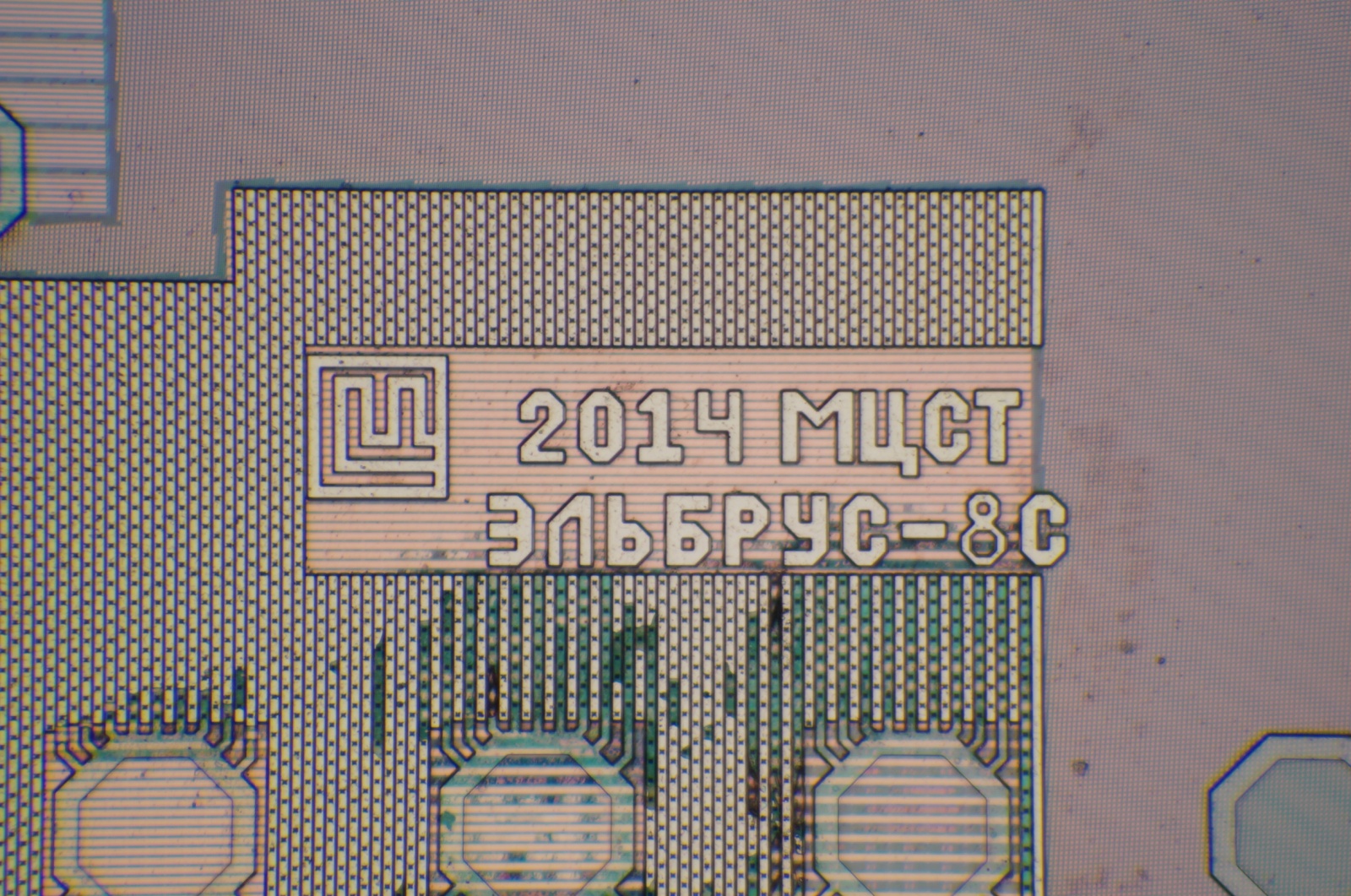

В правой верхней части кристалла виден старый логотип МЦСТ, название и год изготовления процессора.

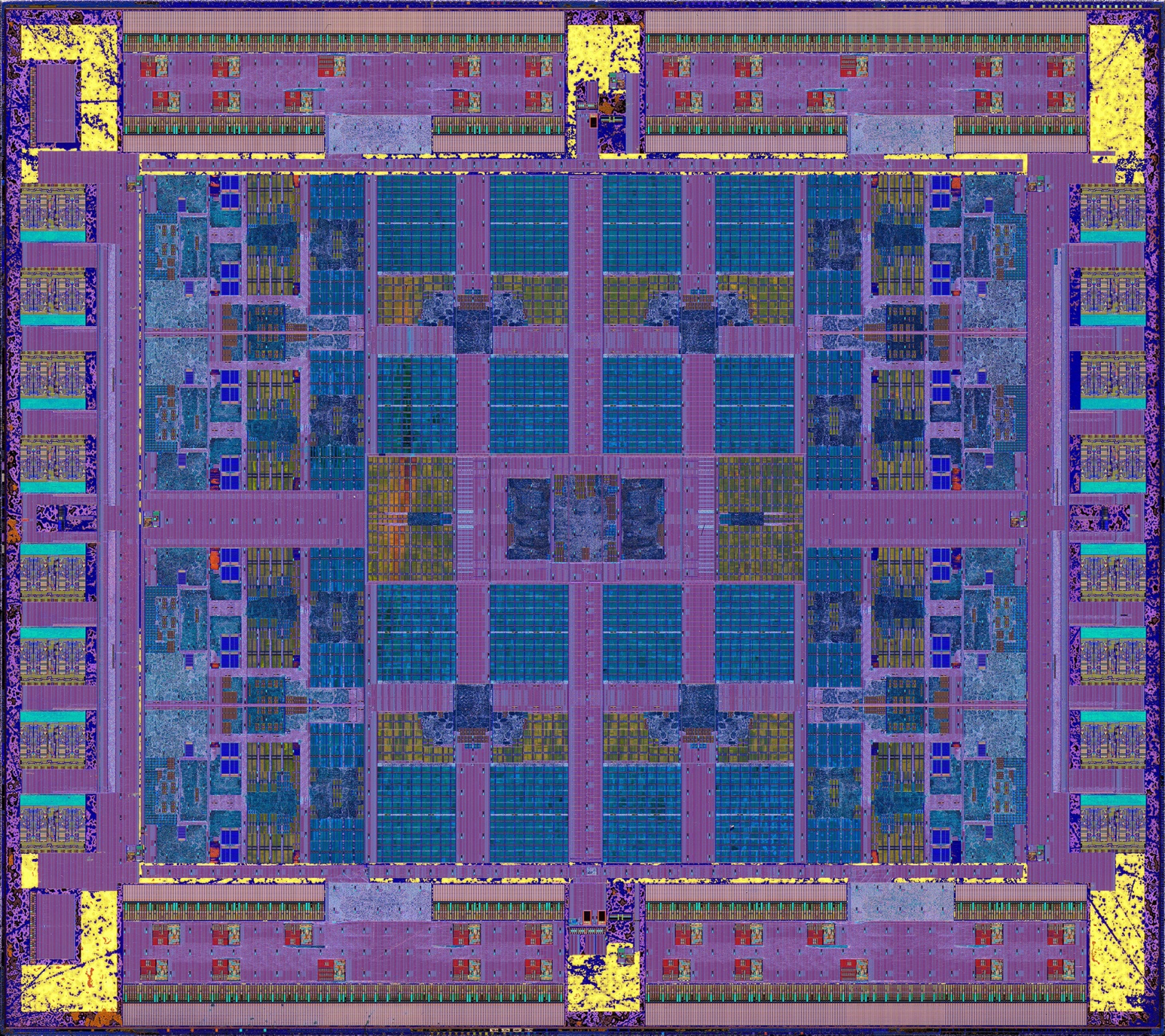

Сняв верхний металлический слой, нас встречает первозданный вид чипа…

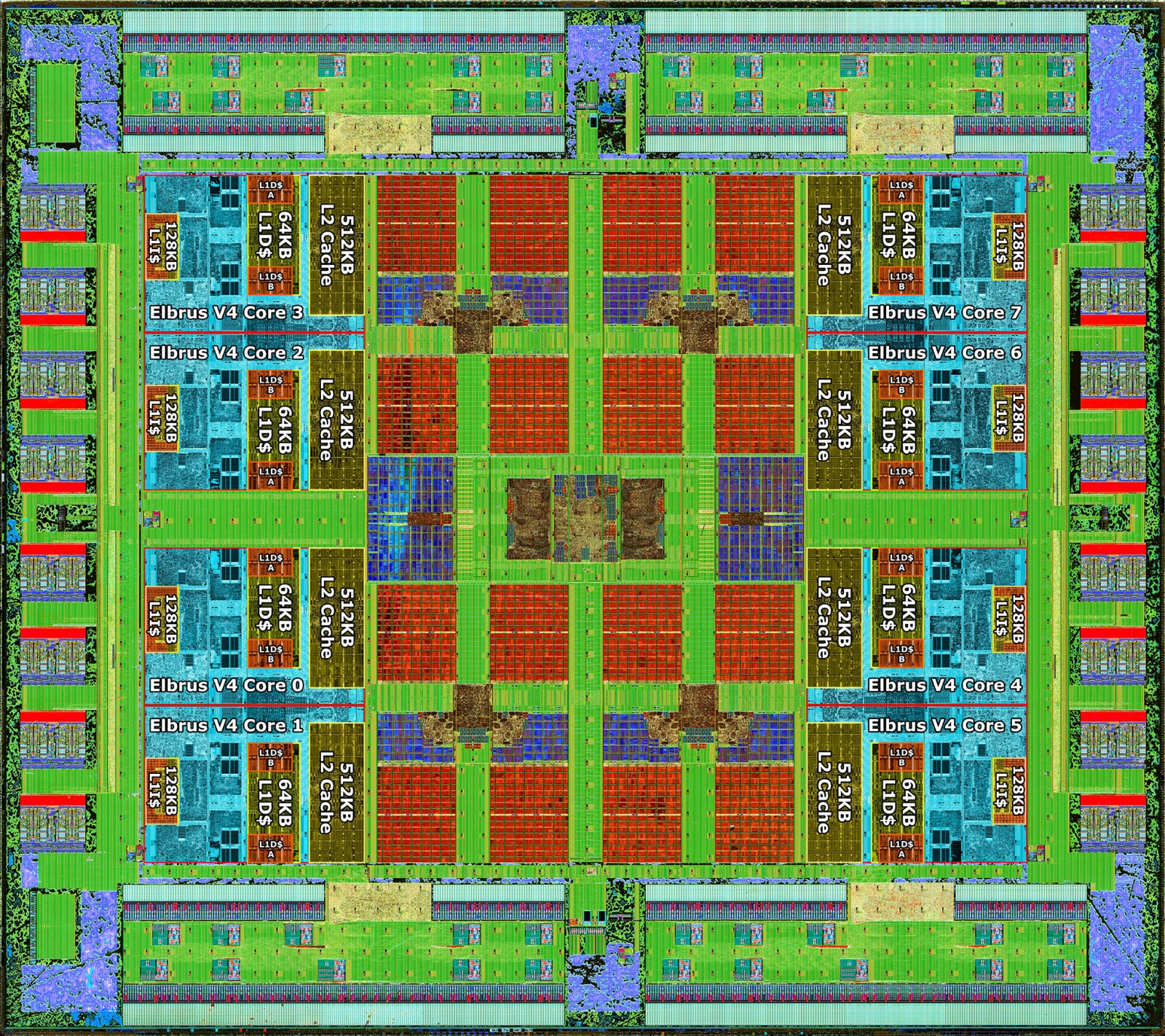

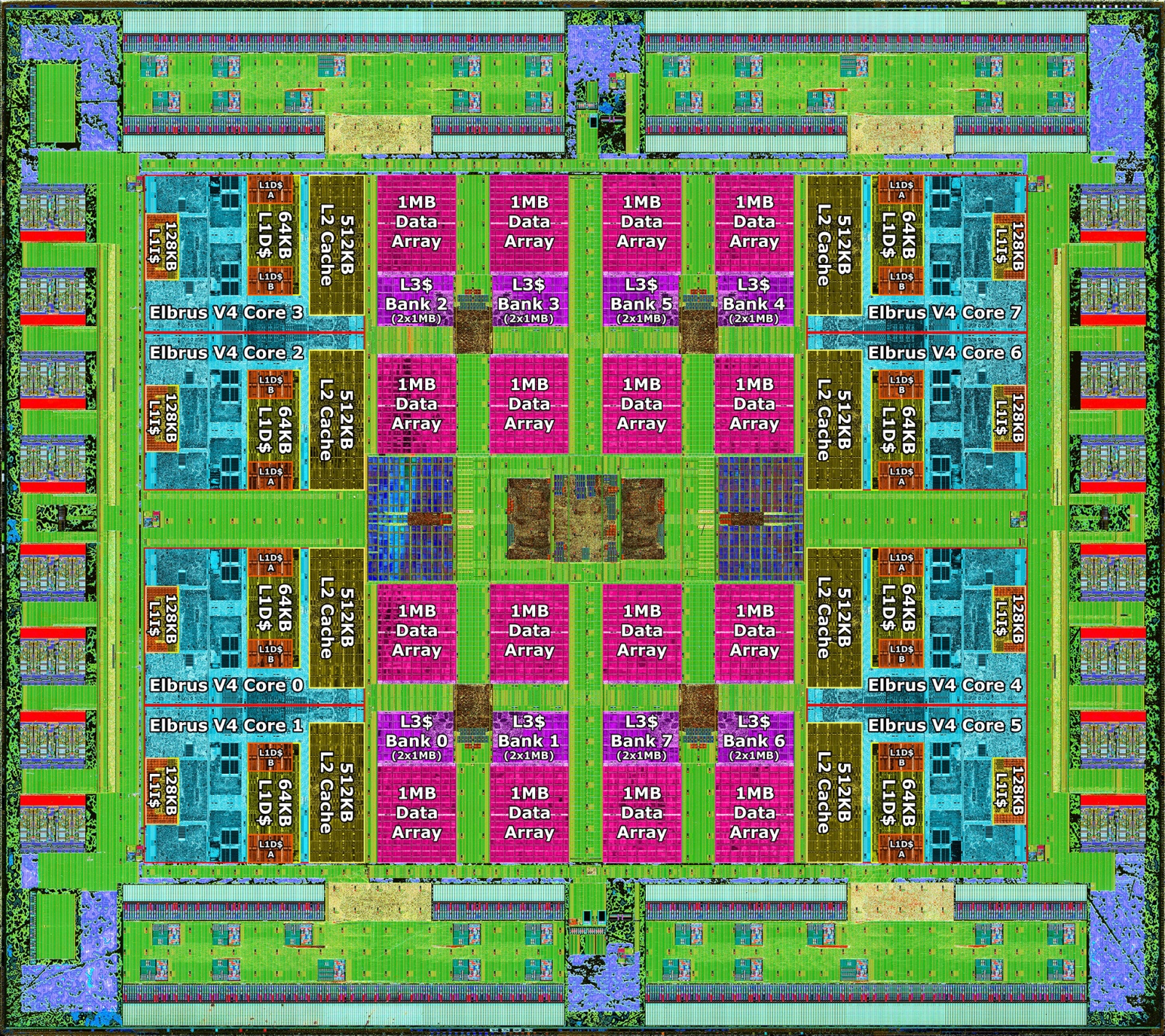

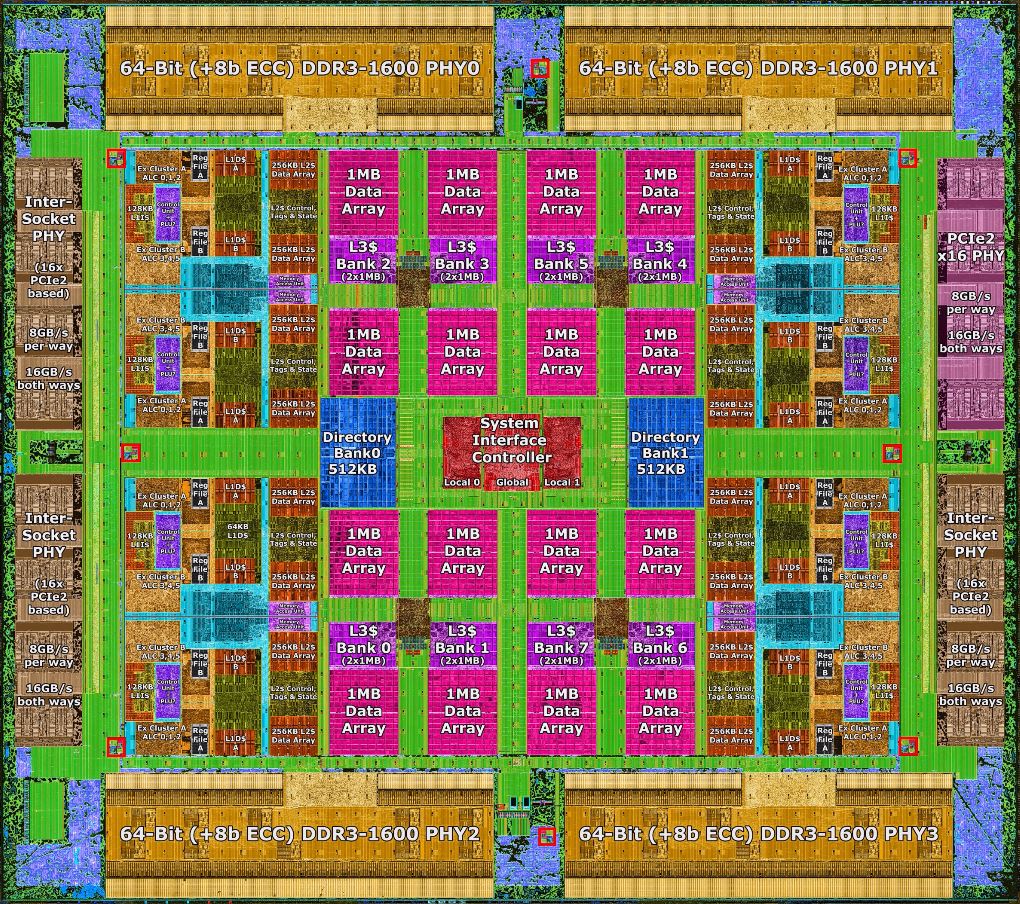

На кристалле размещены восемь процессорных ядер архитектуры Эльбрус 4-го поколения с тактовой частотой до 1300 МГц, каждое из которых способно исполнять до 25 операций за такт в скаля́рном и до 41 операции в ве́кторном режиме.

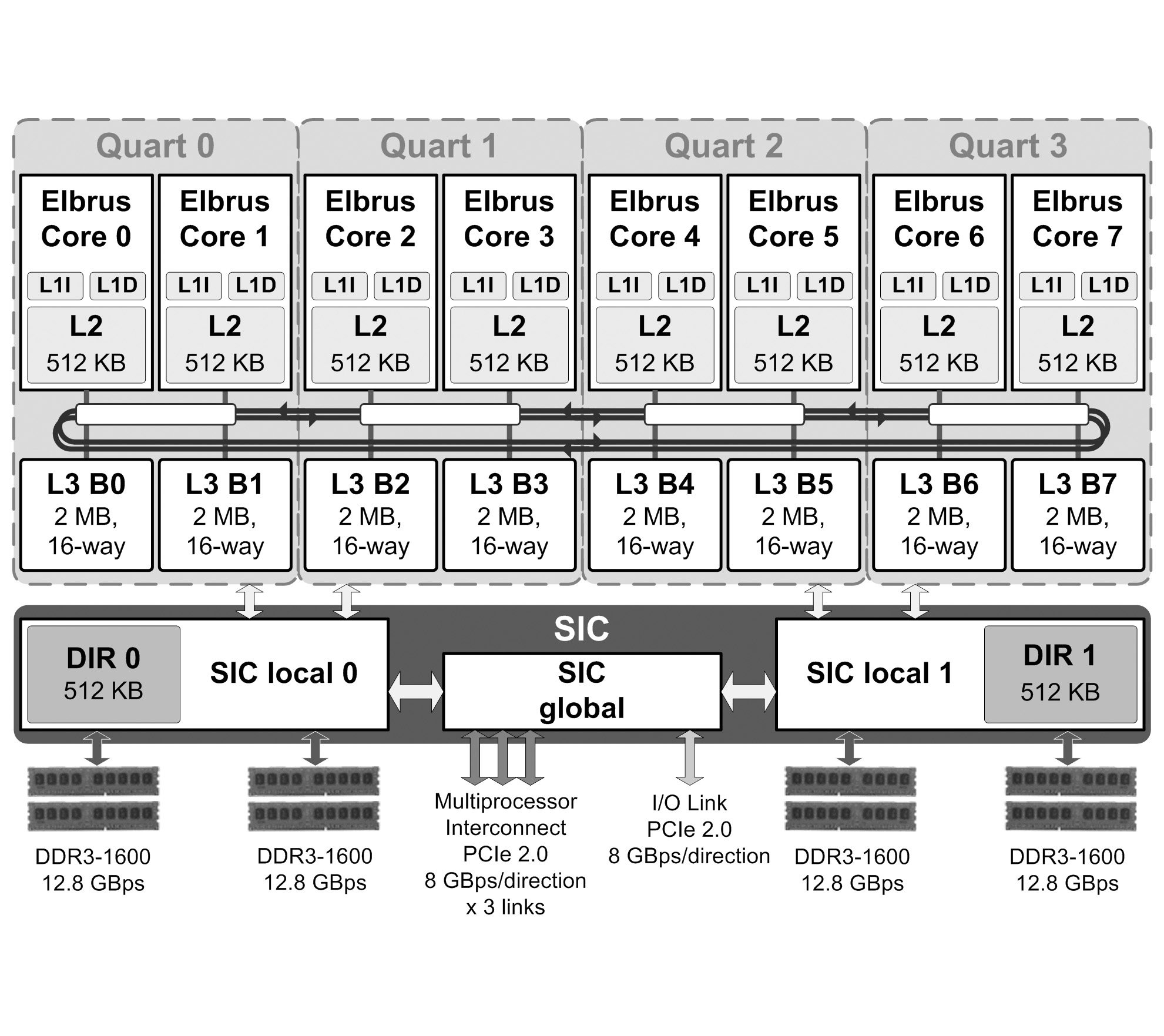

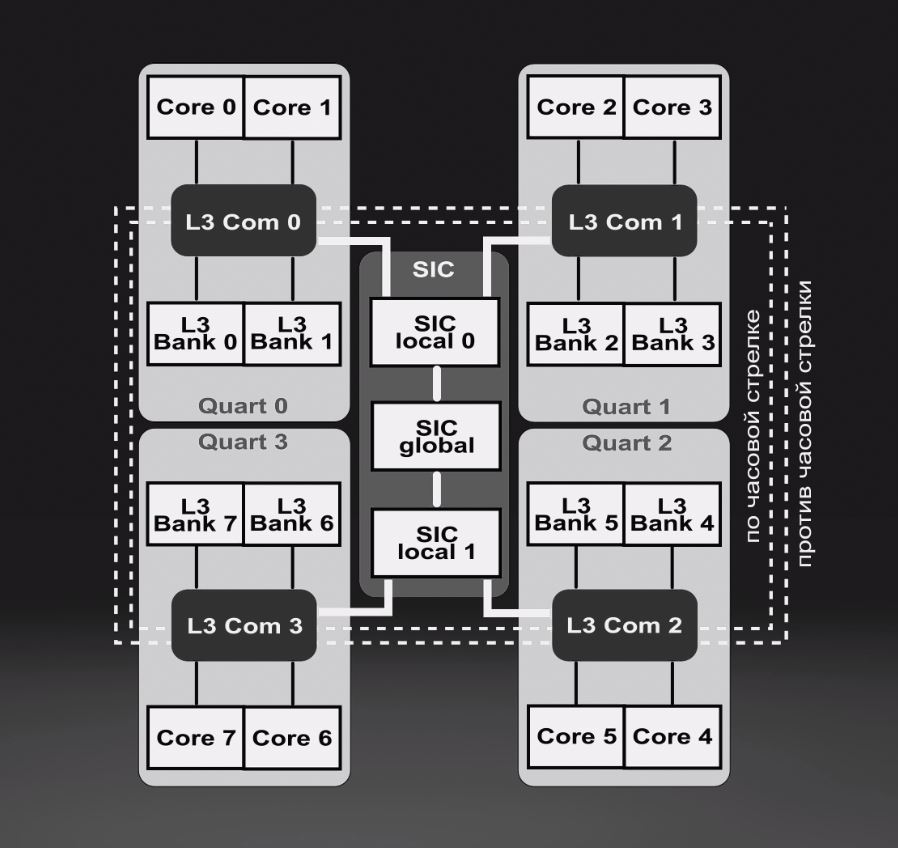

Ядра подключены к общей кэш-памяти третьего уровня, объёмом 16 Мб, имеющую распределённую структуру с разбиением на восемь независимых банков (от Б0 до Б7), причём каждое ядро имеет доступ ко всем банкам.

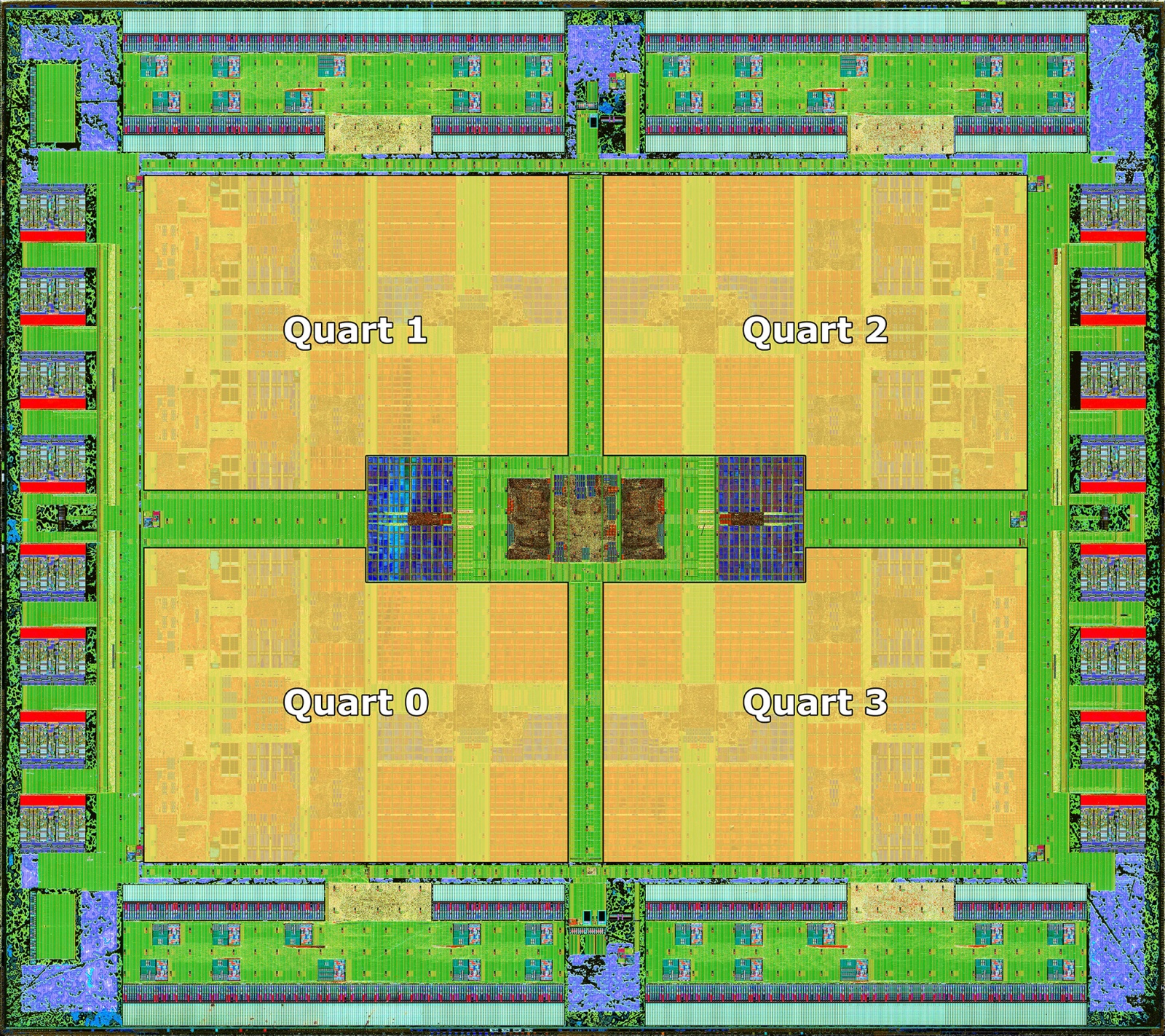

Ядра и банки общей кэш-памяти объединены в узлы (ква́рты) по два ядра и два банка в каждом. Кварты соединены двунаправленным буферизующим кольцом.

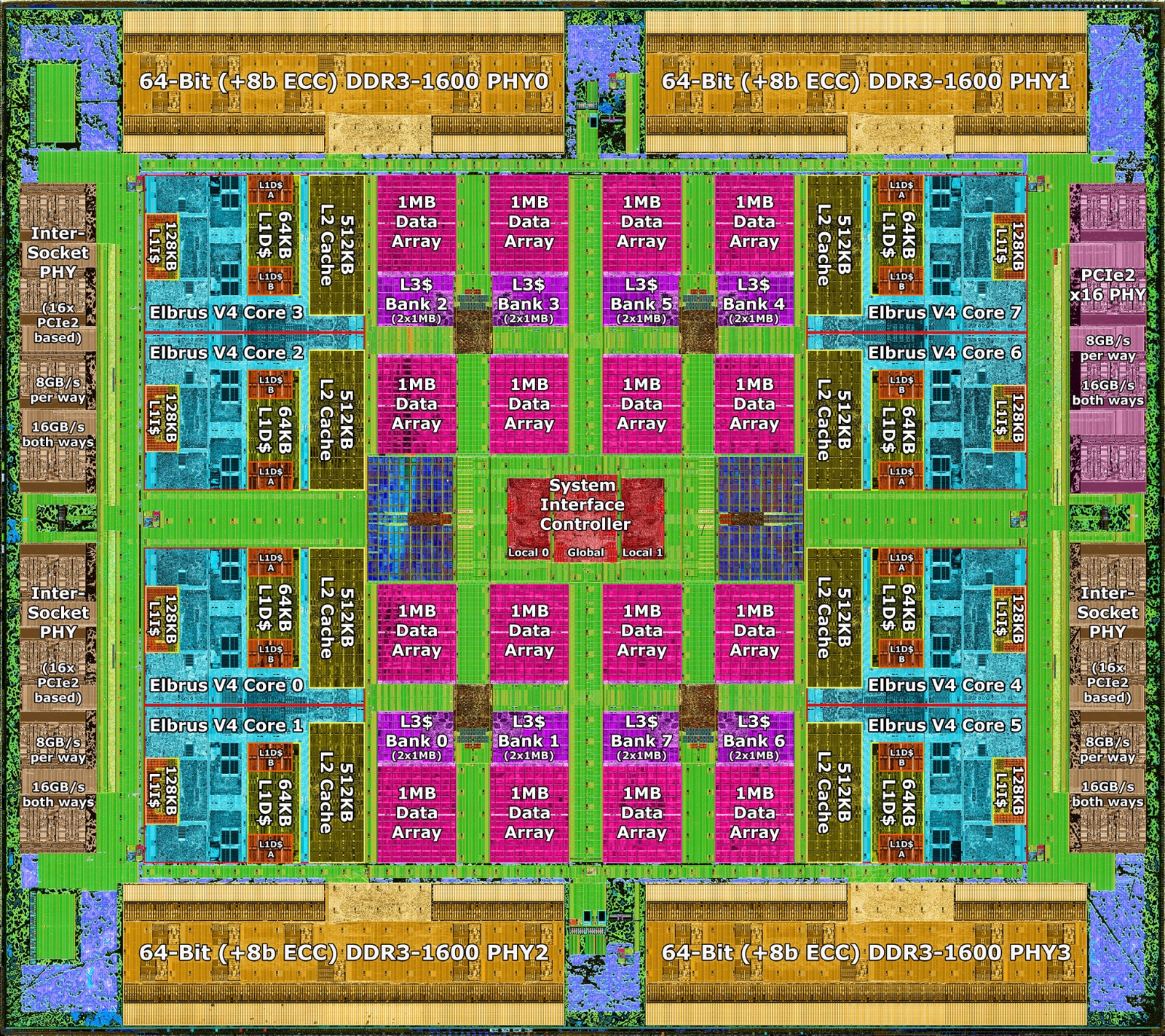

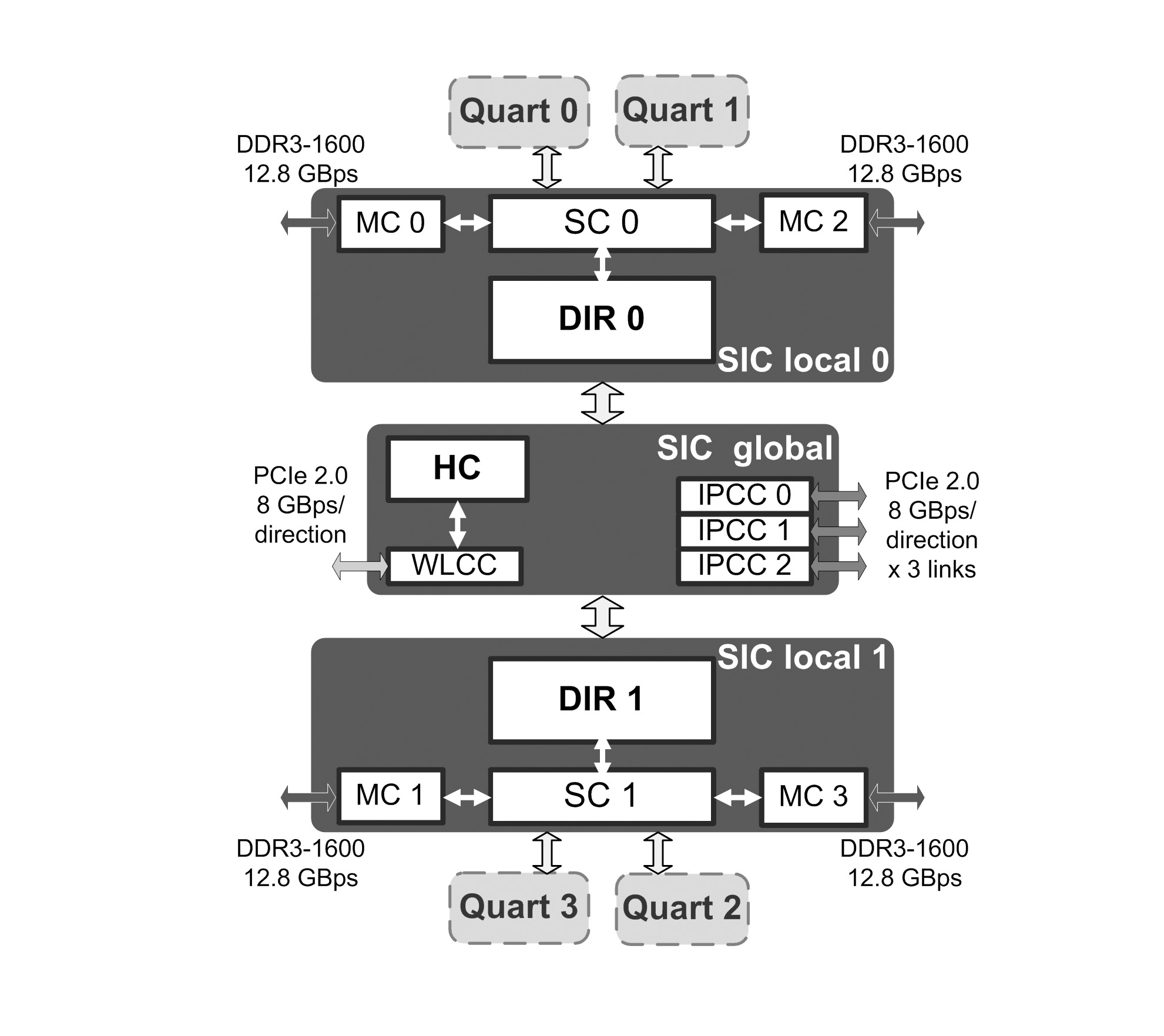

Контроллер системных обменов SIC выполняет функции доступа к памяти и схемам ввода-вывода, он также включает в свой состав все контроллеры высокоскоростных интерфейсов процессора:

- четыре контроллера каналов оперативной памяти SDRAM DDR3-1600 с максимальной пропускной способностью 51,2 гигабайт в секунду, которые обеспечивают установку до 64 Гб памяти на процессор;

- три контроллера дуплексных каналов межпроцессорного обмена с пропускной способностью 8 гигабайт в секунду в каждую сторону, позволяющие объединять до четырёх микропроцессоров в одну систему с когерентной общей памятью до 256 гигабайт;

- контроллер дуплексного канала ввода-вывода с пропускной способностью 8 гигабайт в секунду в каждую сторону, совместимый с южными мостом КПИ-2.

Расчетная тактовая частота Эльбрус 8с достигает 1,3 ГГц, при этом пиковая производительность составляет 250 гигафлопс на операциях с одинарной точностью (FP32) и 125 гигафлопс на операциях с двойной точностью (FP64).

Строение ядра

При разработке ядра Эльбрус-8C за основу было взято ядро микропроцессора предыдущего поколения Эльбрус-4C. Для повышения производительности ядра было решено увеличить тактовую частоту и число одновременно исполняемых арифметических операций с плавающей точкой.

Само ядро имеет двухкластерную организацию. Каждый кластер содержит три арифметико-логических канала (ALC), локальный блок регистрового файла (RF), локальный блок кэша данных первого уровня и блок подготовки операндов и сбора результатов. Каналы ALC имеют отдельные устройства для выполнения целочисленных операций и операций с плавающей точкой. Целочисленные операции выполняются во всех шести каналах двух кластеров. Скалярные обращения в память по считыванию выполняют ALC 0, 2, 3 и 5, по записи – ALC 2 и 5. Операции с плавающей точкой типа сложения и умножения, в том числе трехоперандные, выполняют ALC 0, 1, 3 и 4, операцию деления – только ALC 5.

Увеличение числа одновременно исполняемых арифметических операций с плавающей точкой было достигнуто за счет добавления в ALC 2 и 5 возможности исполнения операций сложения и умножения с плавающей точкой. При этом потребовалось модифицировать структуру широкой команды, а именно, организовать упаковку в нее новых слогов для кодирования новых команд ALC 2 и ALC 5 при сохранении обратной совместимости.

В результате применения обоих методов удалось повысить производительность ядра почти в 2,5 раза, при увеличении площади всего на 3,2%.

Частная кэш-память ядра была унаследована от процессора Эльбрус-4C с некоторыми изменениями. Как и в предыдущем поколении, используется раздельная кэш-память первого уровня (L1) для команд, объёмом 128 КБ и для данных, объёмом 64 КБ. Кэш-память второго уровня (L2) хранит и код, и данные.

Из-за технологических ограничений на площадь кристалла и новых особенностей иерархии размер L2 кэша был уменьшен до 512 КБ, без существенных изменений.

Устройство MAU (Memory Access Unit), подключаемое к выходу L2 кэша и управляющее обменами ядра с остальной системой, было разработано заново с целью повышения рабочей частоты и масштабируемости, а также оптимизации взаимодействия ядра с L3 кэшем.

Подсистемы памяти ввода-вывода

Подсистема памяти обеспечивает когере́нтный доступ процессорных ядер и внешних устройств к оперативной памяти. Как и кэш-память, она играет важную роль в достижении требуемой производительности, особенно для программ Memory-Bound. По сравнению с микропроцессором предыдущего поколения в Эльбрус-8C удвоилось число процессорных ядер и, соответственно, возросла нагрузка на память. Чтобы подсистема памяти не стала узким местом микропроцессора, количество каналов памяти DDR3-1600 было увеличено до четырех, что обеспечивает максимальную пропускную способность 51,2 ГБ/с и установку до 64 ГБ памяти на процессор. В состав микропроцессора входят три спроектированных на физическом уровне PCI Express-контроллера дуплексных каналов межпроцессорного обмена с пропускной способностью 8 гигабайт в секунду в каждую сторону. Посредством этих каналов возможно объединение до четырех процессоров в cache coherent NUMA систему с общей когерентной памятью.

Функции доступа к памяти выполняет локальный контроллер системных обменов SIC local. Кроме того он является глобальной точкой сериализации запросов в многопроцессорной системе с общей памятью. В «Эльбрус-8С» пропускная способность точки сериализации была увеличена вдвое за счет адресного разделения на два независимых кластера SIC local 0,1.

Банки кэш-памяти третьего уровня имеют фиксированную привязку к кластерам: каждая пара контроллеров памяти обслуживает ближайшие четыре банка L3 кэша.

Доступ ядер к внешним устройствам и конфигурационным регистрам системы, а также доступ внешних устройств к оперативной памяти системы посредством DMA обеспечивается через контроллер SIC global.

Коммутация соединений

Схема коммутации микропроцессора разделена на два уровня: ядра – L3 кэш и L3 кэш – SIC. На первом уровне реализована связь каждого процессорного ядра с семью остальными и с восемью банками общей кэш-памяти третьего уровня.

Разработанная схема имеет распределенную структуру и состоит из четырех узлов Quart. В кварту входят два ядра и два банка общего кэша, подключенные к централизованному коммутатору L3 Com. Кварты объединены в двунаправленное буферизующее кольцо с передачей пакетов по часовой стрелке и против часовой стрелки.

На втором уровне реализована связь банков L3 кэша с SIC. Каждая кварта подключена к соответствующей паре контроллеров памяти, входящих в состав одного из устройств SIC local. Коммутация происходит в два этапа: между двумя банками в кварте и между двумя квартами в SIC local. При доступе к подсистеме ввода-вывода и канала межпроцессорного обмена коммутация между всеми четырьмя квартами осуществляется вустройстве SIC global. Суммарная пиковая пропускная способность связей междучетырьмя квартами и контроллером SIC составляет по 166 ГБ/с в каждом направлении.

В связи с увеличением площади кристалла и переходом на новый технологический процесс 28 нм потребовалось решить ряд проблем, не связанных напрямую с достижением высокой производительности. В первую очередь стоит отметить проблему рассеиваемой мощности. Для снижения рассеиваемой мощности при простое одного или нескольких процессорных ядер разработан механизм их динамического отключения под управлением операционной системы. Измерение температуры кристалла осуществляется посредством восьми термодатчиков, размещенных в разных точках кристалла.

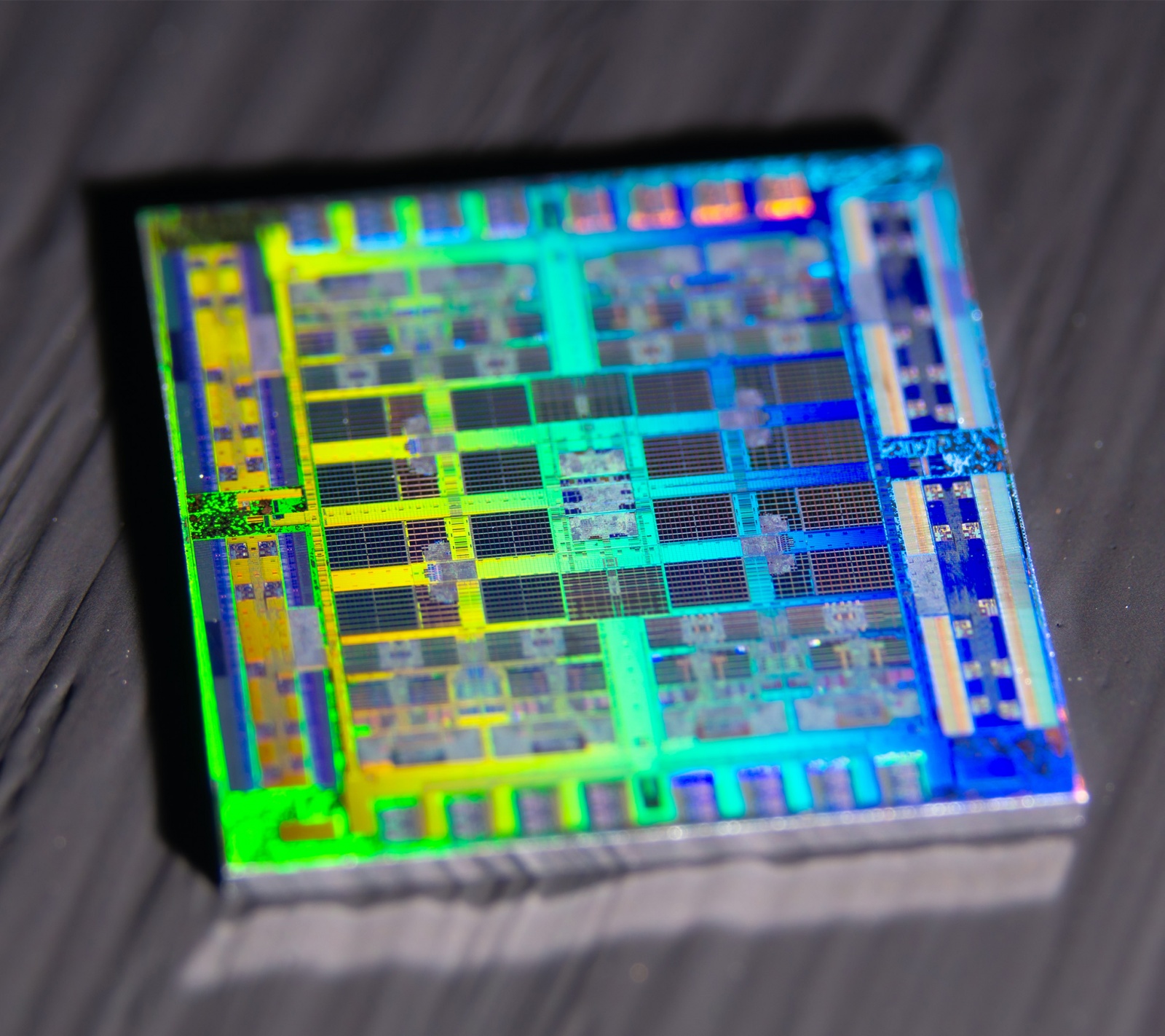

Теперь посмотрим на общую компоновку элементов на кристалле… Посвящается всем любителям голеньких чипов. Очень завораживает…

Производство «у нас»

В статье про разбор строения кристалла процессора Байкал М уже было упомянуто о нормативных требованиях, определяющих то, насколько отечественная микросхема может быть «российской». Однако прослеживается некая тенденция непринятия – многие пишут о том, «как может процессор быть отечественным, если он производится на заводах тайваньской компании».

На территории России есть две известных широкой публике фаблесс-компании – МЦСТ и Байкал Электроникс. Фаблесс означает отсутствие у компаний собственных производственных мощностей, отвечающих технологическим требованиям выпускаемой ими продукции. Таким подходом могут похвастаться также AMD, обособившая в 2009 году свое полупроводниковое производство в отдельную компанию Global Foundries, также NVidia, Qualcomm, MediaTek – вы всех их прекрасно знаете. Единственный процессор МЦСТ, выпускаемый на территории нашей страны, это Эльбрус 2СМ, - производится на Зеленоградском заводе Микрон по технологии 90 нм (2 ядра и 300 МГц это предел на этой фабрике). На Микроне делали даже 65 нанометровые изделия, но возникла проблема с огромным количеством стадий экспонирования, и выход годных кристаллов был низок. В начале прошлого десятилетия ждали новый литографический степпер, но помешали санкции. Микропроцессорная система сама по себе состоит из множества частей, логику и шаблоны которых предоставляют другие компании. Это абсолютно нормальная практика.

Причин, по которым на территории РФ нет высокотехнологичных заводов для производства КМОП на кремнии, достаточно много. Одной из них является то, что 17 июля 2014 года над Донбассом был сбит Боинг 777, летевший из Амстердама в Куала-Лумпур. На борту находилось очень много граждан Нидерландов, вследствие чего голландская компания ASML фактически прекратила все взаимоотношения с российскими микроэлектронными фабриками, поставив крест на их долгосрочных планах апгрейда и на плановом техобслуживании. Введенные в тот период разнообразные санкции, с одной стороны, запустили гораздо более активную программу импортозамещения, а с другой стороны - выкинули Россию из множества международных продуктовых цепочек, без которых современная микроэлектроника практически невозможна. И, опять же, в силу экспоненциального роста сложности и стоимости технологий, у РФ нет никаких шансов создать что-то подобное у себя, даже если потратить на это вообще все деньги. Для того, чтобы купить на Западе, денег в государственных кубышках вполне хватает, но продавать никто не спешит.

В итоге сейчас сложилась ситуация, когда настоящее российской микроэлектроники целиком определяется западными санкциями — как возможности, так и риски с ограничениями обусловлены именно ими. А будущее российской микроэлектроники неразрывно связано с Китаем, потому что он — единственная надежда на обход западной технологической гегемонии. Впрочем, не стоит думать, что полная зависимость от китайских технологий лучше зависимости от западных.

Фотографии кристалла микропроцессора Эльбрус 8с, сделанные Fritzchens Fritz в полном качестве:

Благодарю Locuza за опознание функциональных блоков на чипе.

Спасибо за внимание!

Автор: Василий