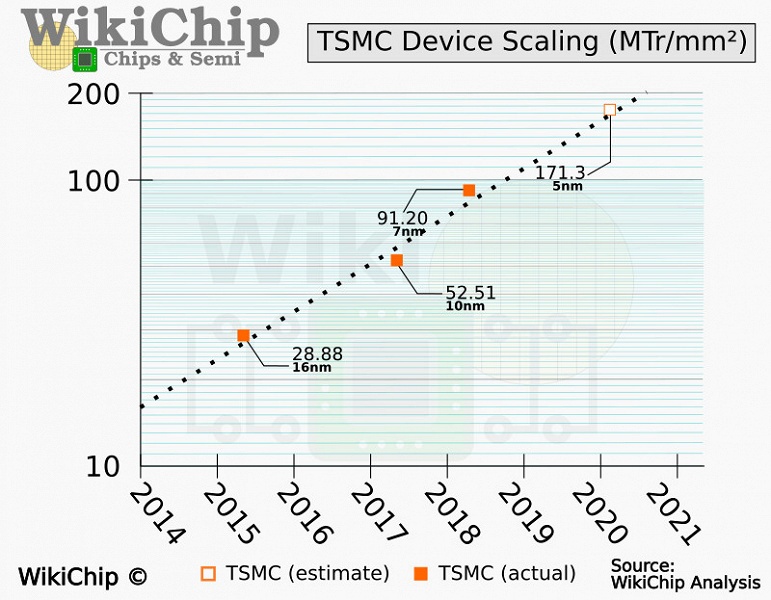

Проанализировав 5-нанометровый техпроцесс TSMC N5P, специалисты WikiChip признали значительное повышение плотности размещения транзисторов на кристалле по сравнению с N7 — наиболее передовым на сегодня техпроцессом TSMC, в котором не используется EUV. Как утверждается, выигрыш достигает 87%. Отметим, что собственная оценка TSMC составляет 84%. Ожидается, что выпуск продукции с применением техпроцесса N5P начнется в конце этого года. Рисковое производство по предшествующему техпроцессу TSMC N5 уже началось в начале года, а коммерческое должно начаться в апреле или мае, если сроки не будут сорваны пандемией COVID-19.

Техпроцесс N5P обеспечивает плотность приблизительно 171,3 млн транзисторов на 1 мм2. В случае N7 этот показатель равен 91,2 млн транзисторов на 1 мм2. Ожидается, что крупнейшим заказчиком продукции, изготовленной с использованием техпроцесса N5P, в 2020 году станет компания Apple, которая проектирует в расчете на этот техпроцесс однокристальную систему серии A14.