Примечание переводчика. В оригинале статьи авторы (один из них — пионер RISC-процессоров Д. Паттерсон) аргументируют необходимость развития открытых ISA (instruction set architecture, наборов команд процессоров) и продуктов на их основе. В качестве аргументов выдвигается стимулирование развития тех областей вычислительной техники и экономических ниш, в которых коммерческие компании не заинтересованы или же недостаточно гибки. Они напоминают об успехах открытых стандартов и свободного программного обеспечения.

На расширенную версию этой статьи (а также на контр-статью от представителей ARM и контр-контр-параграф от авторов!) я наткнулся в августовском выпуске Microprocessor Report (MPR). Доступ к MPR ограничен и распространяется только на подписчиков, однако в открытом доступе есть оригинальный отчёт, размещённый на сайте университета Беркли. Его перевод я и предлагаю далее.

Instruction Sets Should Be Free: The Case For RISC-V by Krste Asanović and David A. Patterson. EECS Department, University of California, Berkeley — Technical Report No. UCB/EECS-2014-146 www.eecs.berkeley.edu/Pubs/TechRpts/2014/EECS-2014-146.html

Copyright © 2014, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

Мнение авторов может не совпадать с мнением переводчика. Я также буду благодарен за любые неточности, замеченные в переводе, и уточнения к его содержанию.

Заказные системы на чипе (SoC), в которых процессоры и их кэши занимают лишь малую часть кристалла, становятся вездесущими; сегодня уже сложно найти электронное устройство, в котором не используется процессор в составе SoC. Таким образом, всё больше компаний проектируют чипы, в которые входят процессоры, чем это было раньше. Учитывая, какую революцию произвели открытые стандарты и открытое программное обеспечение — например, сетевой протокол TCP/IP и операционная система Linux — почему один из самых важных интерфейсов остаётся проприетарным?

Аргументы в поддержку свободных, открытых ISA

Безусловно, некоторые наборы команд процессоров (ISA, англ. instruction set architecture) могут быть проприетарными по историческим и коммерческим причинам. Однако, не существует ни одного твёрдого технического основания для объяснения отсутствия свободных, открытых вариантов.

- Это не ошибка или упущение. Компании, владеющие успешными ISA, такие как ARM, IBM и Intel, владеют патентами на причуды своих систем команд, что препятствует остальным использовать их без лицензий1. Переговоры об использовании длятся по 6-24 месяца и могут стоить от 1 до 10 миллионов долларов, что исключает из процесса академические организации и всех, кому требуются лишь небольшие объёмы производства2. Лицензия от ARM даже не позволяет вам спроектировать собственное ядро; вы лишь получаете право на использование их дизайна (лишь около 15 больших компаний имеют право на создание новых ядер ARM). Даже «OpenPOWER» — это оксюморон; вы обязаны платить IBM, чтобы использовать эту ISA. Разумная с т.з. бизнеса, подобная практика лицензирования душит конкуренцию и инновации, запрещая многим проектировать и делиться собственными ISA-совместимыми ядрами.

- Это не из-за того, что сами владельцы ISA производят подавляющую долю программного обеспечения для своих систем. Несмотря на размеры программных экосистем, которые выросли вокруг популярных ISA, львиная доля ПО для них пишется внешними людьми.

- Эти компании не владеют сакральным знанием, требуемым для создания адекватной ISA. Это большая работа, но многие сегодня могут спроектировать набор инструкций.

- Самые популярные ISA — не самые изящные. Как 80x86, так и ARM не считаются эталонами хорошего дизайна.

- Для верификации совместимости с ISA не требуется контроль компаний. Открытые организации разработали механизмы для сертификации совместимости аппаратных средств много лет назад. Примеры: стандарт IEEE 754 для чисел с плавающей запятой, Ethernet, PCIe. Если бы это было не так, открытые IT-стандарты не были бы столь популярны.

- Наконец, нет гарантий, что проприетарные ISA будут существовать долго. Если компания разоряется и исчезает, она забирает свою ISA с собой. Кончина DEC закончила развитие наборов инструкций Alpha и VAX.

Отметим, что ISA на самом деле — спецификация интерфейса, но не его реализация. Существует три подхода к реализации некоторого интерфейса:

1. Частная закрытая, аналогично Apple iOS.

2. Лицензируемая открытая, наподобие Wind River VxWorks.

3. Свободная и открытая, пользователи которой могут изменять и делиться, как это сделано в Linux.

Проприетарные ISA на практике позволяют работать с первыми двумя подходами, но вам нужна свободная, открытая ISA для поддержки всех трёх подходов.

Отсюда мы делаем вывод, что промышленность только выиграет от жизнеспособной свободно доступной открытой ISA в той же мере, в какой на неё благотворно повлияло развитие свободного открытого ПО. Например, это создаст по-настоящему свободный открытый рынок процессорных дизайнов, которому в настоящее время мешают патенты на причуды ISA.

Это может привести к:

1. Инновациям через конкуренцию на свободном рынке многих дизайнеров, включая открытые и закрытые реализации ISA.

2. Общим открытым дизайнам ядер, что будет выражаться в сокращении времени выхода продукции на рынок, уменьшении стоимости от переиспользования, меньшем числе ошибок из-за пристального внимания многих людей3, и в прозрачности, которая, например, затруднит внедрение секретных бэкдоров правительственными агенствами.

3. Процессорам, доступным для большего числа устройств, что поможет развивать Интернет Вещей (IoT, англ. Internet of Things), со стоимостью порядка доллара.

Аргументы в поддержку RISC как стиля для свободной, открытой ISA

Для того, чтобы какая-либо ISA была принята сообществом open-source, мы считаем, что она должна иметь успешную историю коммерческого применения. Первый вопрос — какой стиль ISA демонстирует такую историю? За последние 30 лет история не знает ни одной успешной стековой архитектуры (Примечание переводчика: странное заявление, учитывая успех Java bytecode и .NET CLI — стековых архитектур). Кроме как в сегменте приложений DSP (англ. digital signal processing), VLIW также постигла неудача: Multiflow всплыл брюхом вверх, а Itanium, несмотря на миллиардные инвестиции HP и Intel, не получил признания. Уже десятки лет ни одна новая CISC ISA не обретает успеха. Выжившие же CISC архитектуры транслируют свои сложные инструкции в более простые ISA, что очень оправдано для исполнения ценной унаследованной кодовой базы. Новая же ISA по определению не будет иметь такой базы, так что дополнительные расходы на аппаратуру и энергопотребление, требуемые для трансляции, сложно оправдать: почему бы сразу не использовать более простую ISA? RISC-подобные load-store наборы команд известны как минимум уже 50 лет, с эпохи CDC 6600 Сэймюра Крея. Тогда как 80x86 выиграл войны за ПК, RISC доминирует в планшетах и телефонах пост-ПК эры. В 2013 г. было продано более 10 миллиардов ARM, в сравнении с 0.3 миллиардами x86. Повторяя то, что мы уже говорили в 19804, мы считаем, что RISC — лучший выбор для свободной и открытой ISA.

Более того, новая RISC ISA может быть лучше своих предшественников, если при её разработке учесть их ошибки:

- Исключение слишком многого: отсутствие команд load/store для байт и полуслов в первом варианте Alpha ISA и отсутствие load/store для чисел с плавающей запятой в MIPS I.

- Включение излишнего: встроенный сдвиг в инструкциях ARM и регистровые окна SPARC.

- Влияние микроархитектурных деталей на ISA: отложенные переходы в MIPS и SPARC, барьеры-ловушки для чисел с плавающей запятой на Alpha.

Для удовлетворения потребностей рынка встраиваемых решений, RISC-и даже предоставили решение проблемы размера кода: ARM Thumb и MIPS16 добавили 16-битные форматы для того, чтобы код был даже короче, чем у 80x86. Таким образом, существует общепризнанное соглашение о том, как в целом должна выглядеть хорошая RISC ISA.

Аргументы за использование существующей свободной открытой RISC ISA

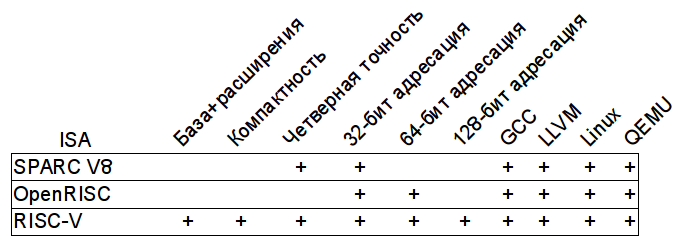

Уже существует три свободных и открытых RISC ISA5:

- SPARC V8 — к чести Sun Microsystems, она сделала SPARC V8 стандартом IEEE в 1994.

- OpenRISC — GNU-лицензированный open-source проект, начатый в 2000, с 64-битной ISA законченной в 2011.

- RISC-V — в 2010, частично из-за ограничений ARM на свой IP и из-за отсутствия 64-битных режимов, а также из-за общей гротескности ARM v7, мы и наши студенты Andrew Waterman и Yunsup Lee разработали RISC-V6 (произносится как «RISC-5») для нужд наших исследований и преподавательской деятельности и выпустили её под BSD-лицензией.

Так как обычно на то, чтобы отшлифовать все тонкости, уходят годы — вызревание OpenRISC заняло 11 лет, а у RISC-V ушло 4 года, — более правильно будет начать с уже существующей ISA, а не формировать комитет и начинать с нуля. Все RISC похожи, так что любая из них может быть хорошим кандидатом.

Так как ISA могут существовать десятилетиями, необходимо сперва экстраполировать и описать будущий ландшафт информационных технологий, чтобы понять, какие особенности могут оказаться важными, для облегчения процесса приоритезации. Скорее всего, преобладать будут три платформы: IoT — миллиарды дешёвых устройств с IP-адресами и доступом в Интернет; 2) персональные мобильные устройства, такие как современные телефоны и планшеты; 3) дата-центры (Warehouse-Scale Computers, WSCs). Можно иметь разные ISA для каждого типа платформ, однако жизнь будет проще, если она всюду будет одна. Такая картина будущего предлагает четыре ключевых требования на неё.

1. Формат «базовая ISA плюс расширения»7. Для повышения эффективности и уменьшения затрат SoC-системы добавляют собственные специфичные для приложения акселераторы. Для этого, а также чтобы поддерживать стабильную кодовую базу, свободная открытая ISA должна иметь: а) небольшое ядро инструкций, которые известны компиляторам и ОС, б) стандартные, но опциональные расширения для частых частных сценариев адаптации SoC к конкретному приложению, в) пространство для полностью новых кодов инструкций для работы акселераторов.

2. Компактная кодировка команд. Меньший объём кода желателен из-за чувствительности цены IoT-приложений к объёму используемой памяти.

3. Четверная точность (QP, quadruple-precision) вычислений над числами с плавающей запятой в дополнение к двойной и одинарной точностям. Некоторые приложения, исполняющиеся в дата-центрах сегодня, обрабатывают настолько большие объёмы данных, что они уже сейчас используют программные библиотеки для QP.

4. 128-битная адресация в дополнение к 32- и 64-битной. Ограничения по памяти IoT-устройств означают, что 32-битная адресация ещё долгое время будет актуальной. 64-битные адреса — дн-факто стандарт для всех больших систем. Хотя промышленность WSC не потребует всех 2128 байт, вполне правдоподобно, что через десятилетие понадобятся числа, превышающие 264 (16 эксабайт), для адресации хранилищ SSD. Ограниченный размер пространства адресов — одна из тех ошибок ISA, которые сложно исправить8, разумно планировать большие адреса уже сейчас.

Следующая таблица суммирует информацию о трёх свободных открытых ISA по этим четырём критериям, а также по наличию поддержки компиляторами и портированными ОС.

Аргументы в поддержку RISC-V как свободной открытой ISA

Наше сообщество должно объединиться вокруг единой ISA, чтобы проверить, что свободная открытая ISA может работать на практике. Только RISC-V удовлетворяет всем четырём требованиям. Она также от 10 до 20 лет моложе остальных RISC, так что мы имели возможность проанализировать и исправить их ошибки, такие как слоты задержки переходов SPARC и OpenRISC. Поэтому система команд RISC-V простая и понятная (см. таблицы 4 и 5 оригинальной статьи, а также www.riscv.org). В дополнение к тому, что остальные ISA не выполняют многие требования, есть вопросы к тому, что 64-битный SPARC V9 — проприетарный, а OpenRISC потерял импульс.

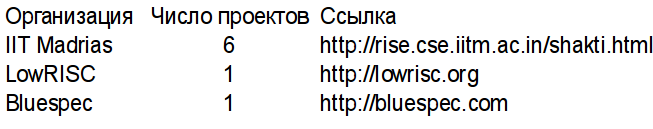

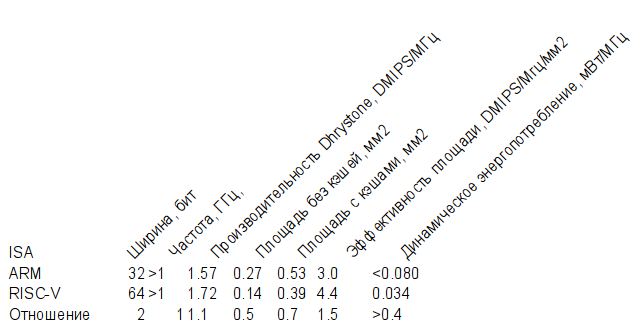

RISC-V всё ещё имеет большой импульс. Таблица 1 перечисляет различные группы, проектирующие SoC на основе RISC-V. Отчасти из-за использования высокопродуктивной, открытой системы проектирования аппаратуры Chisel9, университет Беркли имеет уже 8 типов чипов и новые разработки в процессе. Таблица 2 показывает, что одно 64-битное ядро RISC-V занимает половину площади, потребляет половину от мощности и при этом работает быстрее, чем 32-битный ARM с похожим конвеером или тем же техпроцессом. Хотя сложно полностью устранить нашу предвзятость в этом вопросе, мы полагаем, что RISC-V — лучший и безопасный выбор для свободной открытой RISC ISA. Поэтому мы будем проводить серию семинаров10 для расширения сообщества RISC-V и, вдохновлённые примерами из таблицы 3, планируем создать некоммерческий фонд для задачи сертификации реализаций, а также для поддержки и развития ISA.

Заключение

Наши доводы даже более ясны для открытой ISA, чем для открытой ОС, так как ISA меняются очень медленно, тогда как алгоритмические инновации и новые приложения требуют непрерывной эволюции ОС. Также, как и TCP/IP, это — тсандарт на интерфейс, который легче поддерживать и развивать по сравнению с ОС.

Открытые ISA использовались и раньше, но они никогда не становились популярными из-за недостатка спроса в них. Низкая цена и энергопотребление IoT, желание иметь альтернативу 80x86 для дата-центров и тот факт, что процессорные ядра — лишь малая, но вездесущая часть всех SoC, комбинируются в то предложение, способное удовлетворить возникший спрос. RISC-V нацелен в первую очередь на SoC, с базовым набором никогда не меняющихся команд, учитывая долгую жизнь идей RISC, с медленно эволюционирующим подмножеством опциональных расширений, а также уникальными инструкциями, которые никогда не будут переиспользованы. Хотя первый плацдарм для RISC-V может быть IoT или WSC, наша цель шире: так же, как Linux стал стандартной ОС для большинства вычислительных устройств, мы представляем себе RISC-V как стандартную ISA для всех вычислительных устройств будущего.

Литература

1. Письмо из MIPS (2002). brej.org/yellow_star/letter.pdf.

2. Demerjian, C. (2013). «A long look at how ARM licenses chips: Part 1 of 2,» semiaccurate.com/2013/08/07/a-long-look-at-how-arm-licenses-chips/

3. Raymond, E. (1999). The Cathedral and the Bazaar. Knowledge, Technology & Policy, 12(3), 23-49 // Пер. на русский яз.: Эрик С. Рэймонд. Собор и Базар. lib.ru/LINUXGUIDE/bazar.txt

4. Patterson, D. & D. Ditzel. (1980) «The Case for the Reduced Instruction Set Computer.» SIGARCH Computer Architecture News 8.6, 25-33.

5. Мы недавно узнали о намерениях Open Core Foundation о проектировании 64-битного открытого ядра, основанного на SH-4, к 2016 году.

6. Waterman, A. et al. (2014). The RISC-V Instruction Set Manual, Volume I: User-Level ISA, Version 2.0. EECS Technical Report No. UCB/EECS-2014-54, UC Berkeley.

7. Estrin, G. (1960) «Organization of computer systems: the fixed plus variable structure computer.» Western Joint IREAIEE-ACM Computer Conference, 33-40.

8. Bell, G., & W. Strecker. (1976) «Computer structures: What have we learned from the PDP-11?», 3rd ISCA, 1-14.

9. Bachrach, J., et al. (2012) «Chisel: constructing hardware in a Scalaembedded language.» Proc. 49th DAC, 1216-1225.

10. Первый семинар по RISC-V будет проводиться 14-15 января 2015 г. в Monterey, CA. www.regonline.com/riscvworkshop

Таблица 1. Проекты RISC-V вне университета Беркли (полную таблицу см. в оригинальном отчёте).

Таблица 2. Сравнение 32-битного ARM (Cortex A5) с 64-битным RISC-V ядром (Rocket), выполненных на одном техпроцессе (TSMC 40GPLUS). Данные взяты с сайта ARM и из статьи Y. Lee et al. «A 45nm 1.3GHz 16.7 Double-Precision GFLOPS/W RISC-V Processor with Vector Accelerators», которая будет опубликована в трудах: the 40th European Solid-State Circuits Conference, September 22-24, 2014

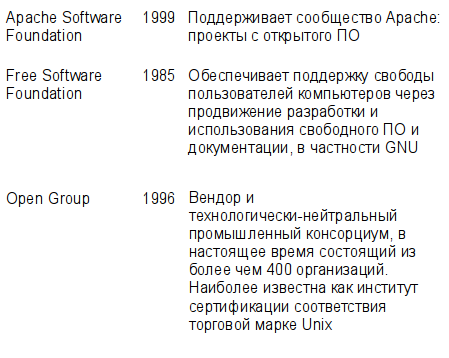

Таблица 3. Примеры open-source фондов ПО, которые поддерживают и развивают open-source проекты десятилетиями.

Таблицы 4 и 5. Формат набора инструкций RISC-V. См. в оригинальном отчёте.

Автор: Atakua