Пути технологии неисповедимы. Три месяца назад к нам в Silicon Valley приехал бизнесмен из Украины Александр Романишин. Я пошел с Александром на выставку для разработчиков IoT, где мы встретили Дэвида Гарольда из британской части Imagination Technologies (компании, которая спроектировала PowerVR GPU внутри Apple iPhone).

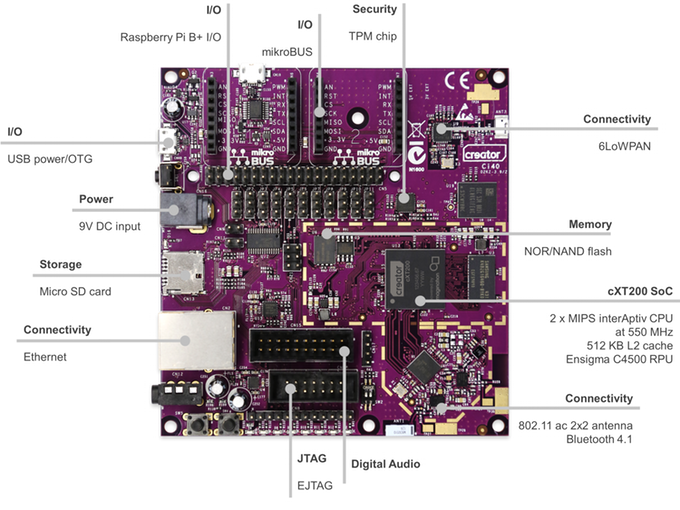

Александр увидел у Дэвида демо платы MIPS Creator ci40 для «умных ферм», и минут двадцать рассказывал Дэвиду, что все правительство Украины начиная с Порошенко лично желает в порядке нахождения экономического будущего страны скрестить электронные технологии и сельское хозяйство.

Дэвид воспринял все это максимально буквально и сегодня утром я получил от начальника Дэвида письмо, откуда узнал, что они в Великобритании сделали онлайн вебинар по использованию MIPS Creator ci40 для построения системы умной ирригации, и соратники Александра могут зарегистрироваться для этого семинара, который состоится в среду 28 сентября в 11 утра по Silicon Valley / в 21.00 по киевскому времени:

По этому поводу я хочу копнуть глубже внутрь чипа и рассказать про историю и особенности процессорного ядра в показываемом в вебинаре устройстве. Внутри MIPS Creator ci40 стоит чип на основе многопоточного двухядерного кластера MIPS interAptiv, продвинутого отпрыска ядра MIPS 24KEc. Последний сейчас переживает вторую молодость внутри только что вышедшего на рынок Omega2, Linux-компьютера ценой $5 размером с почтовую марку. Чем же MIPS interAptiv внутри MIPS Creator ci40 отличается от MIPS 24KEc внутри Omega2 с точки зрения микроахитектуры и как это задевает программиста?

Сначала пару слов про MIPS 24KEc. В MIPS Technologies есть три линейки ядер, как три медведя в сказке Льва Толстого:

В домике этом жили три медведя. Один медведь был отец, звали его Михаил Иваныч. Он был большой, лохматый и суперскалярный (MIPS P5600, P6600). Другой была медведица. Она была поменьше, но более power-efficient, и звали ее Настасья Петровна (MIPS 24K, interAptiv, I6400). Третий был маленький медвежонок с минимальной die area and very low power consumption, и звали его Мишутка (MIPS M51xx, M62xx).

Короче, MIPS 24K — это основа 32-битной секции средней линейки процессорных ядер MIPS Technologies. У них 8 стадий конвейера (что больше, чем 5 у и меньше, чем 15), есть предсказатель переходов (в отличие от MIPS M51xx, M62xx), но нет суперскалярности (в отличие от MIPS I6400, P5600, P6600).

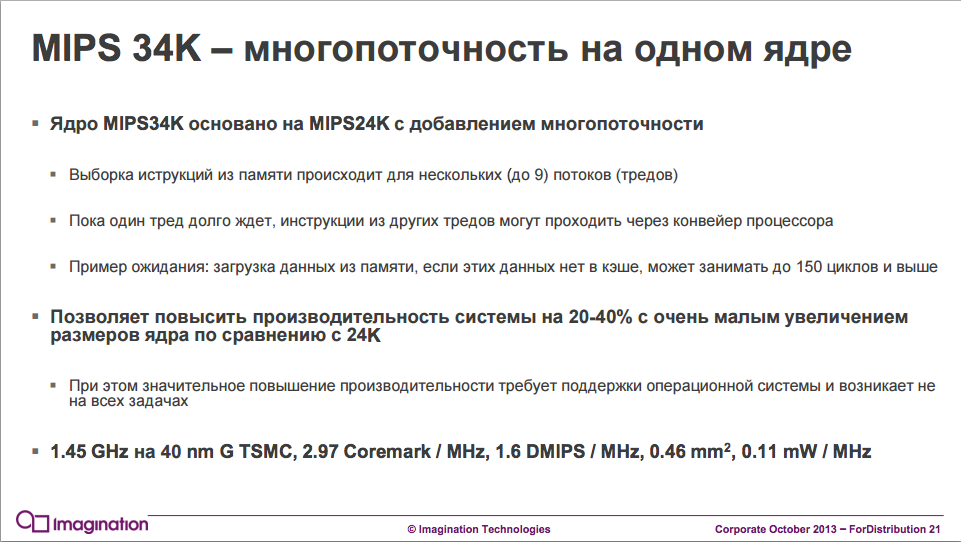

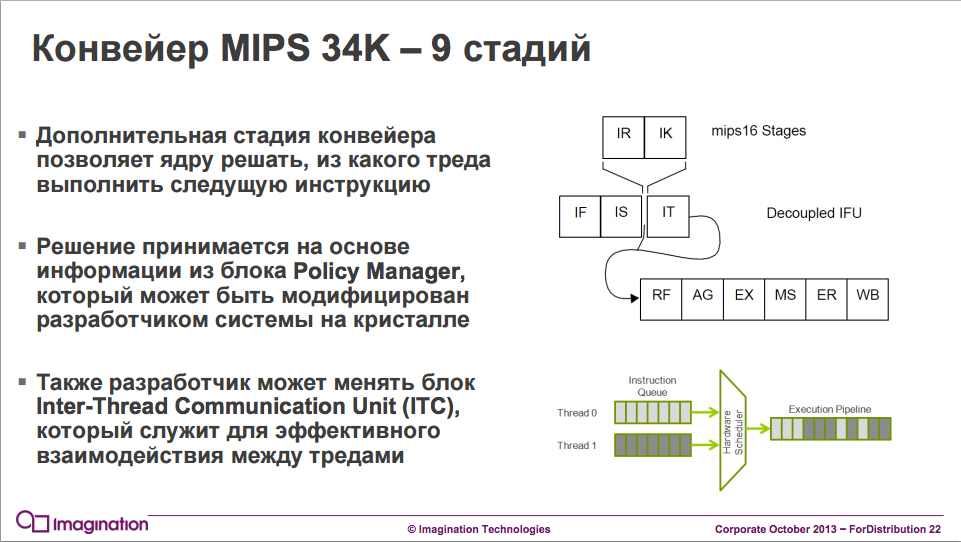

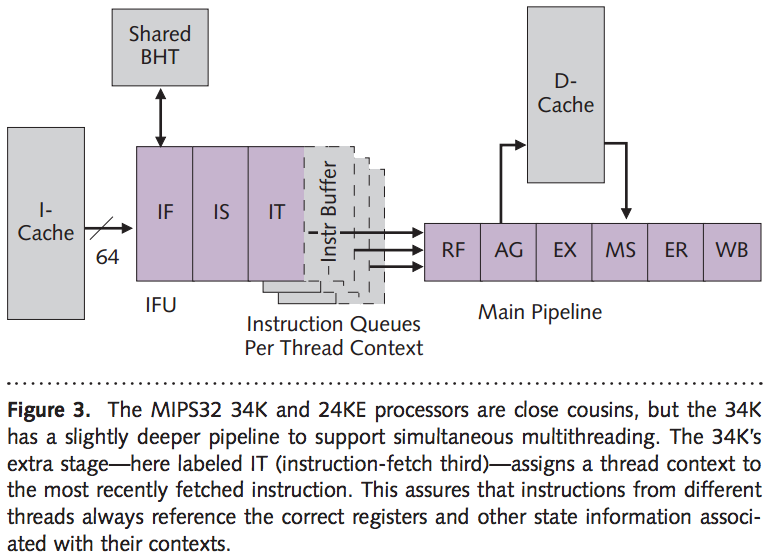

После MIPS 24K был MIPS 34K, в который была добавлена хардверная поддержка многопоточности (hardware supported multithreading). Это довольно элегантное решение для следущей проблемы.

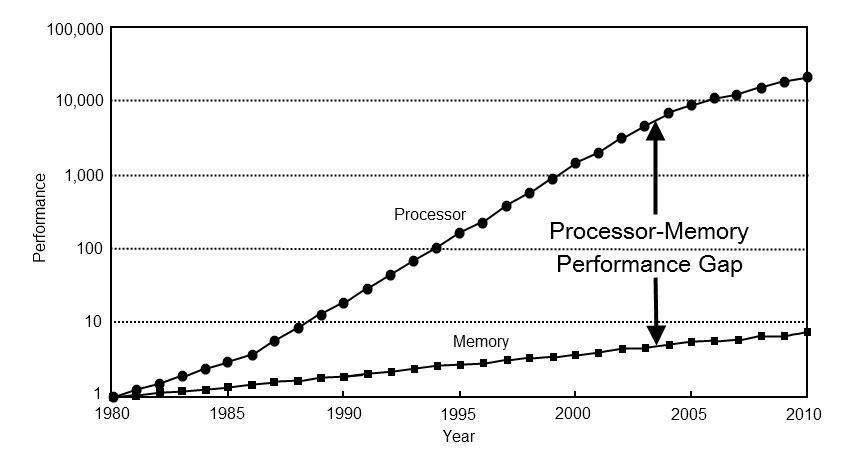

Дело в том, что в последние десятилетия скорость арифметических вычислений в процессоре росла быстрее скорости доступа к памяти:

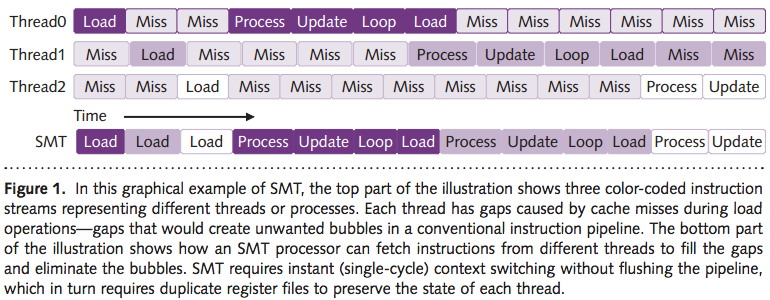

В нашу эпоху за время ожидания данных из памяти при промахе кэша, процессор мог бы выполнить десятки арифметических инструкций. Как же сделать чтобы процессор не простаивал (простой такого типа может отнимать до 50% времени выполнения типичной программы)? А вот как:

Пару картинок из статьи в журнале The Microprocessor Report":

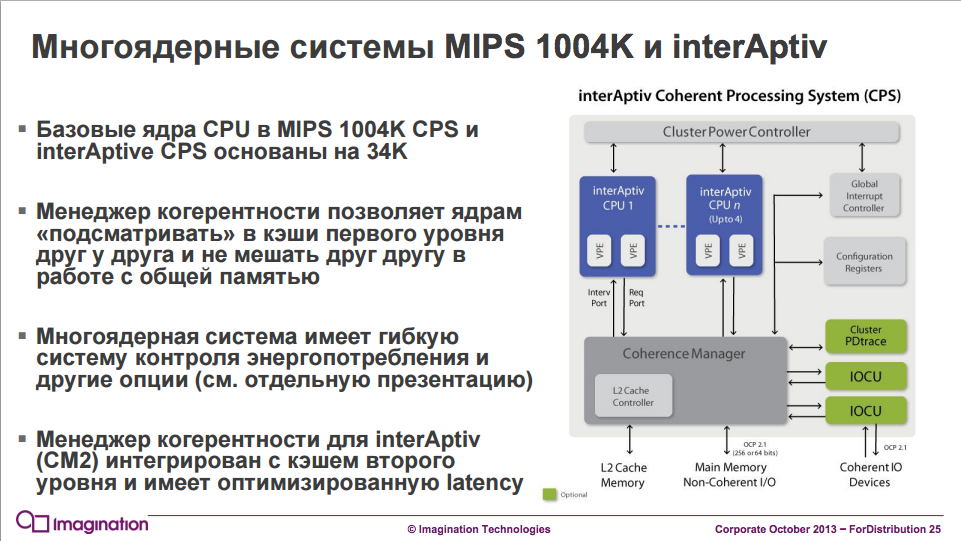

Аппаратную поддержку многопоточности на одном ядре не следует путать с многоядерностью. При этом они могут присутствовать как по отдельности, так и в комбинации. MIPS interAptiv (как и его предшественник MIPS 1004K) является многоядерной системой с менеджером когерентности кэшей первого уровня (чтобы в L1 кэшах разных ядер не лежали разные модифицированные данные):

MIPS interAptiv является современной оптимизированной версией линейки которая началась с MIPS 24K. Именно он стоит во встроенном компьютере MIPS Creator ci40. Хотя процессорных ядер в нем два, но многоядерный Линукс воспринимает их как четыре, так как каждое из двух ядер внутри обрабатывает два потока команд — hardware-supported multithreading. Пока один tread ждет во время промаха кэша, другой может работать — этим достигается бОльшая загрузка процессора. В конечном итоге, такая структура приводит к экономии энергопотребления по сравнению с системами с бОльшим количеством однопоточных ядер:

Автор: YuriPanchul