Добрый день.

15 мая была проведен первый вебинар (из 16) курса «Multicore programming in Java». Вебинары, видео в записи, исходный код программ и проверка заданий доступны только записавшимся на курс (запись еще открыта, свяжитесь по контактам внизу страницы). Но тут я бы хотел опубликовать материалы, упоминавшиеся на лекции: ссылки на источники, термины, картинки, задание. Возможно кто-то сочтет их полезными для себя.

Введение

- Закон Мура, Moore’s law

- Herb Satter, “The Free Lunch Is Over”

- Закон Амдала, Amdahl’s law

“Железо”

Стоит «посмотреть картинки» в следующих источниках

- «What Every Programmer Should Know About Memory»

- «The Architecture of the Nehalem Processor and Nehalem-EP SMP Platforms»

- «A Primer on Memory Consistency and Cache Coherence»

Учебники

Maurice Herlihy, Nir Shavit, “The Art of Multiprocessor Programming”: «Hardware Basics» page 469-482

«Картинки»

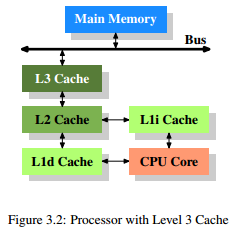

Memory hierarchy #1

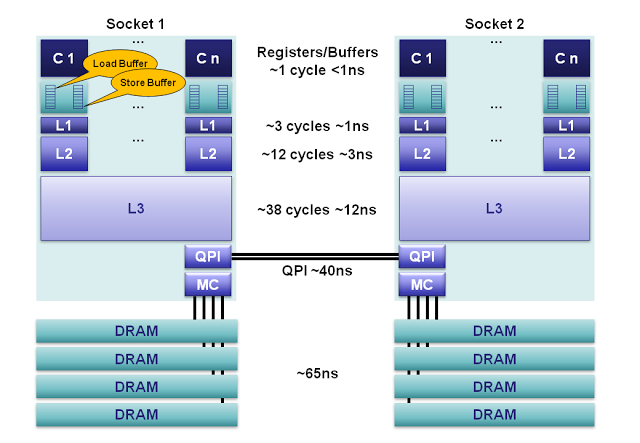

Memory hierarchy #2

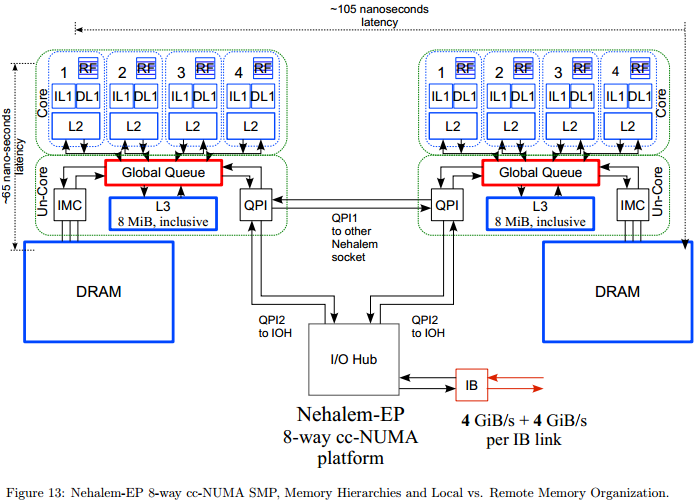

Memory hierarchy #3

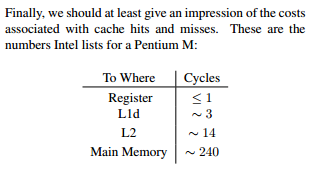

Типичное время доступа к разным уровням памяти

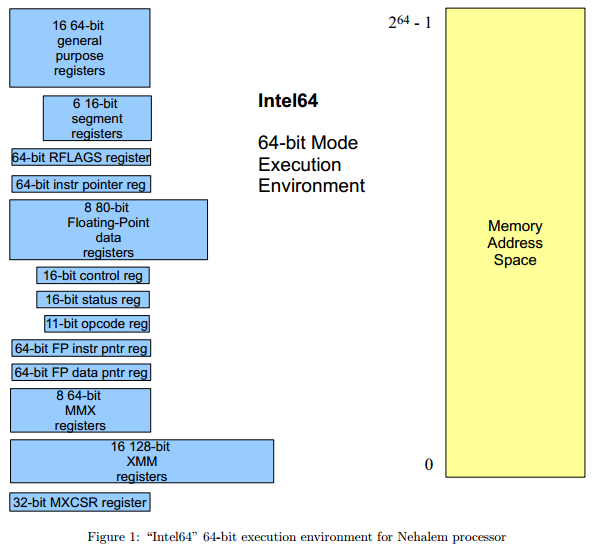

Примеры регистров конкретного процессора

Схематичное взаимодействие контроллеров кэшей

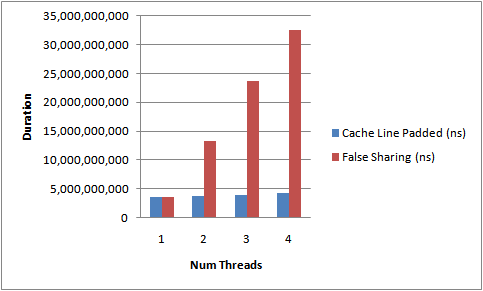

False sharing: код

False sharing: эффект (отрицательная масштабируемость)

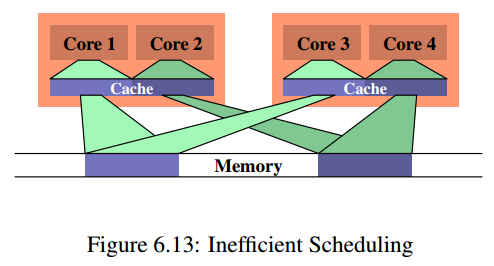

Плохое соответствие между ядрами, кэшами и данными

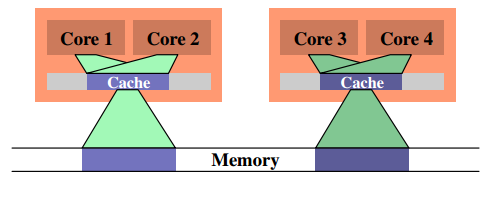

Хорошее соответствие между ядрами, кэшами и данными

Термины

Термины

CPU, core, multicore era, memory wall, memory hierarchy, registers, L1/L2/L3 caches, cache line, false sharing, memory padding, cache pollution, cache miss, SMP, NUMA, multisocket, thread affinity

Что читать по терминам

— Mechanical Sympathy: «CPU Cache Flushing Fallacy»

— Mechanical Sympathy: «Memory Access Patterns Are Important»

— Mechanical Sympathy: «False Sharing»

— Mechanical Sympathy: «False Sharing && Java 7»

— Руслан Черемин: «False sharing»

— Руслан Черемин: «Cache coherency #3: false sharing»

— Руслан Черемин: «How caching affects hashing»

Задание к Лекции #1

Написать утилитарный класс (в варианте A или в обоих вариантах (А и В)), который возвращает следующие характеристики процессора

— размер кэш-линии

— количество и размеры кэшей (L1, L2, L3)

— количество ядер

— определяет SMP или NUMA архитектура

A) путем «постановки программных экспериментов». Рекомендуется прочитать статью «Gallery of Processor Cache Effects» (на лекции #2 разберем примеры из статьи и наметим пути решения задачи)

B) путем использования JNA для вызовов API операционной системы

public class HardwareSpy {

public int cacheLineSize() {...}

public int cacheL1Size() {...} // -1 если считается, что нет L1

public int cacheL2Size() {...} // -1 если считается, что нет L2

public int cacheL3Size() {...} // -1 если считается, что нет L3

public int coreCount() {...}

public int isSMP() {...}

public int isNUMA() {...}

}

Контакты

skype: GolovachCources

email: GolovachCources@gmail.com

Автор: IvanGolovach