Многие знакомы со словом «JTAG», но знакомство это скорее всего поверхностное. В этой статье я хочу перевести Вас на новый уровень, так сказать «во френдзону». Возможно, для многих я не открою ничего нового, но надеюсь тем, кто давно хотел ознакомиться, будет интересно почитать. Итак, от винта.

Введение

В 1985 сформировалась группа производителей электроники — JTAG (Joint Test Action Group). Для решения проблем тестирования в 1990 был выдвинут промышленный стандарт — спецификация IEEE Std 1149.1-1990 (IEEE Standard Test Access Port and Boundary-Scan Architecture). В этом же году Intel вывел в свет первый процессор с JTAG — 80486. С тех пор стандарт постоянно модифицируется и, в данный момент, последняя версия датируется 2013 годом.

«А какие же это проблемы с тестированием?»,- спросите Вы. Ну как же! Мало удовольствия прыгать с осциллографом по выводам микросхемы, особенно если их много больше двух! Стандарт позволяет значительно упростить жизнь за счет встраивание специальной архитектуры в современные чипы, обеспечивающей доступ к выводам (точнее, к специальным блокам ввода-вывода) с помощью 4-х проводного последовательного интерфейса. Эта архитектура позволяет не только контролировать их состояние, но и управлять ими. Таким образом можно обойтись без громоздких пробников с физическим контактом и насладиться всей прелестью этапа отладки цифровых микросхем или устройств уровня печатной платы.

Стандарт используют как для целей внутрисхемного программирования и отладки программ, так и при работе с корпусированными микросхемами. Он же используется для проверки на качество припайки микросхем к плате, межплатного и внутристоечного монтажа плат и блоков. Также надо сказать ему спасибо за восстановление закирпиченных по неосторожности мобильных устройств.

И как же работает?

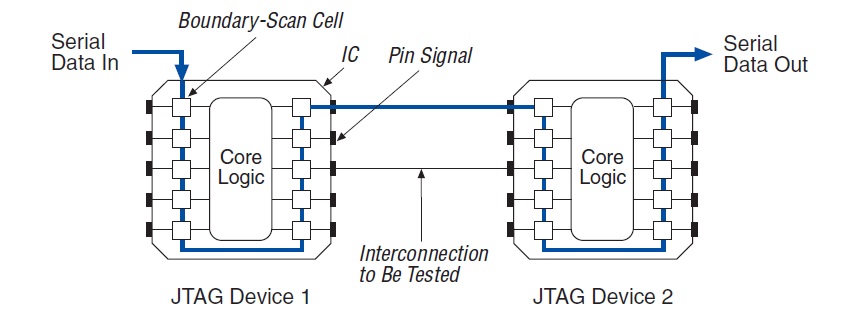

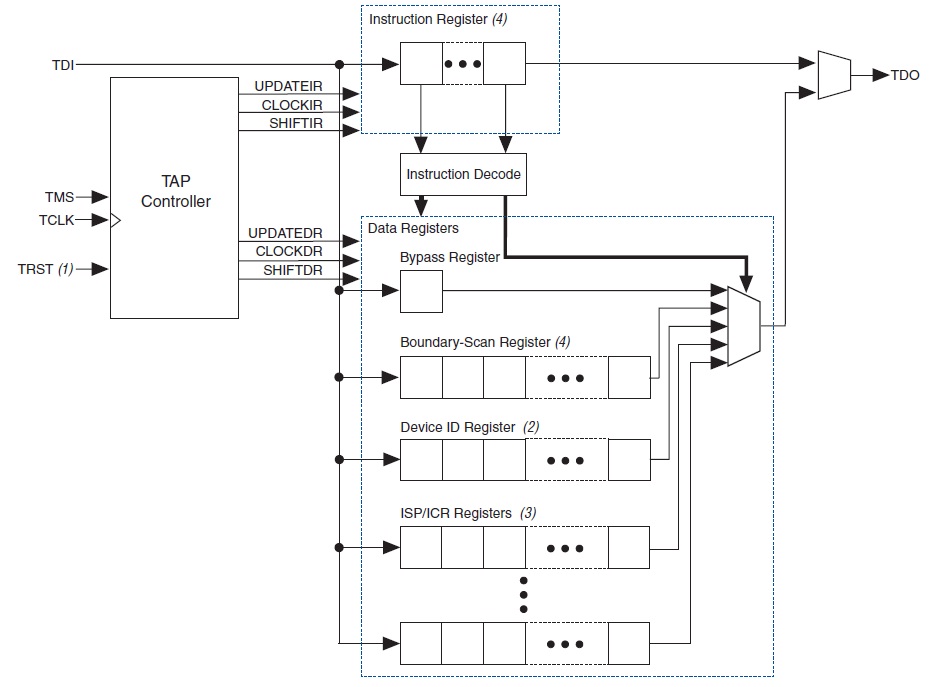

Механизм граничного сканирования заключен, всего лишь, в сдвиговом регистре (Boundary Scan), подключенном между выводами микросхемы и ядром, и мультиплексоре который подключает в нужный момент этот регистр. Каждому конкретному выводу соответствуют так называемые «ячейки».

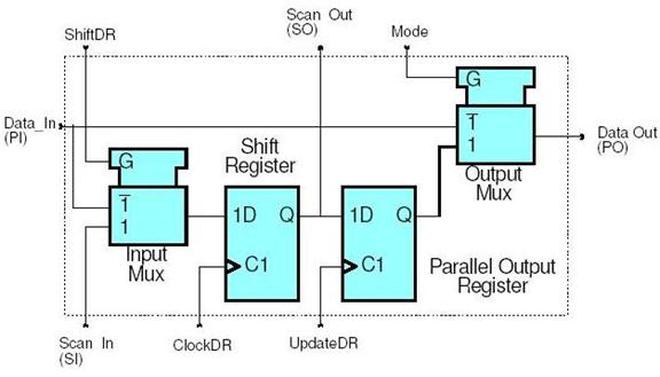

В состав ячейки входит один триггер регистра граничного сканирования и мультиплексора выбора данных. Ячейки могут быть разных типов в зависимости от вывода микросхемы и команд интерфейса, т.е. зависит от производителя той или иной микросхемы. Производители не придерживаются строго стандарта и, поэтому, развелось множество модификаций.

На рисунке представлена одна из разновидностей ячейки. PI, PO — параллельные вход и выход, SI,SO — последовательные.

Сигналы на регистр микросхемы попадают через мультиплексор, который позволяет считывать как состояния выводов ядра микросхемы (инструкция INTEST), так и данные, поступающие извне на сдвиговый регистр (инструкция EXTEST). Разновидности инструкций и их функциональность опять же меняются от желаний производителя, но существуют так называемые обязательные:

- EXTEST — инструкция, позволяющая за счет установки логических значений на рабочих контактах электронных компонентов проверить внешние цепи, имеющие непосредственное отношение к тестируемому компоненту.

- INTEST — инструкция обеспечивает возможность установки логических значений внутри микросхемы, то есть на входах ядра, тем самым проверяя его.

- SAMPLE_PRELOAD — позволяет тестировать ядро электронного элемента в статическом режиме, устанавливая значения логических уровней на границе его выходных буферов.

- BYPASS — инструкция, при которой наш регистр граничного сканирования «схлопывается» в один триггер. При этом данные со входа (TDI) на выход (TDO) передаются с задержкой в один такт частоты синхронизации интерфейса (TCK). Этот режим позволяет эффективно использовать возмодности последовательного интерфейса при организации длинных последовательно объединенных цепочек.

- IDCODE — инструкция выдвигает на выход значение встроенного 32-битного регистра с идентификаторами производителя, модели и версии устройства.

Сигнальные линии интерфейса

Как уже говорилось выше, интерфейс JTAG имеет следующие сигнальные линии:

- TDI — Test Data Input — сигнал данных на вход, данные задвигаются по переднему фронту TCK.

- TDO — Test Data Output — выход последовательных данных JTAG, выдвигаются по заднему фронту TCK, должен находиться в третьем состоянии — Z — когда данные не передаются.

- TMS — Test Mode Select — сигнал управления TAP — контроллером.

- TRST — Test Reset — не всегда есть, так как ресета можно добиться удерживая некоторое время TMS = 1, активный уровень сигнала — 0.

- TCK — Test Clock — тактовая частота.

JTAG — синхронный интерфейс, сигналы принимаются по переднему фронту синхроимпульсов младшими битами вперед и только в течении состояний TAP — контроллера Shift-DR Shift-IR. Выходные данные выдвигаются по заднему фронту.

TAP — контроллер

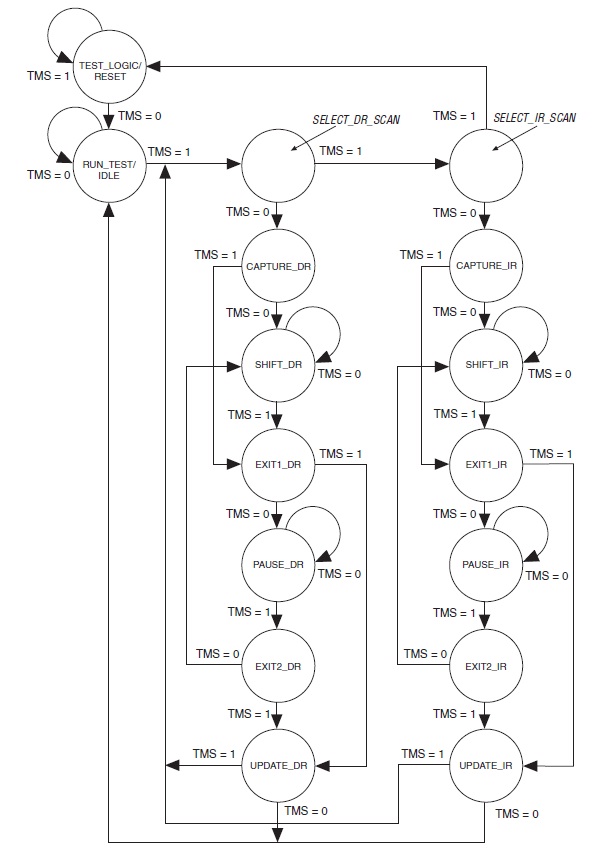

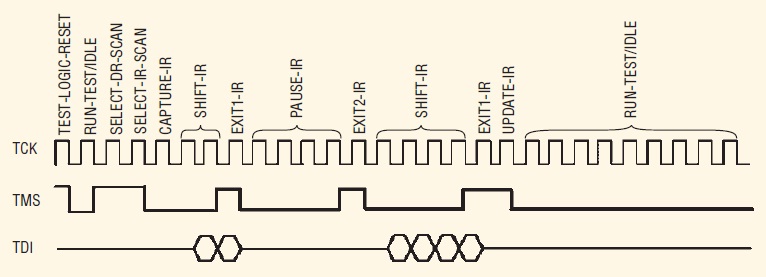

Мы добрались до самой сути JTAG, а именно — управляющий работой автомат. С его помощью собственно и живет всё вокруг. Автомат имеет 16 состояний. Управление интерфейсом осуществляется путем воздействия на автомат посредством сигнала TMS. Переходы происходят по переднему фронту сигнала TCK. Чтение и запись данных происходят одновременно. Ниже привожу иллюстрацию работы, взятую из документации микросхем фирмы Altera.

Диаграмма переходов автомата, управляющего режимами TAP

Состояния диаграммы переходов:

- Test-Logic-Reset – исходное состояние;

- Run-Test/Idle – переходное состояние контроллера при выполнении тестов или ожидании следующей

- команды;

- Select-IR, Select-DR – состояние, после которого будет производиться тестирование команд, данных;

- Capture-IR, Capture-DR – состояние приёма команд, данных;

- Shift-IR, Shift-DR – состояние сдвига команд, данных;

- Exit1-IR, Exit2-IR – выход из режима работы с командами;

- Exit1-DR, Exit2-DR – выход из режима работы с данными;

- Pause-IR, Pause-DR – состояние паузы;

- Update-IR, Update-DR – состояние перезаписи данных в выходные регистры.

DR — действия происходят над данными, IR — соответственно над инструкциями.

Исходное состояние, в котором находится автомат после включения, это Test-Logic Reset. Пока сигнал TMS имеет значение «лог.1», состояние автомата остается неизменным. В этом состоянии, по умолчанию, выбрана инструкция IDCODE или BYPASS.

Сигнал сброса TRST не является обязательным, поэтому для сброса автомата в исходное состояние применяют следующую процедуру. Необходимо подать на вход TMS сигнал высокого уровня и удерживать его не менее 5 тактов частоты TCK. Если сигнал TMS будет установлен хостом в низкий уровень, то автомат перейдёт к состоянию Run-Test/Idle (активное состояни, в котором ничего не происходит). Обычно из этого состояния можно перейти в состояние Select-IR, для того чтобы загрузить в контроллер новую инструкцию. Но если на вход сигнала TMS подействует не сигнал, подаваемый от хоста, а помеха низкого уровня, то, как и в предыдущем случае, автомат перейдёт в состояние Run-Test/Idle. Если же кратковременная помеха (длительностью не более одного периода синхрочастоты) прекратится, то автомат через три такта снова вернётся в исходное состояние – Test-Logic Reset.

Чтобы загрузить в контроллер новую команду, надо из состояния Run-Test/Idle перевести автомат в состояние Select-IR, Capture-IR, Shift-IR. Затем необходимо «продвинуть» в цепочку данных новую команду, а потом перевести автомат через состояния Exit1-IR, Update-IR и снова в Run-Test/Idle. Логика работы с данными такая же. Нужно учитывать, что сигнал высокого уровня при переходе из состояний Shift-IRDR подается вместе с последним битом информации.

Диаграмма сигналов при выполнении переходов для загрузки команды

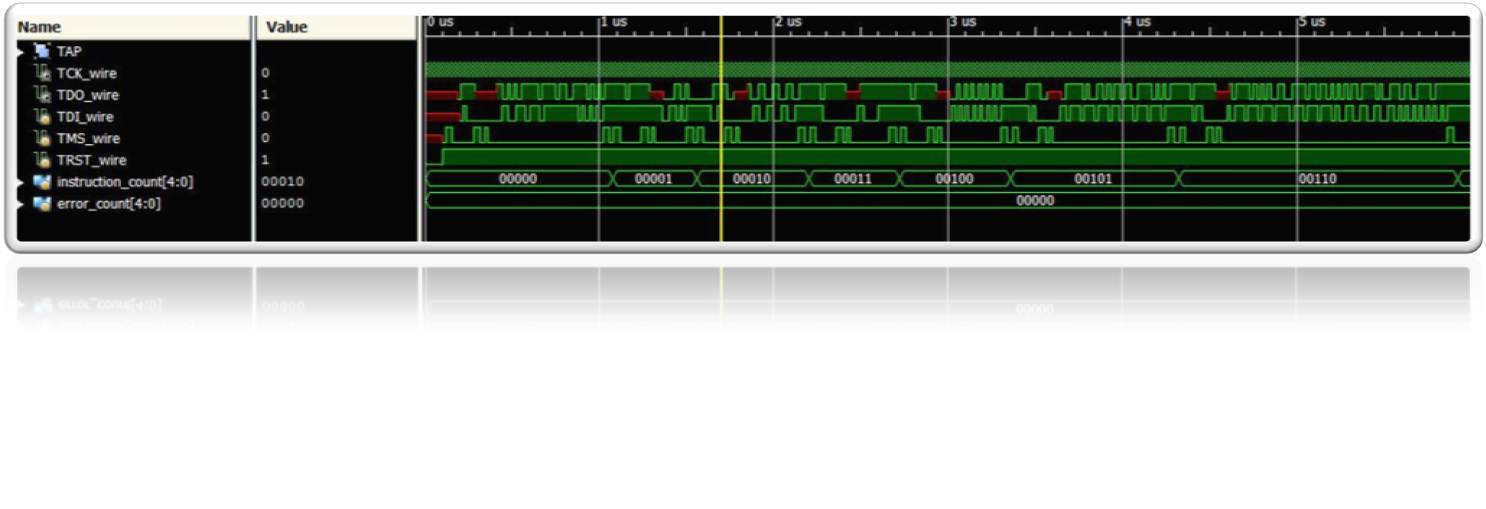

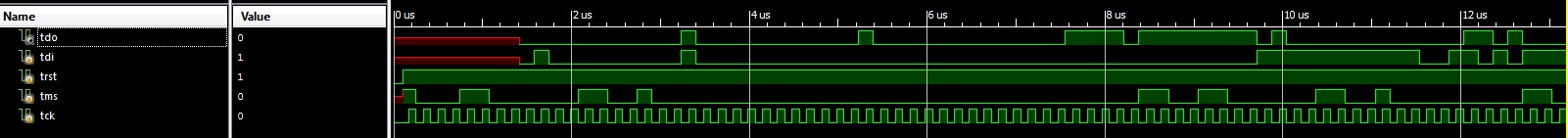

Если использовать САПР фирмы Xilinx — ISE Design Suit и написать код работы JTAG на Verilog, то результирующая диаграмма будет выглядеть примерно так:

Сылка на дропбокс, картинка в полный размер

Наконец можно показать полную структурную схему устройства JTAG и Вы вполне должны в ней разобраться:

… И в заключение...

Использование JTAG и технологии граничного сканирования в микросхеме, на плате или в устройстве добавляет стоимость и увеличивает время разработки проекта. Но, всё же эти затраты легко окупаются при проведении тестирования, которое обеспечивается на каждой стадии цикла жизни изделия. То, что было первоначально разработано как производственный испытательный инструмент, используется до начала производства, во время серийного производства и после производства, то есть на этапе эксплуатации конечным пользователем. Кроме непосредственно граничного тестирования, проектировщики используют технологию JTAG для того, чтобы производить самотестирование (BIST) (в тех компонентах, где оно реализовано) и загружать внутренние значения в регистры устройства или программировать микросхемы ПЗУ. Тесты, которые были разработаны и использованы на этапе проектирования, могут быть переданы производству, для того чтобы обеспечить дополнительное снижение стоимости и времени на проверку изделий при выходном контроле.Основные положительные эффекты от применения технологии JTAG в производственной фазе – экономия времени при разработке испытательных тестов, улучшенный «охват» тестируемого изделия при поиске ошибки и диагностировании и улучшенная производительность испытаний при одновременном уменьшении времени испытания.

Применение граничного сканирования при эксплуатации изделия также даёт определённый положительный эффект. Отказы при эксплуатации часто происходят из-за структурных отказов, которые вызываются повышенной температурой, влажностью, вибрацией. Используя граничное сканирование, техники имеют возможность быстро проверить изделие на структурные ошибки вплоть до уровня компонентов без трудоёмкого исследования или возвращения платы изготовителю на завод.

Литература:

Wiki

Boundary-scan in Altera devices

офф. страница рабочей группы стандарта IEEE 1149.1

1149.1-2013 — IEEE Standard for Test Access Port and Boundary-Scan Architecture

Хорошая хабро-статья, в которой затронуто JTAG тестирование

В статье использовались некоторые данные из журнала «Современная электроника» выпуск №2 2007.

Автор: Levard