«Самоделкиных» было много всегда. С появлением сети любители сделать что-то своими руками тут же самоорганизовались, и создали массу разного рода сообществ, форумов и прочих мест, где можно пообщаться с себе подобными. Благодаря этому в Интернете регулярно появляются интереснейшие работы, на некоторые из которых стоит обратить самое пристальное внимание.

Одной из таких работ является, в частности, проект по созданию дискретного 8-битного компьютера. Автор проекта — Andrew Starr, а сам проект располагается вот на этой страничке. Что собой представляет проект?

По словам автора, это частично кинетическая скупльтура, частично — дань достижениям науки и техники, причем достижениям прошлых лет. Частично же это образовательный проект.

Для создания этой системы автор использует следующие элементы:

- 8-битная шина;

- 2*64 битные стеки (data, return);

- Гарвардская архитектура: 256 байтная основная память и программная память на 256 слов;

- 13-разрядное программное командное слово: 5 бит на опкод, 8 бит — операнд;

- Все элементы памяти изготовлены с использованием ферритовых сердечников;

- Программная память выполнена с использованием ферритовых трансофрматоров;

- Логические элементы выполнены из дискретных элементов, в виде plug-in модулей;

- Целевая тактовая частота — 1 МГц.

В гарвардской архитектуре характеристики устройств памяти для инструкций и памяти для данных не обязательно должны быть одинаковыми. В частности, ширина слова, тактирование, технология реализации и структура адресов памяти могут различаться. В некоторых системах инструкции могут храниться в памяти только для чтения, в то время как для сохранения данных обычно требуется память с возможностью чтения и записи. В некоторых системах требуется значительно больше памяти для инструкций, чем памяти для данных, поскольку данные обычно могут подгружаться с внешней или более медленной памяти. Такая потребность увеличивает битность (ширину) шины адреса памяти инструкций по сравнению с шиной адреса памяти данных.

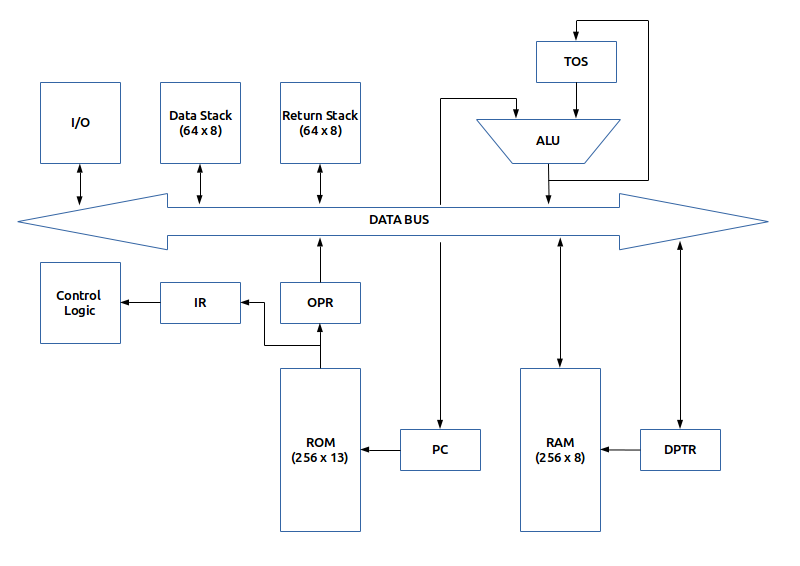

Архитектура системы:

Здесь используется стандартная 2-х стековая машина с несколькими модификациями, позволяющими использовать гарвардскую архитектуру и опциональное поле данных в инструкции.

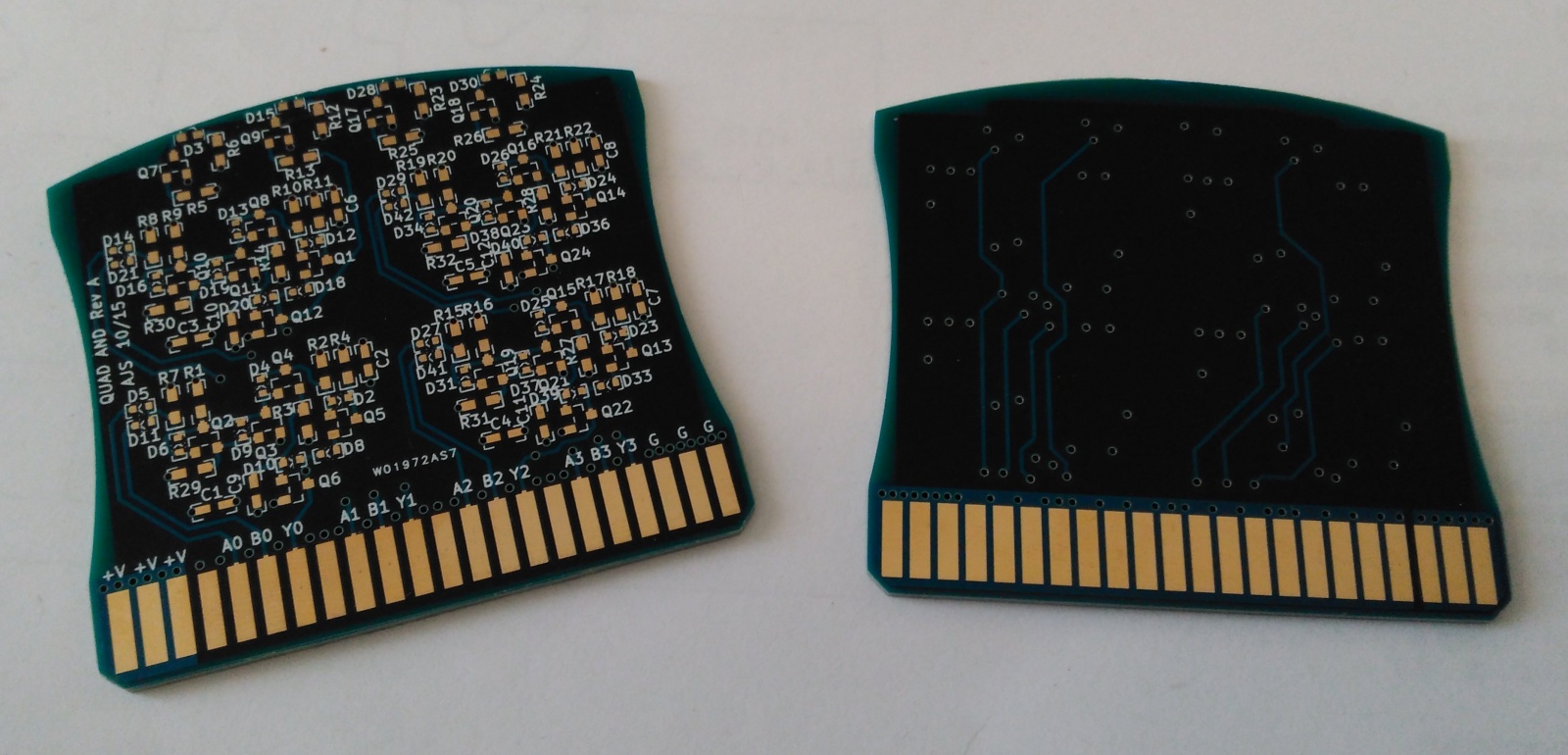

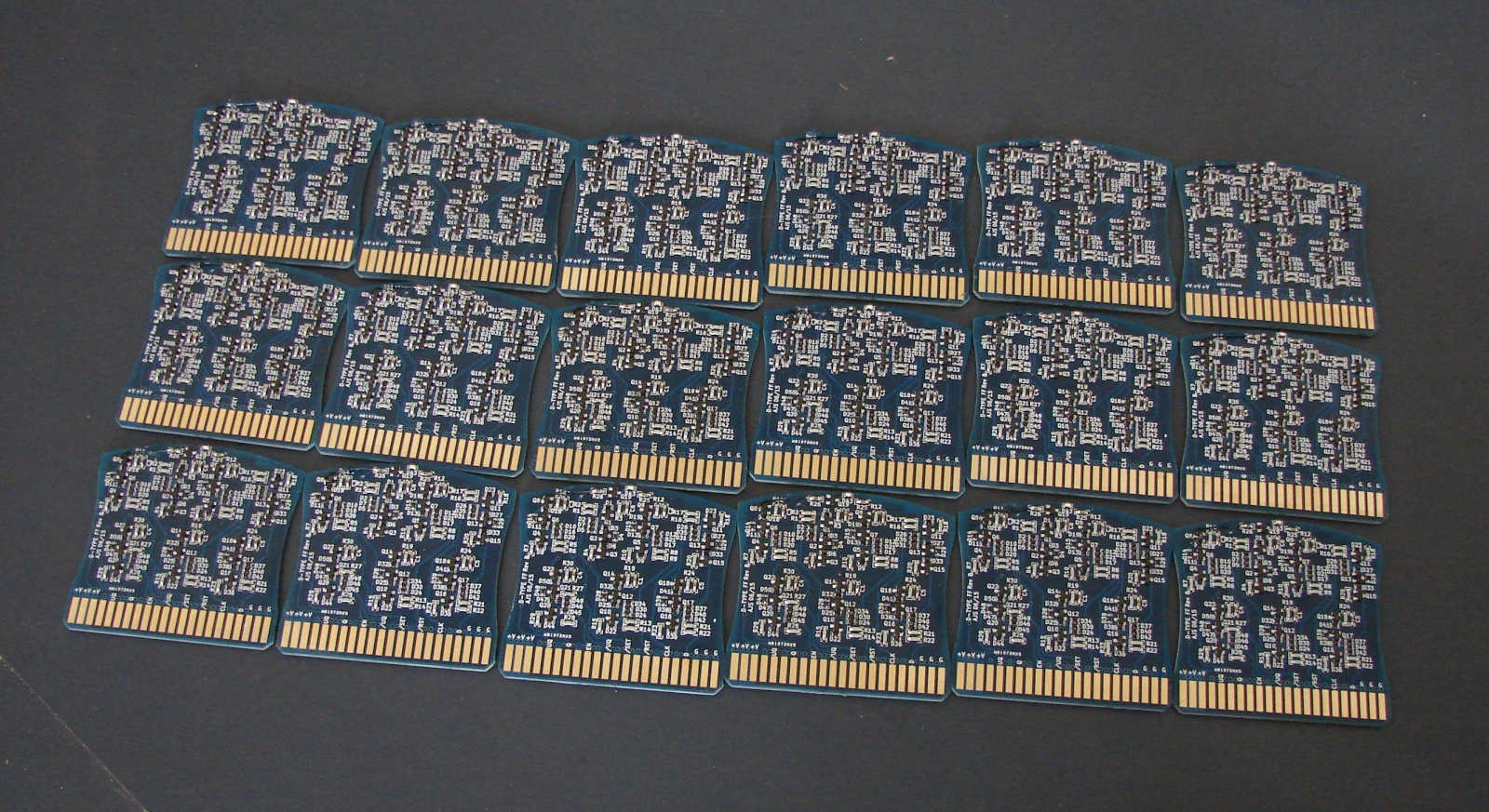

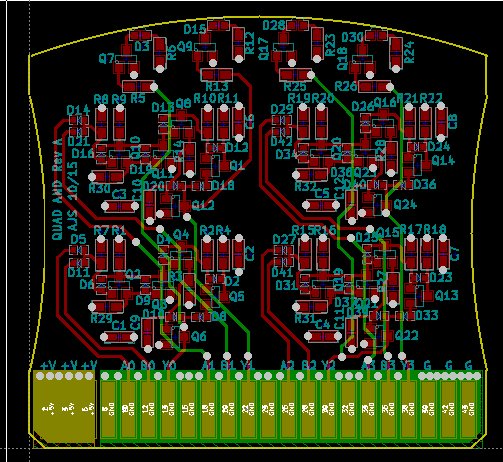

Сейчас автор уже разработал схему AND -модуля, и заказал соответствующие модули, которые и прибыли на днях.

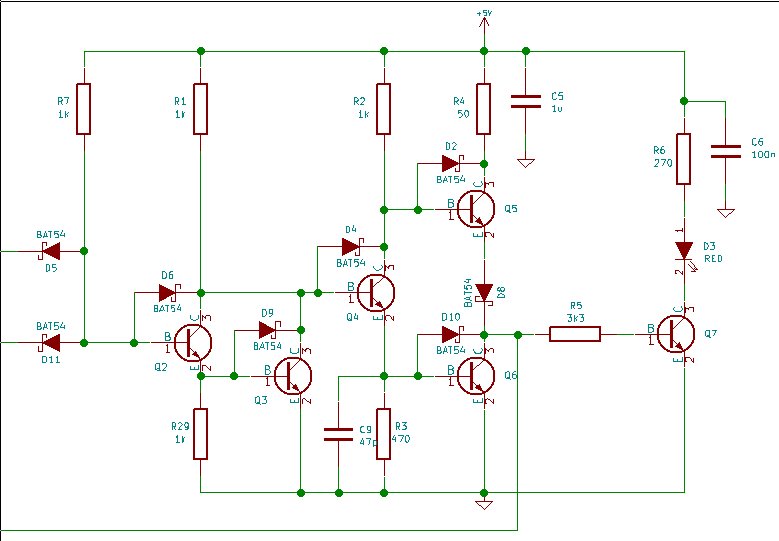

Схемы

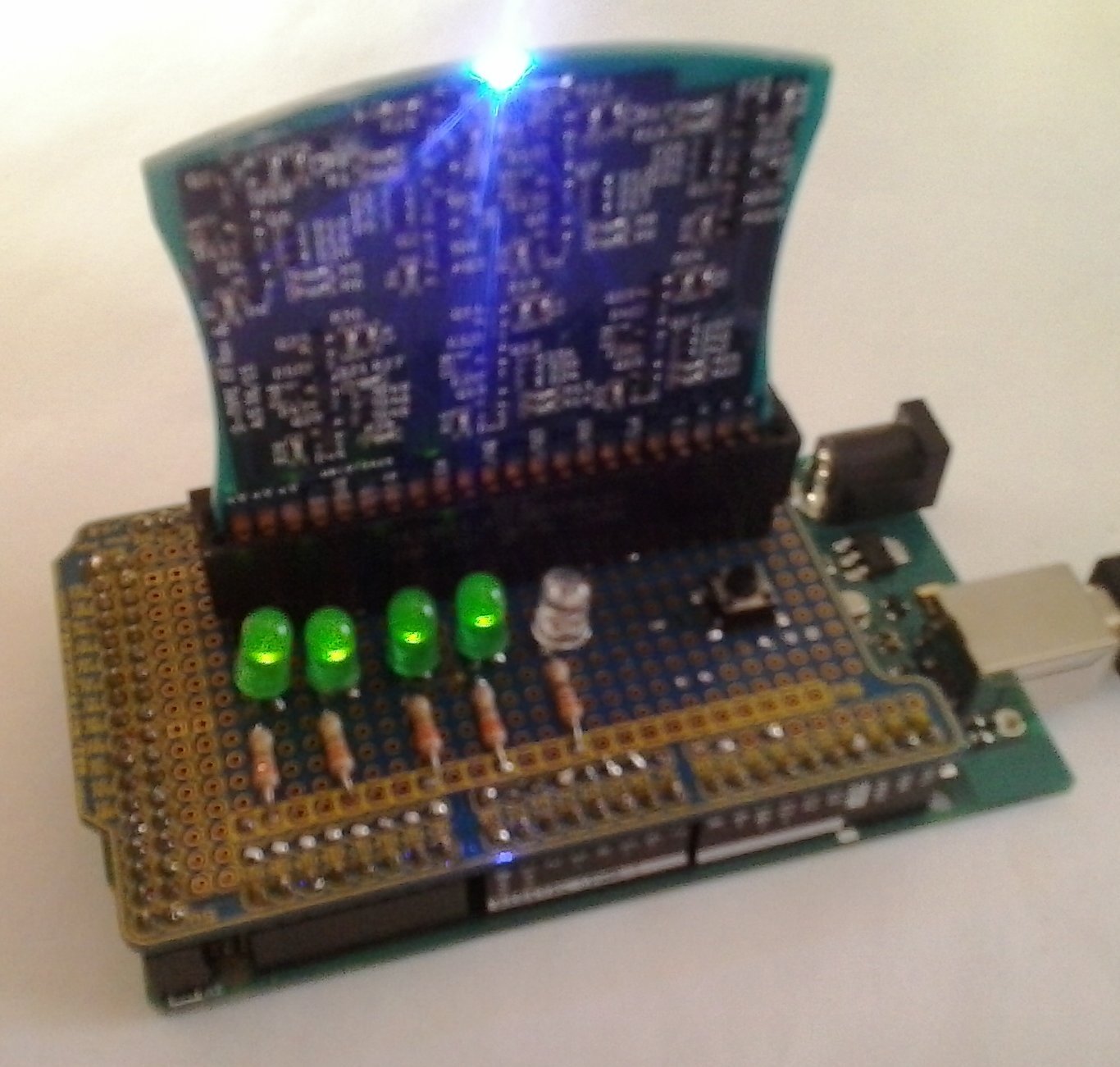

Тестирование:

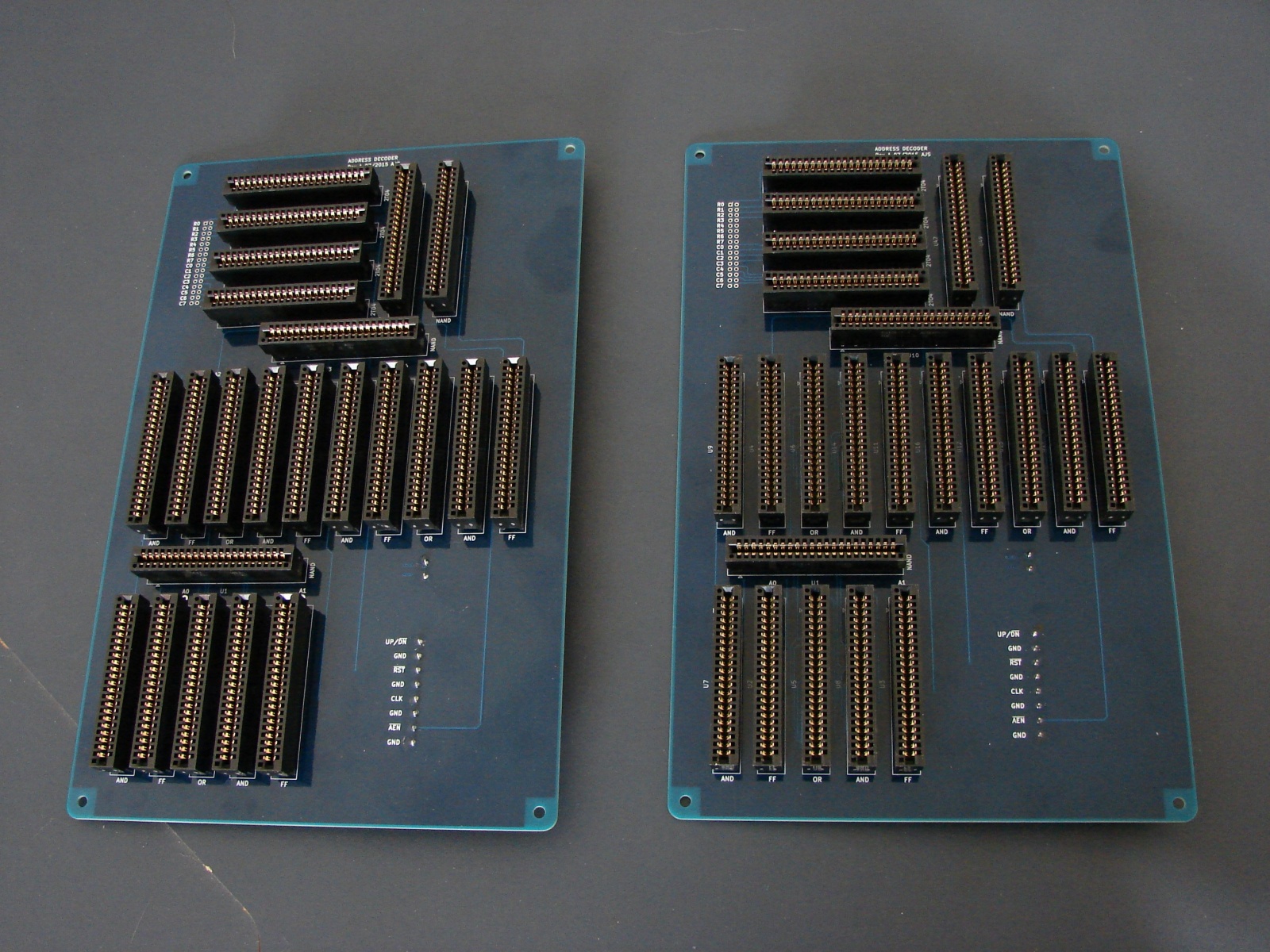

Готовы уже и прочие компоненты, включая дешифраторы адреса для стековой памяти.

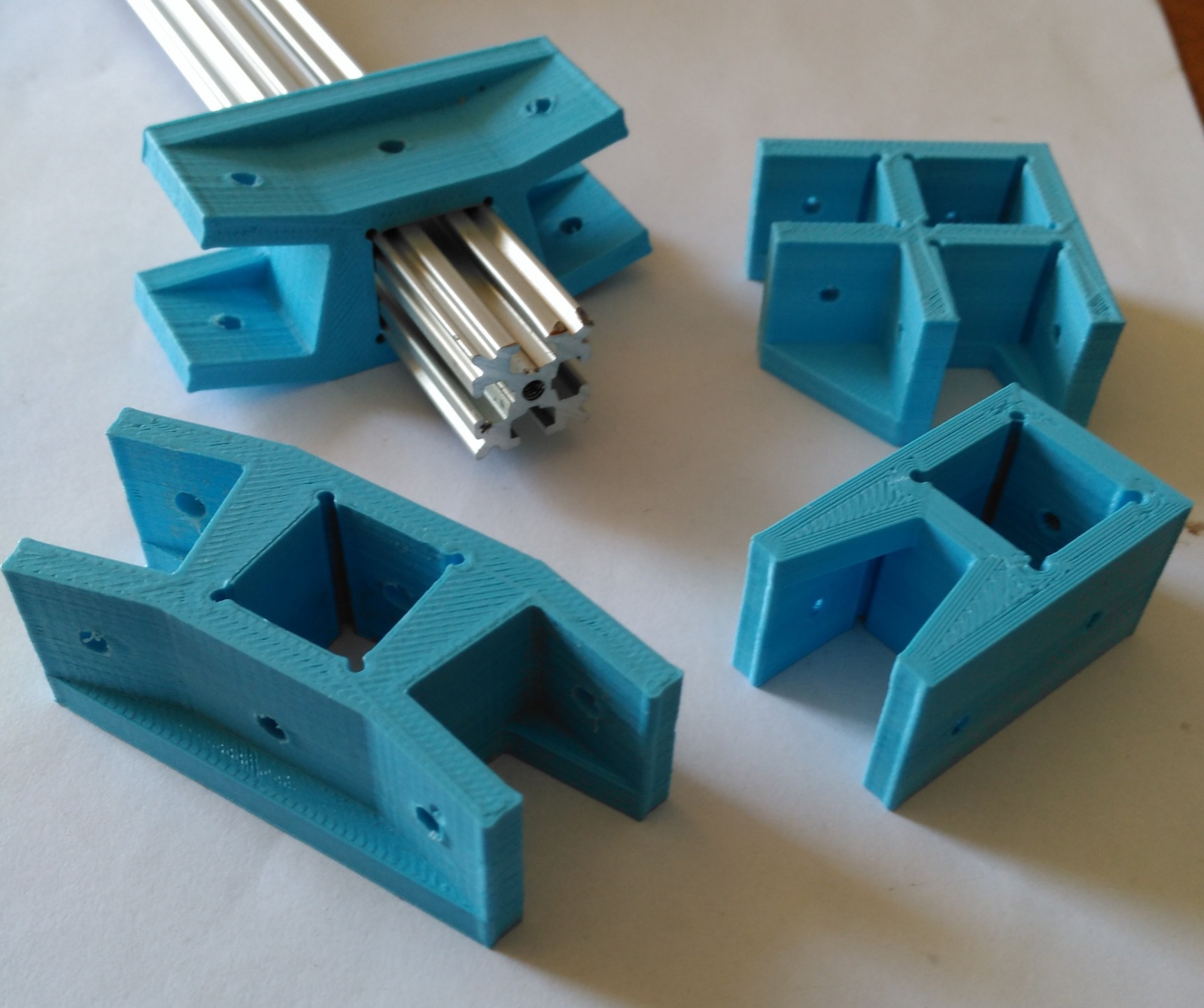

Кроме всего прочего, автор сейчас разрабатывает и корпус для своего творения:

Сейчас работа еще продолжается, так что следить за реализацией проекта можно здесь.

Автор: marks