На конференции 2018 IEEE International Electron Devices Meeting (IEDM) представители бельгийского исследовательского центра Imec продемонстрировали доказательство эффективности магниторезистивной памяти SST-MRAM для использования в качестве разделяемой кеш-памяти вместо традиционной памяти SRAM. Для этого была разработана модель массива SST-MRAM и выпущен опытный чип, на котором были проведены все необходимые измерения.

Следует отметить, что опытный массив памяти SST-MRAM выпущен с использованием 5-нм техпроцесса. Для производства был использован 193-нм сканер и однопроходная иммерсионная литография (с погружением в жидкость). Тем самым разработчики доказали, что процесс производства массива кеш-памяти SST-MRAM с технологическими нормами 5 нм может быть достаточно недорогим.

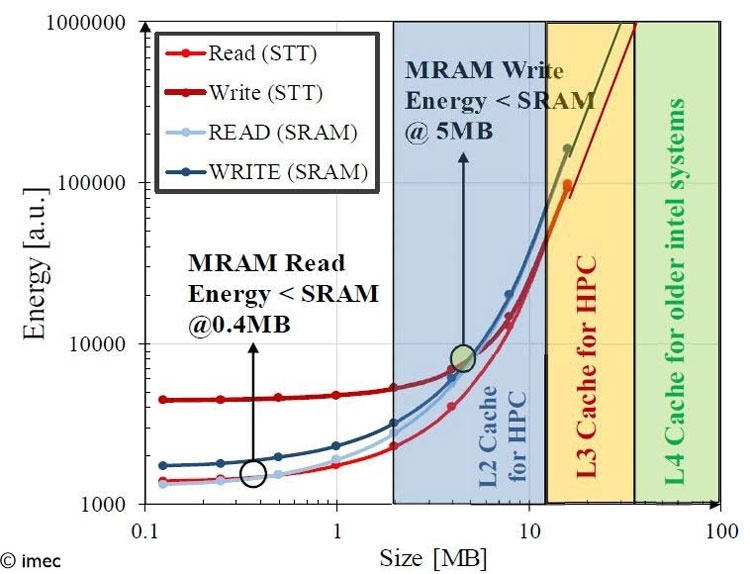

Сначала с помощью расчёта, а затем путём замеров был составлен график зависимости потребления массива кеш-памяти SST-MRAM и SRAM в зависимости от объёма памяти. Выяснилось, что в случае ёмкость 0,4 Мбайт память SST-MRAM становится эффективнее памяти SRAM в режимах чтения, а при наборе ёмкости 5 Мбайт потребление в режиме записи памяти SRAM начинает превышать потребления в режиме записи памяти SST-MRAM. Это означает, что в техпроцессах 5 нм память SST-MRAM невыгодно использовать для кеш-памяти первого и второго уровней, тогда как для кеш-памяти третьего уровня, обычно разделяемой, это эффективная замена SRAM. К тому же память SST-MRAM является энергонезависимой, что добавляет ей очков при сравнении с обычной оперативной памятью.

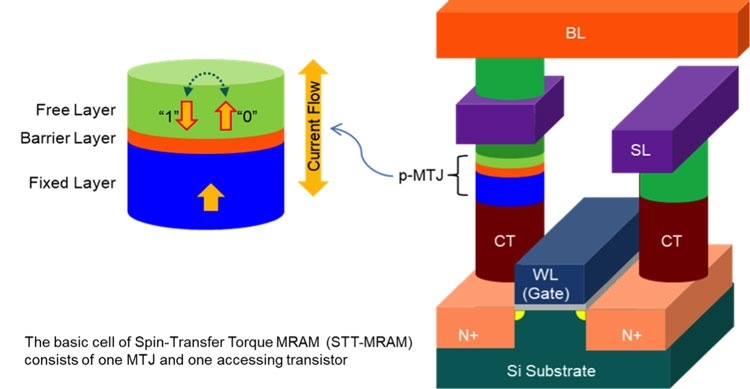

Остаётся напомнить, что ячейка памяти SST-MRAM представляет собой бутерброд из диэлектрика, заключённого между двумя слоями с намагниченностью: одну с фиксированной, а вторую — с переменной. В зависимости от поляризации тока свободный слой меняет направление намагниченности благодаря движению через него электронов с заданным вращающим моментом. Использование SST-MRAM вместо SRAM решает также другую задачу — это увеличения плотности ячеек памяти. Эксперимент показал, что в рамках 5-нм техпроцесса ячейка SST-MRAM занимает примерно 43,3 % от площади ячейки SRAM.