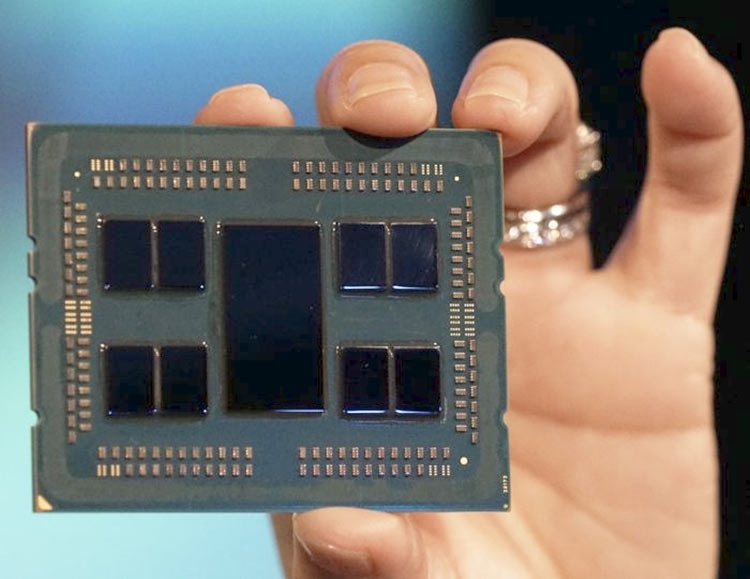

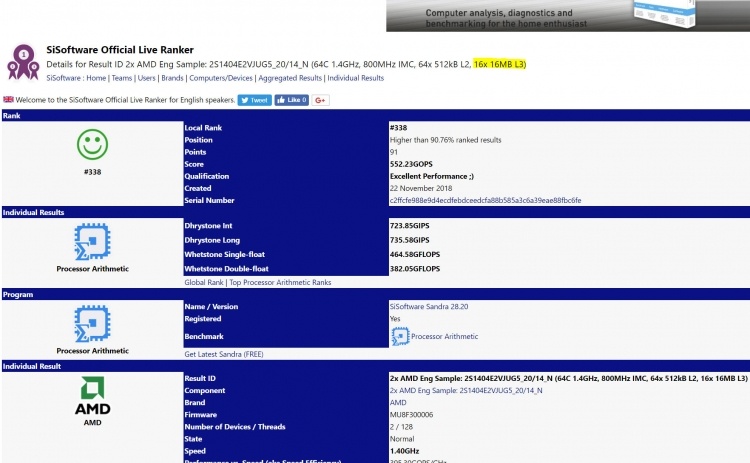

Обнаруженная в базе данных тестового пакета SiSoftware Sandra запись, касающаяся двухпроцессорной системы на базе серверного процессора AMD EPYC семейства Rome, проливает свет на иерархию кеш-памяти этого чипа. Напомним: каждый 64-ядерный процессор EPYC Rome состоит из восьми 7-нм 8-ядерных чипов («чиплетов») с архитектурой Zen 2, которые объединены 14-нм контроллером ввода-вывода (модуль I/O), отвечающим за работу с памятью, связь между чиплетами и PCIe-соединения.

В результате теста упоминается следующая иерархия кеш-памяти: выделенный кеш L2 объёмом 512 Кбайт на каждое ядро и 16 по 16 Мбайт кеша L3. Как и CPU-Z, Sandra умеет отображать распределение кеш-памяти L3. Для процессора Ryzen 7 2700X пакет сообщает, что кеш-память L3 распределена по принципу 2 x 8 Мбайт, что соответствует общему кешу L3 объёмом по 8 Мбайт на каждый 4-ядерный блок CCX.

В каждом 64-ядерном процессоре Rome имеется в общей сложности 8 чиплетов. Если Sandra верно сообщает распределение кеша L3, то, по-видимому, каждый из этих 8-ядерных кристаллов по-прежнему разделён на два четырёхъядерных блока CCX. В свою очередь один CCX получает 16 Мбайт общего кеша L3.

Это удвоение объёма буферной памяти L3 на каждом CCX, вероятно, призвано несколько компенсировать проблемы, вызываемые задержками при передаче данных между 8-ядерными чиплетами и кристаллом ввода/вывода в новых серверных процессорах EPYC. Это особенно важно, поскольку 8-канальный контроллер памяти DDR4 расположен именно на этом 14-нм кристалле.