Ранее в этом году Cadence и Micron провели первую в отрасли публичную демонстрацию работы оперативной памяти (dynamic random access memory, DRAM) следующего поколения — DDR5. На мероприятии TSMC в начале этого месяца компании представили дополнительную информацию как о стандарте в целом, так и о разработке решений на его базе. Оказывается, окончательная спецификация DDR5 ещё не была принята JEDEC, но Micron всё ещё планирует начать производство чипов памяти DDR5 в конце 2019 года.

Как отмечалось ещё в мае, основной особенностью DDR5 SDRAM является увеличенная ёмкость микросхем, а не только более высокая производительность и низкое энергопотребление. Разумеется, DDR5 обеспечит скорость работы интерфейса от 4266 до 6400 МТрансферов/с, её напряжение питания снизится до 1,1 В с допустимым диапазоном колебаний 3 % (т. e. на ± 0,033 В) и будет использовать два независимых 32/40-разрядных канала на модуль (без/или с ECC). Кроме того, DDR5 увеличит эффективность командной шины (поскольку оба независимых канала будут иметь свою собственную 7-разрядную шину адресов (Add) и команд (Cmd)), получит лучшие схемы обновления, а также увеличенное количество групп банков для дополнительного увеличения производительности. Примечательно, что в Cadence говорят о том, что технологические усовершенствования DDR5 позволят увеличить реальную пропускную способность памяти на 36 % по сравнении с DDR4 даже при скорости передачи данных 3200 МТ/с, а после того, как DDR5 заработает на проектных скоростях вроде 4800 МТ/с, фактическая пропускная способность станет на 87 % выше, чем у DDR4-3200 (другой вопрос, какие при этом будут задержки). Тем не менее, одной из ключевых особенностей DDR5 станет именно возможность увеличивать плотность монолитной микросхемы памяти свыше 16 Гбит.

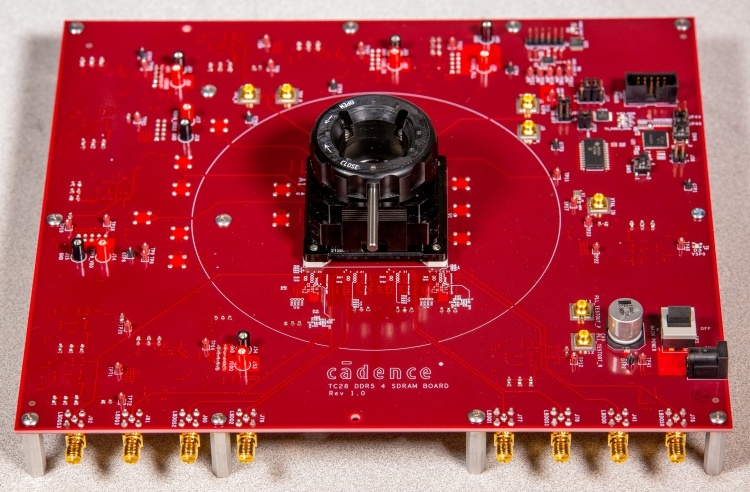

Прототип контроллера памяти компании Cadence

Ведущие производители оперативной памяти уже имеют в своём арсенале монолитные чипы DDR4 ёмкостью 16 Гбит, но эти устройства не могут предложить действительно высоких тактовых частот или скоростей ввода/вывода из-за законов физики. По этой причине компаниям вроде Micron предстоит проделать немалую работу, чтобы объединить высокую производительность и плотность ячеек DRAM. В частности, в Micron обеспокоены непостоянным временем удержания заряда ячейками памяти, а также другими феноменами на уровне атомов для микросхем памяти, произведённых по технологическим процессам 10–12 нм. При этом в случае с DDR5 шина Add/Cmd уже имеет встроенную терминацию, призванную сделать сигналы более чистыми и увеличить стабильность при высоких скоростях передачи данных. Кроме того, модули памяти высокой ёмкости будут экипироваться собственными регуляторами напряжения и управления питания. Таким образом, хотя стандарт DDR5 и адаптирован к тому, чтобы объединить производительность и плотность, компаниям вроде Micron потребуется проявить своё мастерство при изготовлении соответствующих микросхем.

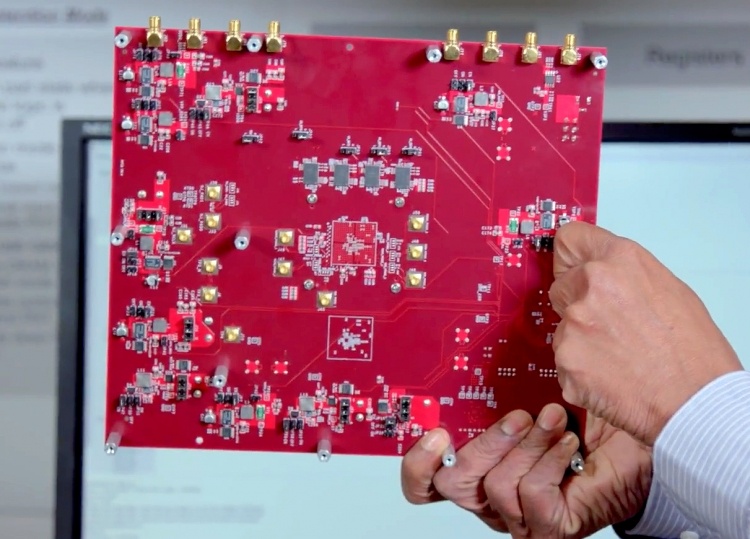

Микросхемы памяти DDR5 производства Micron

Micron рассчитывает начать производство чипов памяти DDR5 ёмкостью 16 Гбит с использованием техпроцесса с «шириной затвора менее 18 нм» уже в конце 2019 года. Впрочем, это не означает, что одновременно с этим появятся приложения, использующие новую DRAM. В свою очередь, Cadence уже предлагает готовый блок DDR5 (контроллер + физический интерфейс), реализованный для техпроцессов TSMC N7 (7 nm, DUV) и N7+ (7 nm, DUV+EUV). Таким образом, у разработчиков систем на кристалле (system-on-chip, SoC) есть всё необходимое для создания совместимых с новым типом памяти SoC. Кроме того, в Cadence работают над соответствующими IP-блоками DDR5 и для более совершенных норм производства.

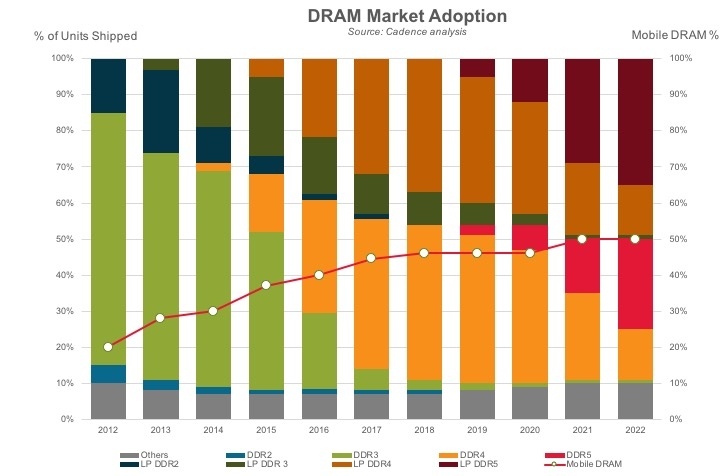

Предположения Cadence в области принятия DDR5 различными типами устройств

Учитывая ключевые преимущества DDR5, неудивительно, что серверы станут первыми устройствами, использующими новый тип оперативной памяти, согласно ожиданиям Cadence. Что особенно интересно, так это то, что в Cadence полагают, что SoC для клиентских компьютеров, произведенные по техпроцессу N7+, будут поддерживать DDR5. По сути, это означает, что подобные процессоры начнут появляться уже в 2020 году. Учитывая предсказываемые Cadence высокие темпы принятия DDR5 рынком, логично предполагать, что новый тип оперативной памяти будет поддержан широким спектром SoC.

Тенденции на рынке оперативной памяти по оценкам Cadence