Imec продолжает радовать разработками, открывающими путь к производству полупроводников с нормами менее 5–3 нм. Среди прочих докладов на симпозиуме VLSI Technology 2018 разработчики центра рассказали о найденной серии технологических цепочек, которая позволит выпускать комплиментарные пары полевых транзисторов с использованием технологических норм менее 3 нм (complementary FET, CFET). Процесс производства CFET по энергоэффективности и производительности транзисторов может в итоге превзойти техпроцесс FinFET применительно к технологическим нормам 3 нм. Более того, техпроцесс CFET открывает возможность уменьшить на 50 % размеры как стандартных (цифровых) ячеек, так и ячеек памяти SRAM.

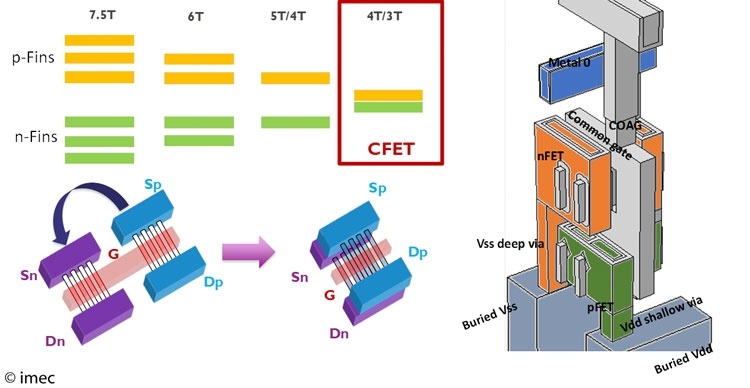

Слева указаны варианты строения ячеек (стандартной и SRAM), а справа — предложенная Imec комплиментарная структура из двух транзисторов

Напомним, что на использовании комплиментарных пар транзисторов базируется классические КМОП (CMOS) техпроцессы производства микросхем. Это транзисторы с разным типом проводимости (n и p), но идентичные или почти идентичные по параметрам. Разработчики Imec внесли смелое предложение создавать на кристалле комплиментарные транзисторы не рядом, а друг над другом. В предложенной Imec цепочке операций по обработке кремниевой пластины полевой транзистор n-типа (nFET) располагается над полевым транзистором p-типа (pFET).

Транзистор pFET выполнен в виде вертикального ребра (фактически FinFET), а транзистор nFET в виде вынесенной над ним наностраницы (по сути такого же ребра FinFET). Особая прелесть данной конструкции в том, что она создаётся в обычном техпроцессе, как для выпуска транзисторов FinFET. Анализ конструкции с помощью TCAD-инструментов доказывает, что производительность и потребление CFET, выпущенных с использованием 3-нм техпроцесса, превзойдёт показатели транзисторов FinFET в лучшую сторону. Тем не менее, есть проблема, с которой ещё придётся разобраться — это высокое паразитное сопротивление участка подключения истока к верхнему nFET-транзистору (происходит значительное падение напряжения Vss). Данную проблему можно решить, например, за счёт использования рутения в качестве проводника.

Что касается размера ячеек, то «цифровую» или стандартную ячейку в случае CFET удаётся свести к схеме с тремя активными рёбрами FinFET (три контактных площадки в первом слое металлизации), а ячейку SRAM — к схеме с четырьмя активными рёбрами FinFET. Современные же техпроцессы дают возможность создавать ячейку с 6 активными рёбрами и не меньше (6T). На картинке выше, поясним, показаны только активные рёбра FinFET. Рёбра-пустышки, которые разделяют активные FinFET, но не задействованы в схеме ячейки, на картинке заменены пустыми местами, но на кристалле они физически присутствуют и занимают место. «Двухэтажные» комплиментарные транзисторы позволят с пользой использовать окружающую площадь. В этом с Imec согласны партнёры по программе разработки компании GlobalFoundries, Huawei, Intel, Micron, Qualcomm, Samsung, SK Hynix, Sony Semiconductor Solutions, TOSHIBA Memory, TSMC и Western Digital.