Цитата из комментариев к предыдущей статье: «Вот, к сожалению, данные, адреса и любые операции над ними не годятся для графового представления. Если придумаете как это сделать — будет революция. А без данных, адресов и арифметики, лучшее что можно сделать асинхронным (с помощью графового метода) — машину Тьюринга. Но никак не процессор, к примеру. Поэтому тематика и заброшена, уже 20 лет как.» В компетенции автора сомневаться не приходится, все-таки доктор наук. А я вот попробую сделать революцию.

Как видно из цитаты проблема состоит из двух частей: операции над данными и операции над адресами. С адресами разберусь в следующей статье, а сейчас — данные.

Для примера попробую сделать схему разряда регистра, выполняющего две операции. Почему две? Потому что две, три операции или десять — принципиальной разницы нет. От увеличения количества операций увеличивается только объем вычислений при синтезе схемы. Главное, чтобы таких операций было более одной. В качестве операций выберу копирование из буфера и сложение с содержимым другого регистра.

Итак, попробую нарисовать поведение разряда такого регистра. Как понимаю, проблема описания поведения объекта (носителя информации) заключается в том, что он взаимодействует с другими объектами (носителями информации). И эти связанные объекты могут изменять свои значения произвольно (относительно описываемого объекта). Если связанных объектов 2, 3 и более, то описывать все возможные изменения таких объектов на языке STG занятие бессмысленное. Но есть выход. Достаточно ввести в STG три новых типа событий:

f? — с этого момента значение сигнала f не определено,

f/ — с этого момента значение сигнала f определено, и оно равно 1,

f — с этого момента значение сигнала f определено, и оно равно 0.

Очередность типов событий для одного сигнала такая:

после "+" — "-" или "?",

после "-" — "+" или "?",

после "?" — "/" или "",

после "/" — "?" или "-",

после "" — "?" или "+".

Используя новые типы событий можно описать поведение разряда регистра.

Входные сигналы:

a — команда на операцию прибавления значения второго регистра;

c — команда на операцию копирования из буфера;

r0 — значение соответствующего разряда второго регистра;

b — значение соответствующего разряда буфера;

y0 — сигнал переноса из младшего разряда при операции сложения;

n0 — сигнал отказа от переноса из младшего разряда при операции сложения.

Выходные сигналы:

r — значение разряда описываемого регистра;

t — сигнал завершения операции сложения;

t0 — сигнал завершения операции копирования;

y — сигнал переноса в старший разряд при операции сложения;

n — сигнал отказа от переноса в старший разряд при операции сложения.

Процесс исполнения команд по шагам выглядит так:

Копирование.

1. Внешняя управляющая схема (ВУС) вырабатывает сигнал c+. К этому моменту сигнал b устанавливается в одном из состояний (0 или 1).

2. Схема разряда регистра (СРР) вырабатывает сигнал t0+ для ВУС.

3. ВУС вырабатывает сигнал c-.

4. Если это необходимо, СРР меняет значение сигнала r на противоположное.

5. СРР вырабатывает сигнал завершения операции t0-. После этого ВУС может изменять значение сигнала b.

Сложение.

1. ВУС вырабатывает сигнал a+. К этому моменту сигнал r0 устанавливается в одном из состояний (0 или 1).

2. Если это возможно без использования информации о переносе из младшего разряда, СРР вырабатывает сигнал y+ или n+ для старшего разряда.

3. СРР дожидается из младшего разряда сигнал y0+ или n0+.

4. СРР вырабатывает для старшего разряда сигнал y+ или n+, если он еще не был сформирован.

5. СРР вырабатывает сигнал t+ для ВУС.

6. ВУС, собрав сигналы t+ со всех разрядов, вырабатывает сигнал a-.

7. СРР вырабатывает сигнал y- или n- для старшего разряда.

8. СРР дожидается сигнала y0- или n0- из младшего разряда.

9. Если это необходимо, СРР меняет значение сигнала r на противоположное.

10. СРР вырабатывает сигнал завершения операции t-. После этого ВУС может изменять значение сигнала r0.

Взаимодействие с младшим разрядом осуществляется опосредованно через ВУС. Введение прямого ответного сигнала для младшего разряда позволило бы запараллелить взаимодействие с ВУС и с соседними разрядами. Но для этой статьи я решил выбрать исходное задание попроще.

Казалось бы, задание составлено, можно приступать к синтезу схемы. Но не все так просто. Ни один из известных методов не способен для данного типа поведений синтезировать SI схему (даже если адаптирует новые типы событий). Более того, на мой взгляд ни один из методов не сможет это задание втиснуть в более менее приемлемую элементную базу.

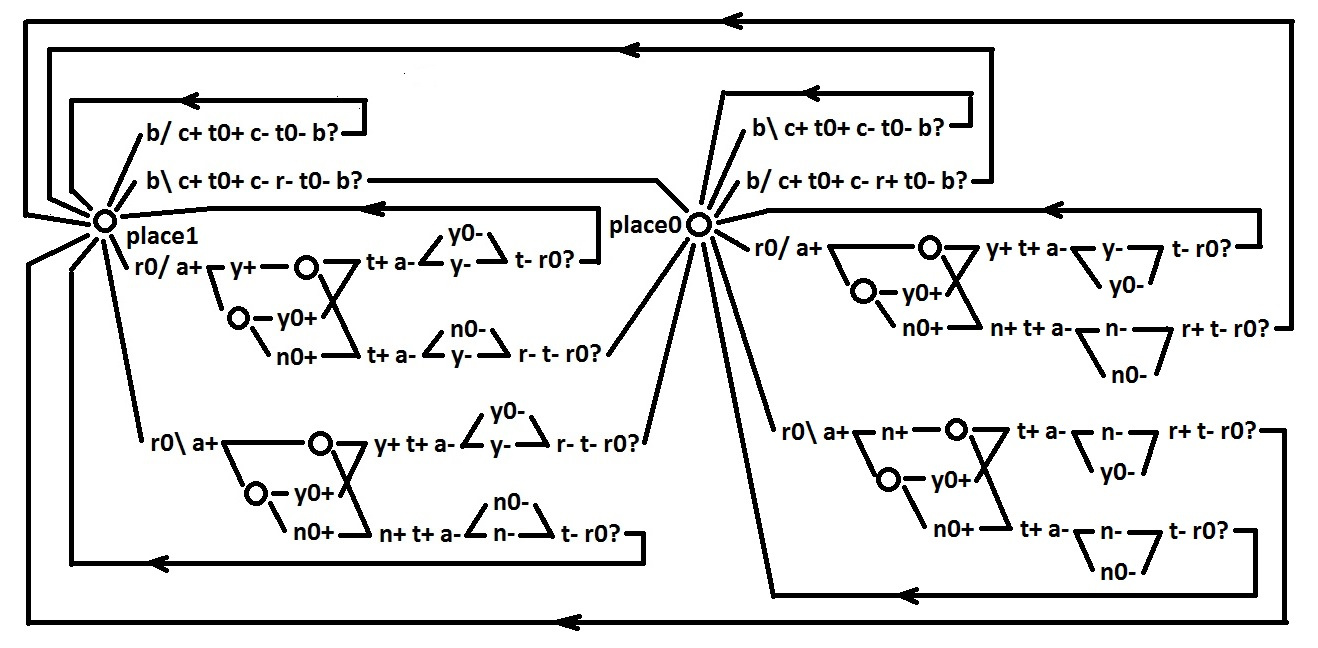

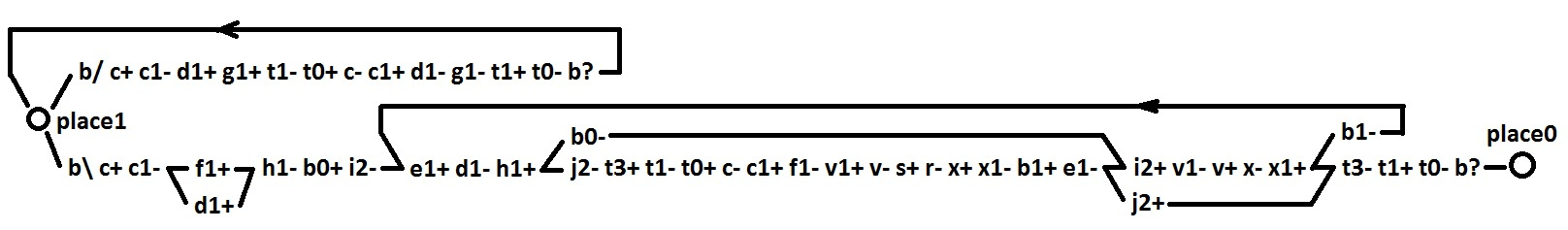

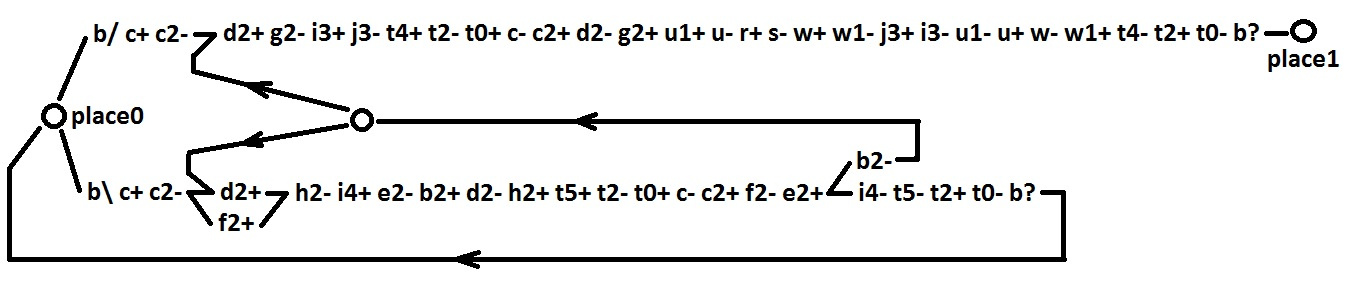

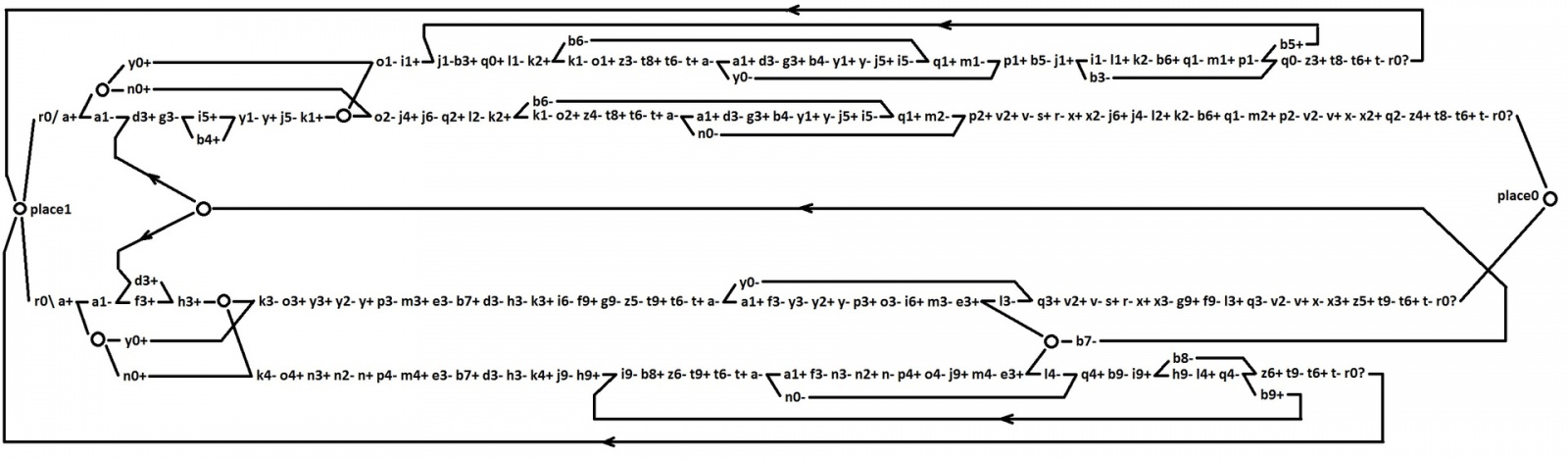

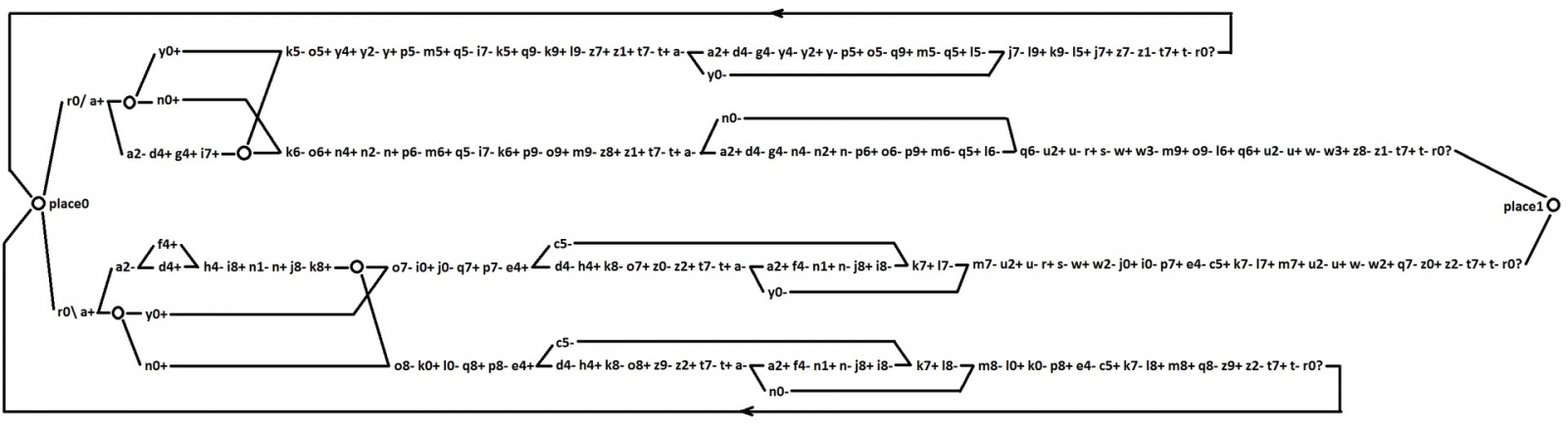

Но, к счастью есть мой метод, который позволяет эти проблемы решить. Процесс корректировки исходного задания я здесь приводить не буду. Покажу лишь конечный результат. Для удобства восприятия покажу его на четырех отдельных картинках.

Копирование когда r=1.

Копирование когда r=0.

Сложение когда r=1.

Сложение когда r=0.

А теперь логические функции.

Как видно, схема синтезирована в базисе 2И-НЕ, 2ИЛИ-НЕ Задачу ограничения нагрузок на выходы элементов я не ставил. Но если каждый выход элемента ограничить двумя нагрузками, то схема увеличится процента на 2-3 (по моей оценке). А вот если ограничить входы схемы двумя нагрузками, то это задача посложнее. Тут я ожидаю увеличения схемы процентов на 25.

Автор: ajrec