Здравствуй, мир! Сегодня у нас серия статьей для людей со средними знаниями о работе процессора в которой мы будем разбираться с процессорными архитектурами (у меня спелл чекер ругается на слово Архитектурами/Архитектур, надеюсь я пишу слово правильно), создавать собственную архитектуру процессора и многое другое.

Принимаются любые замечания!

Немного про архитектуру процессора

Исторически сложилось, что существуют много процессоров и много архитектур. Но многие архитектуры имеют схожести. Специально для этого появились "Группы" архитектур типа RISC, CISC, MISC, OISC (URISC). Кроме того они могут иметь разные архитектуры адресации памяти (фон Неймана, Гарвард). У каждого процессора есть своя архитектура. Например большинство современных архитектур это RISC (ARM, MIPS, OpenRISC, RISC-V, AVR, PIC** и т.д.), но есть архитектуры которые выиграли просто за счет других факторов (Например удобство/цена/популярность/etc) Среди которых x86, x86-64 (Стоит отметить, что x86-64 и x86 в последних процессорах используют микрокод и внутри них стоит RISC ядро), M68K. В чем же их отличие?

RISC

Reduced Instruction Set Computer — Архитектура с уменьшенным временем выполнения инструкций (из расшифровка RISC можно подумать, что это уменьшенное количество инструкций, но это не так). Данное направления развилось в итоге после того, как оказалось, что большинство компиляторов того времени не использовали все инструкции и разработчики процессоров решили получить больше производительности использую Конвейеры. В целом RISC является золотой серединой между всеми архитектурами.

Яркие примеры данной архитектуры: ARM, MIPS, OpenRISC, RISC-V

TTA

Что такое TTA? ТТА это Архитектура на основе всего одной инструкции перемещения из одного адреса памяти в другую. Данный вариант усложняет работу компилятора зато дает большую производительность. У данной архитектуры есть единственный недостаток: Сильная зависимость от шины данных. Именно это и стало причиной ее меньшей популярности. Надо отметить что TTA является разновидностью OISC.

Яркие примеры: MOVE Project

OISC (URISC)?

One Instruction Set Computer — Архитектура с единственной инструкцией. Например SUBLEQ. Такие архитектуры часто имеют вид: Сделать действие и в зависимости от результата сделать прыжок или продолжить исполнение. Зачастую ее реализация достаточно простая, производительность маленькая, при этом снова ограничение шиной данных.

Яркие примеры: BitBitJump, ByteByteJump, SUBLEQ тысячи их!

CISC

CISC — Complex Instruction Set Computer — ее особенность в увеличенных количествах действий за инструкцию. Таким образом можно было теоретически увеличить производительность программ за счет увеличения сложности компилятора. Но по факту у CISC плохо были реализованы некоторые инструкции т.к. они редко использовались, и повышение производительности не было достигнуто. Особенностью этой группы является еще ОГРОМНАЯ Разница между архитектурами. И несмотря на названия были архитектуры с маленьким количеством инструкций.

Яркие примеры: x86, M68K

Адресация памяти

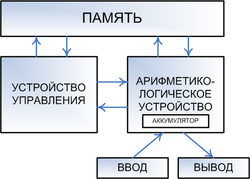

Архитектура фон Неймана

Особенностью таких архитектур была общая шина данных и инструкций. Большинство современных архитектур это программный фон Нейман, однако никто не запрещает делать аппаратный Гарвард. У данной архитектуры большим недостатком является большое зависимости производительности процессора от шины. (Что ограничивает общую производительность процессора).

Архитектура гарварда

Особенность этой архитектуры является отдельная шина данных и инструкций. Дает большую производительность чем фон Нейман за счет возможности за один такт использовать обе шины (читать из шины инструкций и одновременно записывать в шинну данных), но осложняет архитектуру и имеет некоторые ограничения. В основном используется в микроконтроллерах.

Особенности процессоров

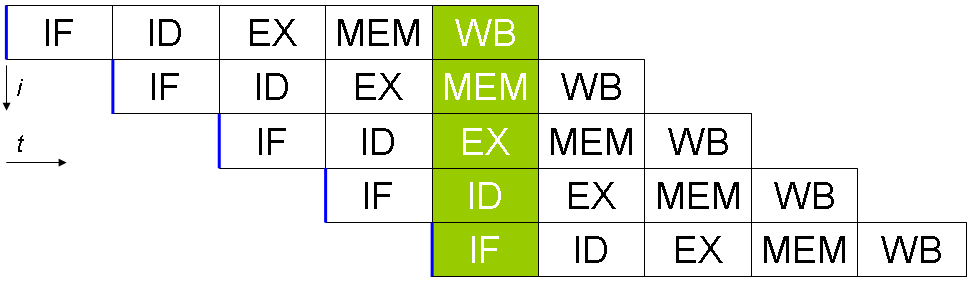

Конвейеры

Что такое конвейеры? Если сказать очень глупым языком это несколько параллельных действий за один такт. Это очень грубо, но при этом отображает суть. Конвейеры за счет усложнения архитектуры позволяют поднять производительность. Например конвейер позволяет прочитать инструкцию, исполнить предыдущую и записать в шину данных одновременно.

На картинке более понятно, не правда?

IF — получение инструкции,

ID — расшифровка инструкции,

EX — выполнение,

MEM — доступ к памяти,

WB — запись в регистр.

Вроде все просто? А вот и нет! Проблема в том что например прыжок (jmp/branch/etc) заставляют конвейер начать исполнение (получение след. инструкции) заново таким образом вызывая задержку в 2-4 такта перед исполнение следующей инструкции.

Расширение существующих архитектур

Достаточно популярной техникой является добавление в уже существующую архитектуру больше инструкций через расширения. Ярким примером является SSE под x86. Этим же грешит ARM и MIPS и практически все. Почему? Потому что нельзя создать унивирсальную архитектуру.

Другим вариантом является использование других архитектур для уменьшения размера инструкций.

Яркий пример: ARM со своим Thumb, MIPS с MIPS16.

Техники применяемые в GPU

В видеокартах часто встречается много ядер и из-за этой особенности появилась потребность в дополнительных решениях. Если конвейеры можно встретить даже в микроконтроллерах то решения используемых в GPU встречаются редко. Например Masked Execution (Встречается в инструкциях ARM, но не в Thumb-I/II). Еще есть другие особенность: это уклон в сторону Floating Number (Числа с плавающей запятой), Уменьшение производительности в противовес большего количества ядер и т.д.

Masked Execution

Данный режим отличается от классических тем, что инструкции исполняются последовательно без использования прыжков. В инструкции хранится некоторое количество информации о том при каких условия эта инструкция будет исполнена и если условие не соблюдено то инструкция пропускается.

Но Зачем?

Ответ прост! Что бы не нагружать шину инструкций. Например в видеокартах можно загрузить тысяче ядер одной инструкцией. А если бы использовалась система прыжков то пришлось бы для каждого ядра ждать инструкцию из медленной памяти. Кеш частично решает проблему, но все еще не решает проблему полностью.

Прочее

Здесь мы будем описывать несколько техник используемых в центральный процессорах и микроконтроллерах.

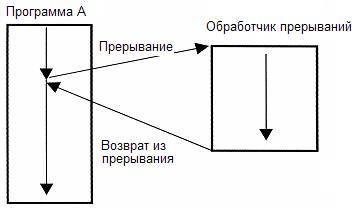

Прерывания

Прерывания это техника при которой исполняемый в данный момент код приостанавливается для выполнения какой-то другой задачи при каких-то условиях. Например при доступе в несуществующий участок памяти вызывается HardFault или MemoryFault прерывания или исключения. Или например если таймер отсчитал до нуля. Это позволяет не бездействовать пока нужно ждать какое-то событие.

Какие недостатки? Вызов прерывания это несколько тактов простоя и несколько при возврат из прерывания. Так же несколько инструкций в начале кода будет занято инструкциями для Таблицы прерываний.

Exception (исключения)

Но кроме прерываний еще существуют исключений которые возникают например при деления на ноль. Зачастую его совмещают с прерываниями и системными вызовами, как например в MIPS. Исключения не всегда присутствуют в процессоре например как в AVR или младших PIC

Системные вызовы

Системные вызовы используется в Операционных системах для того что бы программы могли общаться с операционной системой например просить ОС прочитать файл. Очень похоже на прерывания. Аналогично исключениям не всегда присутствуют в процессоре

Контроллеры доступа в память и прочие методы сдерживания программ

Здесь описываются методы запрета доступа приложений к аппаратуре напрямую.

Привилегированный режим

Это режим в котором стартует процессор. В таком режиме программа или ОС имеют полный доступ к памяти в обход MMU/MPU. Все программы запускаются в непривилегированном режиме во избежания прямого доступа к аппаратным подсистемам программ для этого не предназначенных. Например вредоносным программам. В Windows ее часто называют Ring-0 а в *nix системным. Не стоит путать РУТ и Привилегированный режим ибо в руте вы все еще не можете иметь прямой доступ к аппаратуре (можно загрузить системный модуль который позволит это сделать, но об этом чуть позже :)

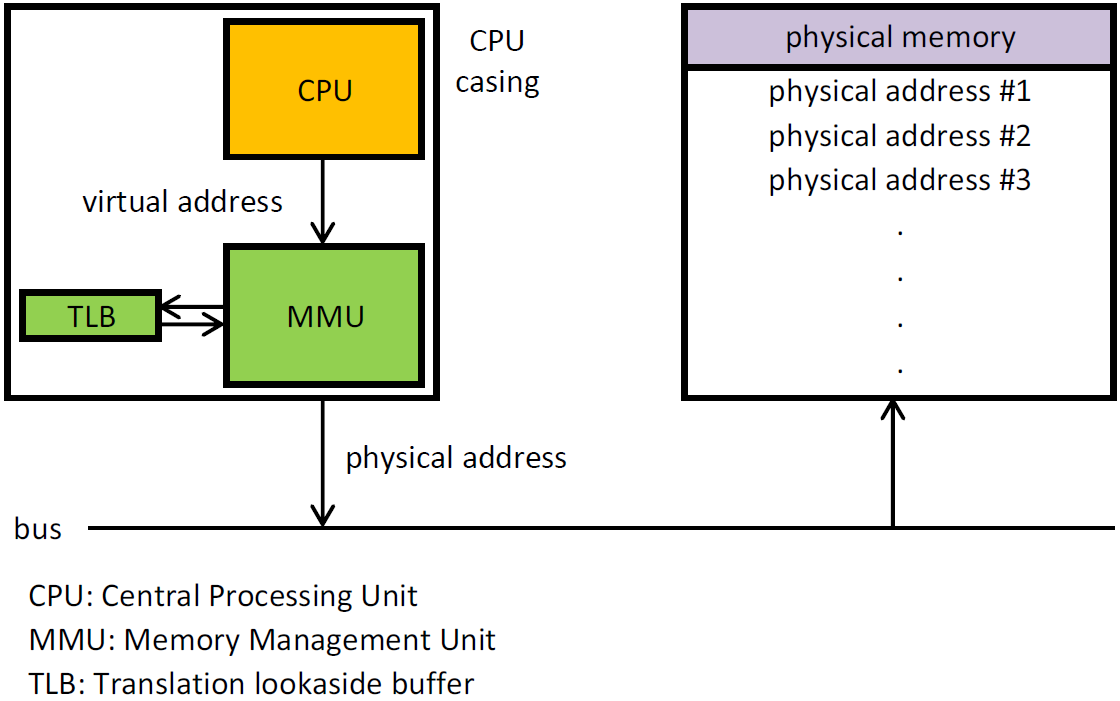

MPU и MMU

MPU и MMU используется в современных системах чтобы изолировать несколько приложений. НО если MMU позволяет "передвинуть" память то MPU позволяет только блокировать доступ к памяти/запуск кода в памяти.

PIC (PIE)

Что такое PIE? (PIC не использую для избежания путаницы с МК PIC). PIE это техник благодаря которому компилятор генерирует код который будет работать в любом месте в памяти. Это техника в совмещении с MPU позволяет компилировать высокие языки программирования которые будут работать и с MPU.

SIMD

Популярная техника SIMD используется для того что бы за один такт выполнять несколько действий над несколькими регистрами. Иногда бывают в качестве дополнений к основной архитектуре например как в MIPS, ARM со своими NEON/VFP/etc, x86 со своим SSE2.

Reposition for Optimization

Это техника используется для того что бы оптимизировать код который генерирует компилятор что бы увеличить производительность процессора с помощью пересортировки инструкций. Это позволяет использовать конвейер на полную.

Status register

Что такое регистр статуса? Это регистр который хранит состояние процессора. Например находится ли процессор в привилегированном режиме, чем закончилась операция последнего сравнения.

Используется в связке с Masked Execution. Некоторые разработчики специально исключают регистр статуса ибо она может являться узким местом как поступили в MIPS.

mov vs $0 reg

В MIPS нет отдельной инструкции загрузки константы в память. Но есть инструкция addi и ori которая позволяет в связке с нулевым регистром ($0) эмулировать работу загрузки константы в регистр. А в других архитектурах она присутствует. Я затронул эту тему, потому что она пригодиться нам в статьях с практикой.

Rd, Rs vs Rd, rs, rt

Идут множество споров насчет того сколько должно быть операндов в арифметических инструкциях. Например в MIPS используется вариант с 3-мя регистрами. 2 операнда, 1 регистр записи. С другой стороны использования двух операндов позволяет сократить код за счет уменьшения размера инструкции. Пример совмещения является MIPS16 в MIPS и Thumb-I в ARM. В плане производительности они практически идентичны (Если исключать размер инструкции как фактор).

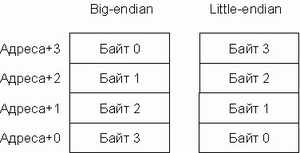

Endianness

Порядок байт. Возможно вам знакомы Выражения Big-Endian и Little-Endian. Они описывают порядок байт в инструкциях/в регистрах/в памяти/etc. Здесь думаю все просто :). Есть процессоры которые совмещают режимы. Как например MIPS. Или которые используют одну систему команд но имеют разный порядок байт. Как пример ARM.

Битность процессора

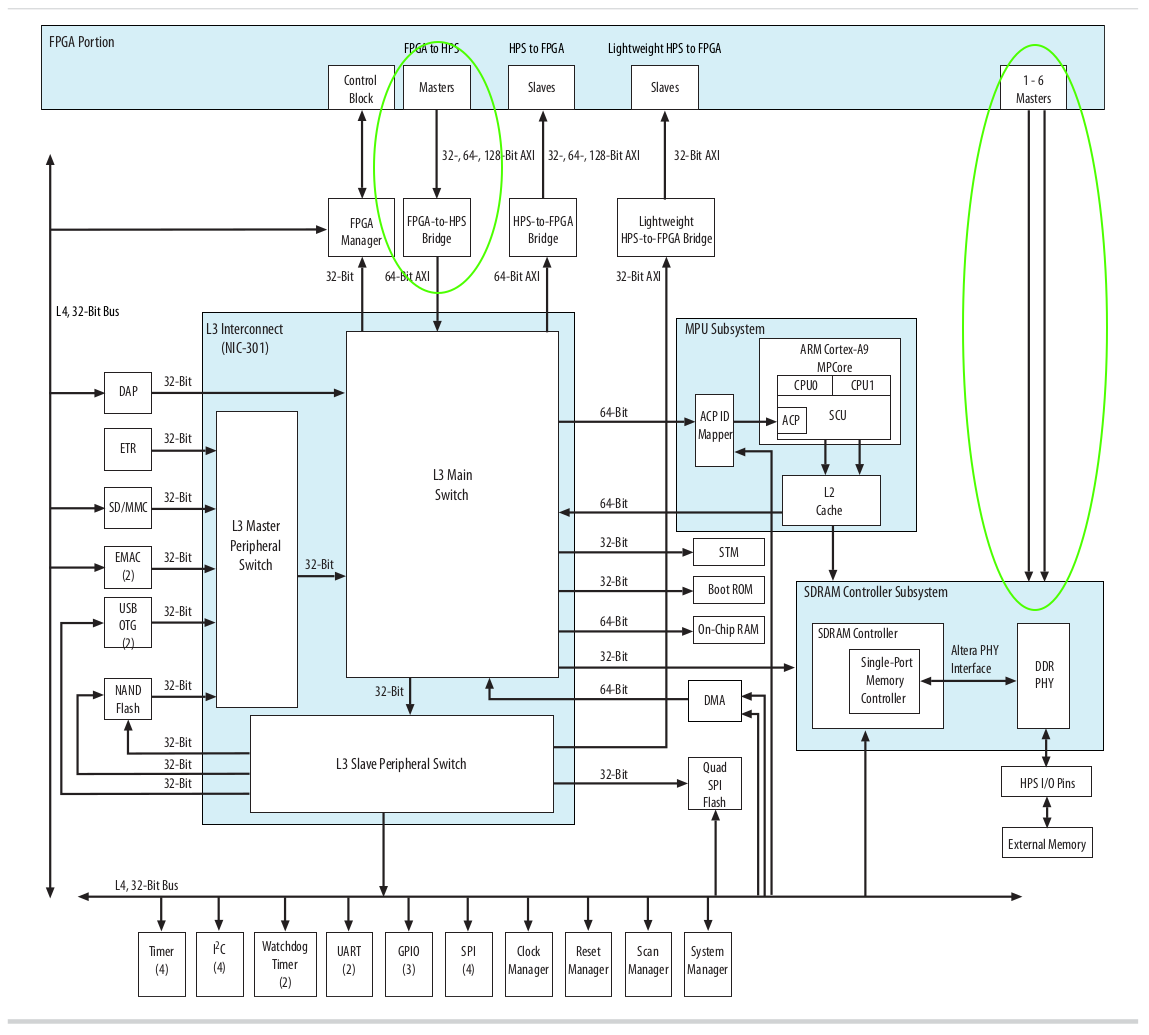

И так что такое битность процессора? Многие считают, что это битность шины данных. Но это не так. Почему? В ранние переоды микроконтроллеров и микропроцессоров шина могла быть например 4-х битной но передавала пакетами по 8 бит. Для программы казалось, что это 8-и битный режим, но эта была иллюзия. Как и сейчас. Например в ARM SoC-ах часто применяют 128-и битную шину данных или инструкций.

Сопроцессоры

Что такое сопроцессоры? Сопроцессоры являются элементами процессора или внешней микросхемой, который позволяют исполнять инструкции который слишком громоздки для основной части процессора. Как яркий пример сопроцессоры в MIPS для деления и умножения. Или например 387 для 80386 который добавлял поддержку чисел с плавающей запятой. А в MIPS сопроцессоров было много и они выполняли свои роли. Например были контроллерами прерываний/исключений/системных вызовов. Часто сопроцессоры имеют собственные инструкции и на системах где этих инструкций нет (Пример ARM) Эмулируют ее через Trap-ы (ловушки?). Несмотря на костыльность, и маленькую производительность они часто являются единственным выбором в микроконтроллерах.

Атомарность операций

Атомартность операций обеспечивает потоко-независимое исполнение за счет инструкций который выполняют несколько действий за один Псевдо такт.

Вариант другого решения атомарность переферии. Например для установки ножки в STM32 в высокое и низкое состояние используется разные регистры, что позволяет иметь атомарность на уровне переферии.

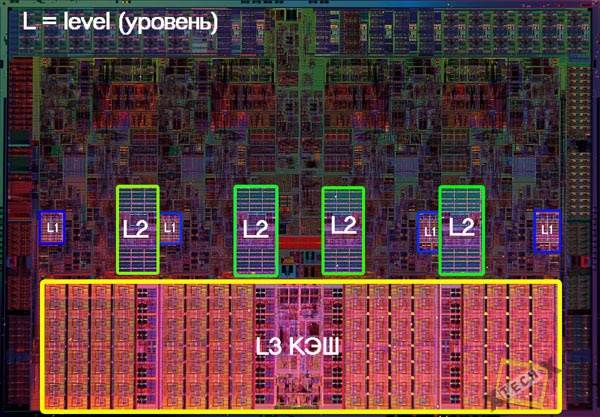

Кеш

Вы навярника слышали о L1, L2, L3 и регистрах. Если коротко процессор анализирует часть кода, что бы предугадать прыжки и доступ в память и зараннее просит кеш получить эти данные из памяти. Кеш зачастую бывает прозрачным для программы, но бывают и исключения из этого правила. Например в Программных ядрах в ПЛИС используется програмный кеш.

И вы кончено слышали о такой вещи, как Cache Miss или промах по кешу. Это операция которая не была предустмотренна процессорам или процессор не успел закешировать эту часть памяти. Что достаточно часто является проблемой замедления доступа к памяти. Промах проходит незаметно для программы, но не остается не заметными просадки в производительности. Так же переключения контекстов например при прерываниях тоже заставляет страдать кеш ибо небольшой код сбивает конвейер и кеш для собственных нужд.

Shadow Registers

В современных процессорах часто используеться техника теневых регистров. Которые позволяют переключаться между прерываниями и пользовательским кодом практически без задержек связанных с сохранением регистров.

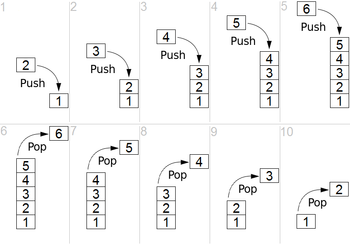

Stack

Стек? Я видел Стек в .NET и в Java! Что же. Вы частично правы. Стек существует, но он никогда не был апаратным в большинства процессорах. Например в MIPS его по просту нет. Спросите КАК ТАК ТО?! Ответ прост. Стек это просто доступ к памяти которую не нужно резервировать (очень грубое определение). Стек используется для вызова функций, передачи аргументов, сохранения регистров для того чтобы востановить их после выполнения функции и т.д.

Спросите тогда что такое хип (Heap)? Хип это память размером намного больше чем стек (Стек обычно ~1MB). В хипе храниться все глобальное. Например все указатели полученные с помощю Malloc указывают на часть хипа. А указатели хранятся в стеке или в регистрах. С помощю инструкций загрузки данных относительно регистра можно ускорить работу стека и других доступов к памяти по типу стека посколько не нужно постоянно использовать операции PUSH/POP, INC/DEC или ADDI, SUBI (добавить константу) что бы получить данные глубже по стеку, а можно просто использовать доступ относительно стека с отрицательным смещением.

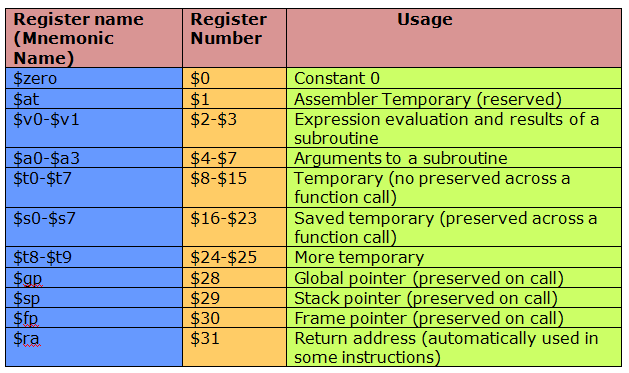

Регистры

Не буду описывать регистры слишком подробно. Это мы затронем в практической статье.

В x86 регистров достаточно мало. В MIPS используется увеличенное количество регистров а именно 31 ($0 имеет значение всегда равное нулю). В процессоре университета беркли использовались регистровые окна, которые жестки ограничивали вложенность функций, при этом имели бОльшую производительности. А в других (например AVR) ограничили использование регистров (например три 16 битных, которые можно трактовать, как шесть восьми битных. первые 16, которые недоступны при некоторых операциях). Я считаю, что лучший метод был выбран MIPS-ом. Это мое сугубо личное мнение.

Выравнивание

Что такое выравнивание? Оставлю-ка я этот вопрос вам :)

Конец

Это конец первой главы нулевой части. Вся серия будет крутиться вокруг темы создания собственного процессора. Собственной операционной системы. Собственного ассемблера. Собственного компилятора и много чего другого.

Нулевые части будут посвящены теории. Я сомневаюсь что доведу всю серию до победного конца, но попытка не пытка! )

Автор: Armleo