Разработка микросхем дело сложное, дорогое и долгое. И цена любой ошибки крайне велика. После изготовления кристалла патчами и обновлениями уже ничего не исправить. Поэтому к проверке проектируемых схем на этапе разработки подходят особенно скрупулёзно. Для каждого функционального блока пишутся блочные тесты во всех рабочих и не рабочих режимах. После интеграции блока в общую схему проводятся системные тесты, как этот блок работает составе системы. Все тесты постоянно крутятся в регрессионном тестировании. Даже есть неформальный признак более менее приемлемого уровня тестирования – когда объем кода тестов в 10 раз больше объема кода тестируемого блока. Но все эти тесты не дают ощущения, что схема жизнеспособна, так как любое моделирование это поведение схемы на протяжении сотен миллисекунд максимум. А в жизни схема должна отработать сотни тысяч часов. Однажды я искал сбой, когда на 1 Гбайт переданной информации терялись 1 или 2 байта и никакие функциональные тесты эту проблему не обнаруживали. И проявлялась эта ошибка только на FPGA прототипе будущей микросхемы. О том какие прототипы делали мы и что вообще твориться в мире расскажет эта статья.

Прототипирование будущих микросхем на FPGA это единственный способ проверить как работает схема на реальных задачах в более менее реальном масштабе времени. Прототип позволяет отладить софт, получить первоначальные характеристики производительности и многое другое. Современные FPGA обладают достаточно большим объемом ресурсов для этих задачи. Например, вы можете сами на плате с FPGA за 300$ реализовать полноценный компьютер с процессором Intel 8086.

2004 год

К сожалению самого первого прототипа в залежах нашего шкафа со скелетами найти не удалось, но это была небольшая платка на базе Xilinx Spartan3-400 (XC3S400). 400 означает число тысяч эквивалентах вентилей, которые доступны разработчику для создания своей схемы. Цена платки составляла примерно 50$ и позволяла реализовать в ней простой 8-ми битный микроконтроллер со всей памятью и на частоте 40 МГц. Прототипирование заключалось в том, что разработанный микроконтроллер на ней поморгал светодиодом.

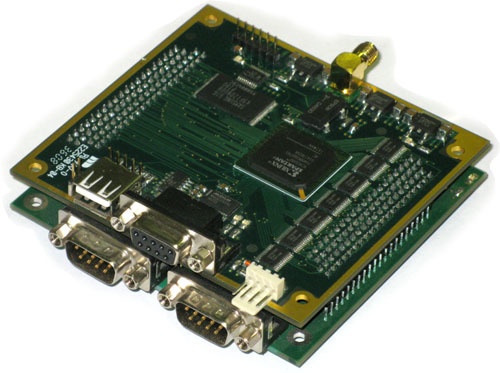

2005 год

Специальная плата для прототипа уже разрабатывалась не как эксперимент, а как осмысленный этап проекта. Применялась уже FPGA Xilinx Spartan3-1000. Т.е. нам уже был доступен 1 млн вентилей, и проектируемый микроконтроллер работал на своей макимальной частоте 48 МГц. И именно на этой плате я ловил те самые 2 потерянных байта на гигабайт. Цена платы составляла примерно 200$.

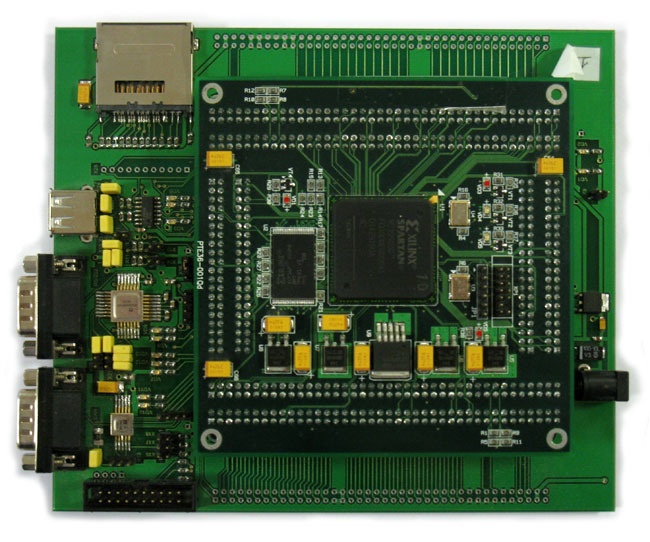

2007 год

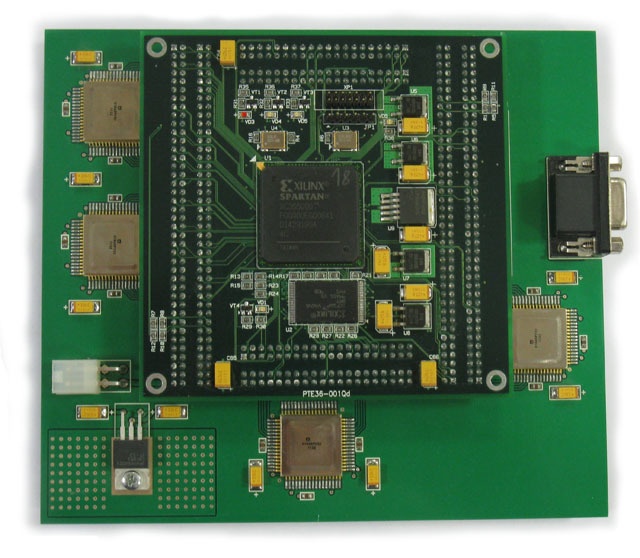

Для нового 32-х разрядного микроконтроллера было очевидно, что 1 млн вентилей может и не хватить. По этому была разработана новая плата на базе Xilinx Spartan3-5000, благодаря которой стало доступно уже 5 млн вентилей. Цена платы составила примерно 500$ и на долгое время эта плата стала основной для прототипирования новых разработок. На ее базе проверялись не только микроконтроллеры, но и различные специализированные микросхемы. Проектируемые микроконтроллер в FPGA работал уже на пониженной частоте в 20 МГц, хотя потом в кремнии работали на частотах 100 МГц и даже 150 МГц.

Прототип 32-х битного микроконтроллера:

Прототип видеокарты (к сожалению в жизнь проект так и не пошел, но готовый RTL ждет своего часа):

Прототип 4-х потового Ethernet коммутатор с встроенными приемопередатчиками:

2010 год

При разработке двухъядерного микроконтроллера (32-х битный RISC + 16 битное DSP ядро) мы наконец дошли до уровня, когда 5 млн было уже мало. Но реализация в FPGA различных усеченных конфигураций будущей микросхемы позволила проверить ее функционирование. Например, реализовывали два ядер (RISC+DSP) и с усеченным набором периферии или же одно ядро(RISC), но зато вся периферия.

2012 год

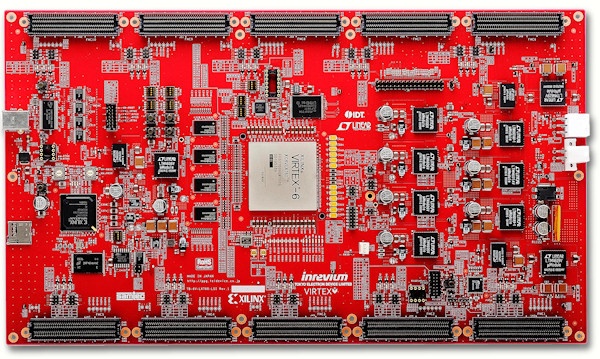

Новый проект потребовал новой платы, так как требуемый объем внутренней памяти для нового 32-х разрядного DSP ядра уже превосходил доступный объем в самой большой FPGA Spartan. Пришлось переходить на более дорогие и сложные ПЛИС. Время проекта было ограничено, и решили найти уже готовое решение. Выбор пал на плату от INREVIUM c самой большой на то время FPGA Xilinx Virtex-6 XC6VLX760.

И хотя число эквивалентный вентилей увеличилось всего до 8 млн, зато объем встроенной блочной памяти увеличился с 2 Мбит до 25 Мбит.

Выбор так же скорее всего определило то, что на сайте немецкого представительства в кэше Google сохранилась стоимость платы, и мы знали что она будет стоить 18К$ до подписания всяких NDA. А при стоимости только одной микросхемы FPGA в 15 тыс $ это снимало любые вопросы о разработке собственной платы. Серийные платы для таких больших FPGA обычно стоят либо столько же сколько и сами FPGA либо немного дороже.

Приобретение платы тоже доставило много интересных знаний, так например наш локальный дистрибьютор был убежден, что эта плата стоит 40K$ c учетом доставки, и вообще он очень рискует при 100% предоплате с нашей стороны. В конечном счете было приобретено 3 таких платы без посредников и сейчас они применяются для прототипирования наших DSP процессоров

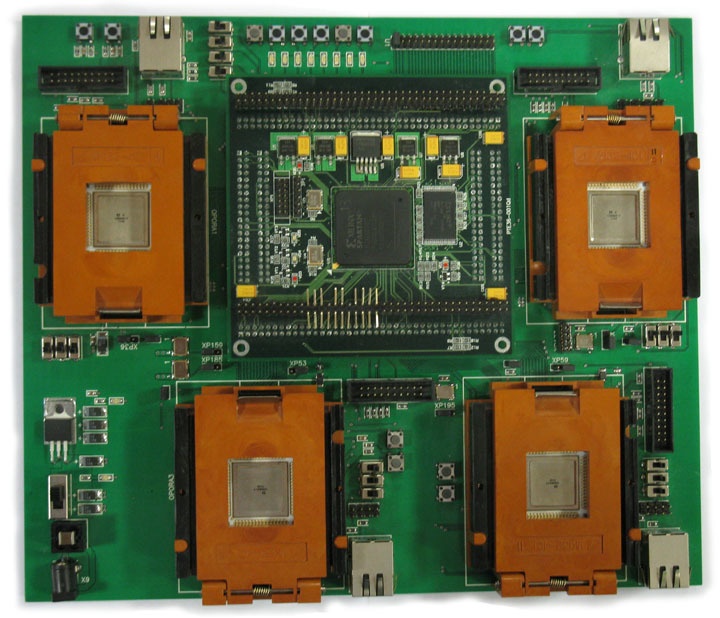

2013 год

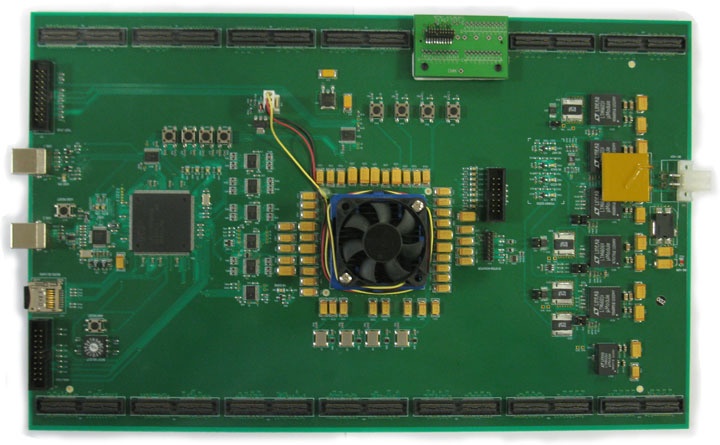

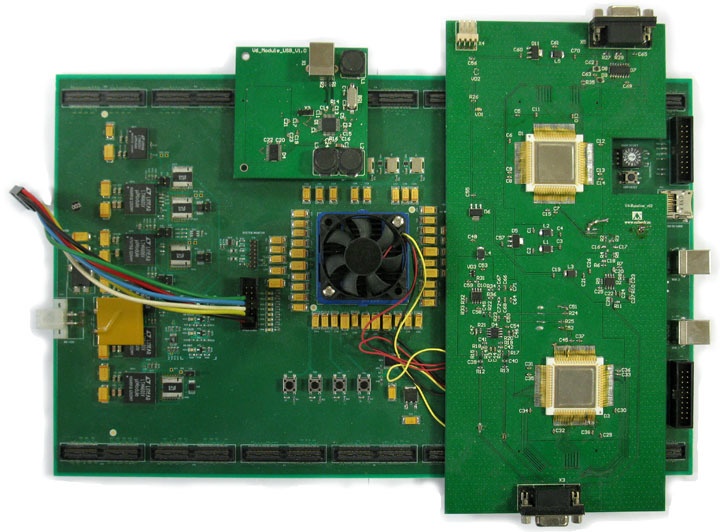

Для нового 32-х битного специализированного микроконтроллера было решено все же попробовать сделать свою плату. Во-первых, разработчики модулей на FPGA должны развиваться и не бояться применять микросхемами, которые дороже их личных автомобилей, а во-вторых у одного из дистрибьюторов завалялись на складе несколько Virtex-6 XC6VLX550Т и он предлагал их с большим дисконтом. FPGA LX550Т это на одну ступень меньше чем LX760 (примерно на 30% меньше вентилей), но зато конечная цена плат с учетом разработки составила всего около 8К$. Таких плат было собрано 6 шт. Раздавать их заказчикам мы не планировали, а организовали для разработчиков доступ к ним через интернет. В плате было реализовано много интересных решений. Например, файлы прошивок грузились на плату как на MassStorage Device в специальную SD карту, и потом уже из нее загружались в FPGA. Всего на карте может быть до 10 различных прошивок, и через специальную программу управления можно выбрать какую из них использовать в данный момент. Так же реализованы различные защиты «от дурака», что бы случайно не спалить дорогую микросхему. Все это позволяет работать с этими платами удалено, безопасно и доверять их даже студентам. Проектируемый МК в FPGA работал на частоте 40 МГц.

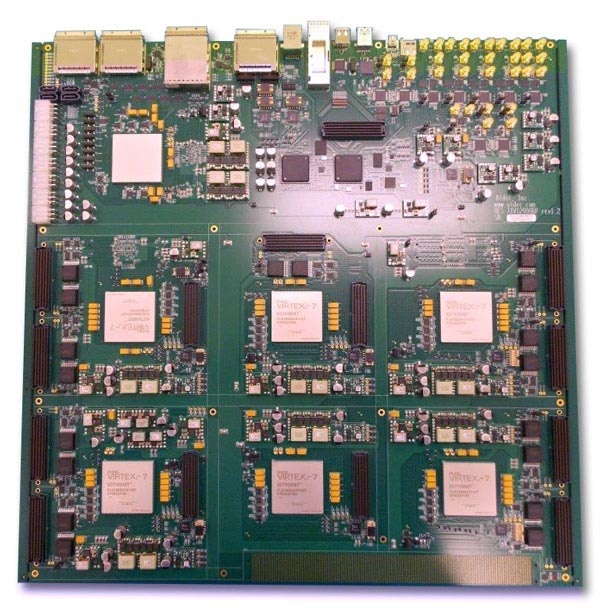

Сама плата (прототип специализированного двухъядерного 32-х битного микроконтроллера):

Прототип специализированной микросхемы для датчиков преобразования угол в код:

К сожалению в данной плате есть несколько недостатков: выбраны «дурные» разъемы для подключения дополнительных модулей, но это пол беды, забыли сделать крепежные отверстия возле разъемов, и модули держатся фактически только в разъемах. Так же что бы получить доступ к некоторым элементам управления основной платы приходится фигурно вырезать модули расширения.

Отечественный опыт

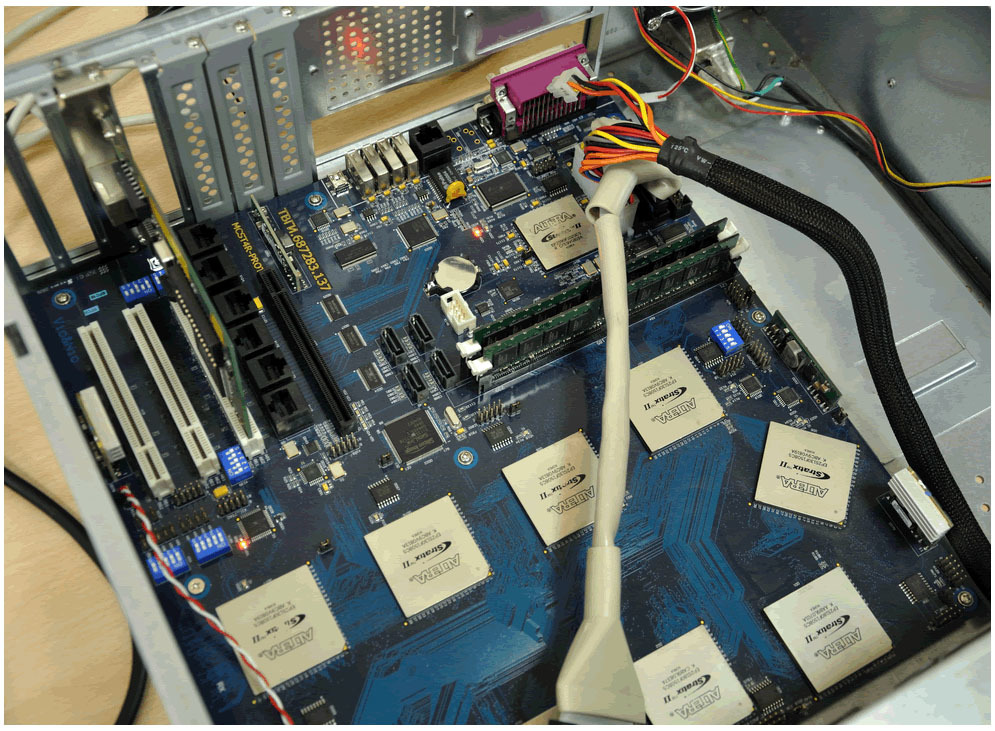

А что же другие разработчики заказных микросхем? Например МЦСТ при прототипировании СБИС 1891ВМ6Я (R-1000, четырёхъядерный процессор с 64-битной архитектурой SPARC v.9) использовала специализированную плату с 10 FPGA Altera Stratix II ( 4 х EP2S180 + 5 x EP2S130 + 1 x EP2S90). Общий объем логических вентилей системы можно оценить в 20 млн.

Сейчас одна микросхема EP2S180 стоит около 8К$. Так что стоимость только микросхем FPGA в прототипе превышает 50К$.

Для прототипирования процессора Эльбрус-4C+ потребовалась уже 21 микросхема Altera Stratix IV EP4SE820 и с суммарным объемом в 100 млн. вентилей (хотя сам МЦСТ приводит цифру в 750 млн) и стоимостью около 200К$. При этом рабочая частота прототипа 9 МГц.

Зарубежный опыт

Сейчас специализированные решения для FPGA прототипирования предлагают компании специализирующиеся на разработке средств САПР для микроэлектроники, хотя пригодные для прототипирования модули можно найти и у других компаний. FPGA прототипы есть у Intel и IBM, но их характеристики не афишируются, и становятся известны широкому кругу, только тогда, когда прототип уже моральна устарел.

Cadence предлагает специальную Rapid Prototyping Platform построенную на базе FPGA Altera Stratix-4 EP4SE820. В минимальной конфигурации платформа состоит из двух (c суммарным объемом в 10 млн вентилей), в максимальной из шести FPGA (c объемом до 30 млн вентилей). Цена одной микросхемы EP4SE820 сегодня ~10К$.

Новая система от Cadence носит название Protium и стоится на базе Xilinx Virtex-7 XC7V2000Т и позволяет реализовать от 25 млн на двух FPGA до 100 млн вентилей на восьми. Стоимость одной микросхемы XC7V2000Т сейчас около 20К$. Т.е. в полной комплектации Protium будет стоить не менее 160К$.

Компания Aldec помимо средств разработки так же предлагает платформу для FPGA протоипирования HES-7.

На одной плате расположено до шесть FPGA Xilinx Virtex-7 XC7V2000Т или UltraSacle XCVU440. В случае реализации модуля на базе FPGA UltraSacle XCVU440 суммарное число вентилей достигает 158 млн. С помощью дополнительной платы можно собрать в единый модуль 24 микросхемы FPGA и получить 633 млн вентилей. Стоимость одной микросхемы XCVU440 сейчас 49К$. А максимальная суммарная стоимость всех FPGA переваливает за 1М$.

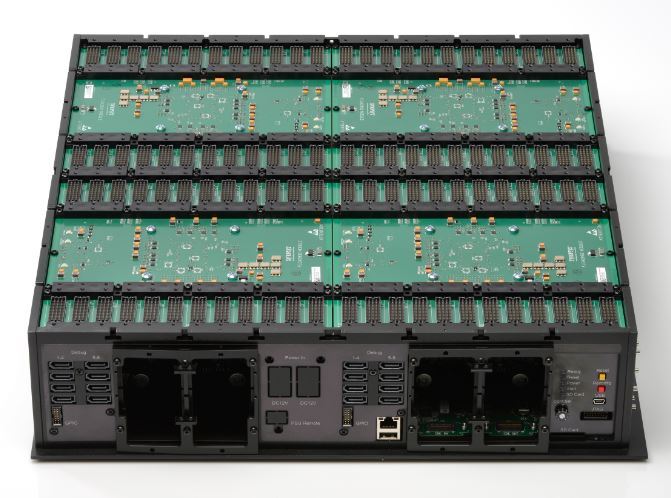

Synopsys имеет наверное наибольший опыт в разработке платформ для FPGA прототипирвоания. Ранние их модели строились на базе FPGA Virtex-6 (HAPS-60), затем Virtex-7 (HAPS-70). Последняя их разработка HAPS-80 в одном модуле содержит от одной до четырех FPGA Xilinx UltraScale XCVU440.

Готовые модули можно объединять в единую стойку. И в этом случае суммарный объем составляет рекордные 1,6 млрд вентилей.

При использовании одной FPGA максимальная частота до 300 МГц, при использовании соседних в одном модуле до 100 МГц, при использовании нескольких модулей частота снижается до 30 МГц.

Таким образом, имея примерно 3,5М$ на приобретение FPGA вы сможете собрать платформу пригодную для прототипирования Intel Xeon E7. Ну или подождать 20 лет, когда FPGA такого объема подешевеют до пары сотен долларов.

Автор: Sergei2405