Пульт управления

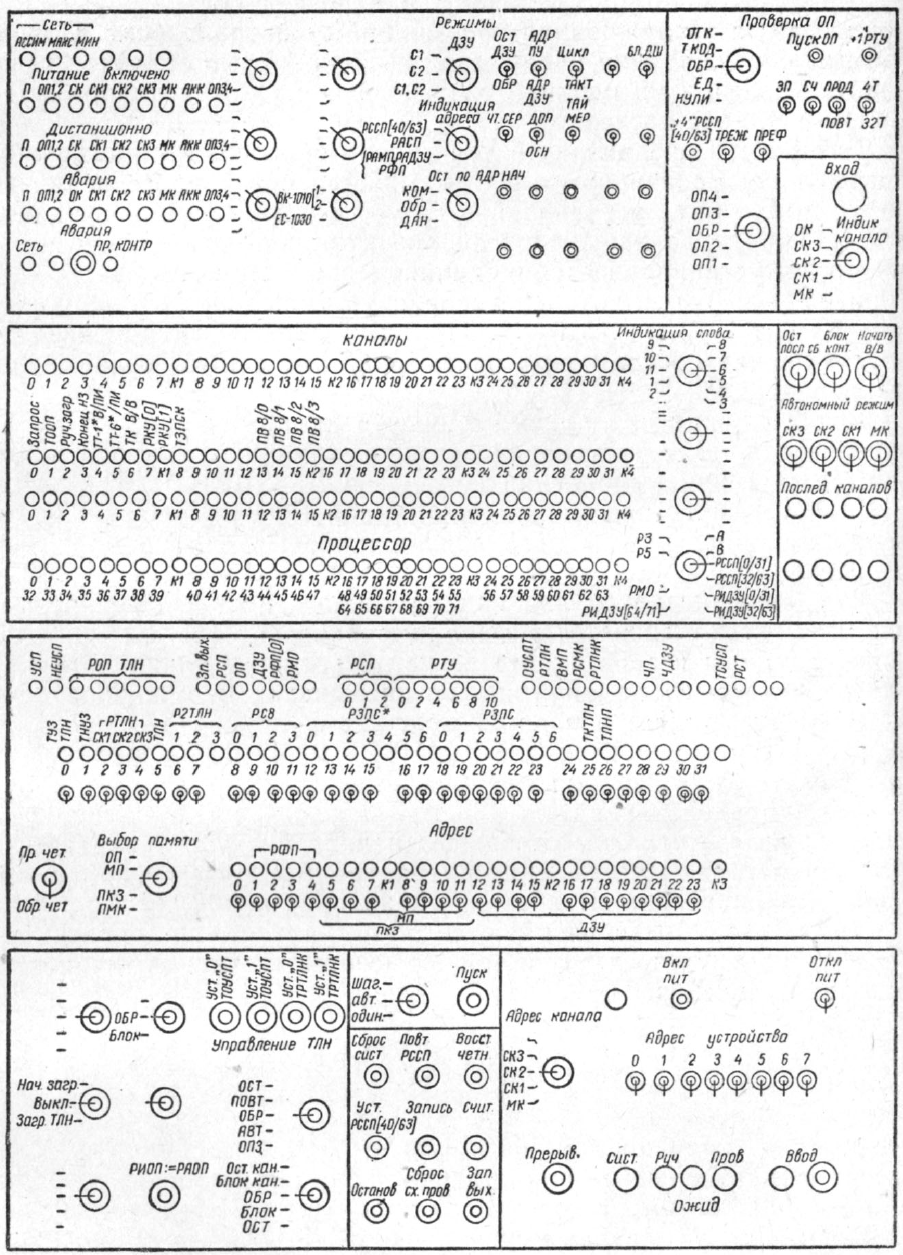

В Интернете фотографий ЕС-1030 почти нет: помимо той, что используется в качестве иллюстрации ко всей серии статей, мне лично попалась только ещё одна, на которой присутствует только процессор и его пульт. Схематическое изображение пульта имеется в [1].

Как видно по фотографиям, пульт ЕС-1030, в отличие от если не всех, то подавляющего большинства машин Единой Системы, является плоским, что эргономически, пожалуй, менее удобно.

Пульт оператора

В правой нижней части расположены органы управления пульта оператора, позволяющие включить и выключить машину (предусмотрено не только обычное, но и аварийное отключение, при котором питание со всех устройств снимается сразу, без соблюдения определённой последовательности), выполнить начальную загрузку и послать системе сигнал прерывания.

Нажатие кнопки включения питания после завершения всех процессов, связанных с подачей питания на узлы процессора, памяти и каналов, инициирует начало выполнения микропрограммы с адреса E01. Микропрограмма инициализирует аппаратуру, выполняет самотестирование и переходит в состояние останова, т. е. ручной работы, в котором установлен триггер рабочего состояния ТРС, а микропрограмма зацикливается на адресе 10F, непрерывно анализируя состояние ТРС, как это было описано в предыдущей статье (он сбрасывается при нажатии некоторых кнопок пульта).

Нажатие кнопки «Прерывание» приводит к установке триггера прерывания пульта управления ТППУ, что, в конечном итоге, вызывает внешнее прерывание с соответствующим кодом. Если в момент нажатия внешние прерывания запрещены, запрос прерывания сохраняется до тех пор, пока не будет обслужен или не будет выполнен сброс процессора.

Состояние поворотного переключателя выбора канала и восьми тумблеров адреса устройства заносится в десятиразрядный регистр адресных переключателей ввода РАПВ — они задают адрес устройства загрузки.

Нажатие кнопки «Ввод» (при положении переключателя «Загрузка» в положении «Начальная загрузка» — последний относится к пульту ручной работы и находится в левой нижней части пульта управления) инициирует процесс начальной загрузки программы. Технически при этом происходит переход на микропрограмму по адресу E04.

Кроме запуска процесса загрузки, нажатие кнопки «Ввод» устанавливает два триггера: Т2 и ТИВП. Триггер Т2 позднее анализируется микропрограммой: его нулевое состояние свидетельствует о том, что запуск процессора был инициирован не нажатием кнопки «Ввод», а сигналом другого процессора вычислительного комплекса ВК-1010; в зависимости от состояния этого триггера микропрограмма реализует либо полноценную загрузку с указанного внешнего устройства, либо только выборку уже подготовленного другим процессором PSW. Триггер ТИВП зажигает на пульте индикатор выполнения начальной загрузки («ввода программы») — последний будет гореть до тех пор, пока первый этап загрузки не будет успешно завершён.

Пульт ручной работы

Пульт ручной работы занимает среднюю и левую часть нижней панели пульта управления, находясь рядом с пультом оператора. Он обеспечивает выполнение ряда ручных операций, которые иногда требуются оператору машины, но обычно применяются инженерным персоналом.

Кнопка «Сброс системы» запускает микропрограмму с адреса E02. Последняя выполняет собственно сброс и переводит процессор в режим ручной работы, установив триггер ТРС. По сути, микропрограмма сброса является частью микропрограммы обработки включения питания: последняя сначала выполняет проверку основного оборудования, а затем осуществляет сброс и переход в ручной режим.

Нажатие кнопки «Повтор. РССП» запускает микропрограмму по адресу E08. Эта микропрограмма сначала выполняет сброс, а затем загружает PSW из нулевой ячейки памяти и начинает выполнение программы под управлением этого PSW. Эта операция является нестандартной для Системы 360, но в расширенном виде была стандартизирована в Системе 370 под названием «прерывание повторного пуска». Особенно полезна она в многопроцессорном комплексе, где один процессор с помощью соответствующего приказа может запустить работу прочих процессоров.

24 тумблера группы «Адрес» в зависимости от использования задают адрес основной памяти, памяти ключей защиты, местной памяти или ДЗУ. Они доступны через регистр адреса пульта управления РАПУ. Последний является псевдорегистром: он не имеет физических триггеров, а представляет собой схему выдачи в процессор информации, набранной на переключателях.

Переключатель «Выбор памяти» задаёт тип памяти, к которому относится набранный на пульте адрес — ОП, ПКЗ или МП. Его положение учитывается микропрограммами чтения и записи памяти в рамках выполнения соответствующих пультовых операций.

32 других тумблера образуют регистр информации пульта управления РИПУ. В частности, на них набирается информация, которая записывается в память при выполнении соответствующей пультовой процедуры.

Кнопка «Уст. РССП[40/63]» заносит адрес, набранный на тумблерах регистра адреса пульта управления РАПУ, в биты РССП[40/63], т. е. обеспечивает загрузку нового адреса следующей команды.

Кнопка «Начать» заносит адрес, набранный на переключателях, в РАДЗУ, тем самым осуществляя переход на заданную микрокоманду.

Нажатие кнопок «Запись» и «Счит.» вызывает переход на микрокоманды E20 и E40 соответственно. Начинающиеся ими микропрограммы реализуют пультовые операции записи в память и считывания из памяти.

Переключатель «Род работы» имеет три положения: «Шаг.», «Авт.» и «Один.». Для обычного выполнения программы он должен находиться в положении «Авт.». В положении «Шаг.» обеспечивается покомандное выполнение: при нажатии кнопки «Пуск» выполняется одна команда и обрабатываются все имеющиеся запросы прерываний, после чего процессор опять переходит в состояние останова. В положении «Один.» обеспечивается выполнение по одной микрокоманде, причём для выполнения очередной микрокоманды необходимо начать кнопку «Начало».

Кнопки «Пуск» и «Стоп» позволяют переводить процессор между состояниями «стоп» и «работа»: они влияют на состояние триггера ТРС. В частности, нажатие кнопки «Пуск» сбрасывает ТРС, но, если переключатель «Род работы» находится в состоянии «Шаг.» или «Один.», этот триггер будет установлен вновь, благодаря чему после выполнения одной команды процессор вновь остановится.

Переключатель останова по сравнению адреса имеет три положения. В положении «Обр.» осуществляется обычная обработка без возможности останова по адресу. Положения «Ком.» и «Дан.» используются для останова процессора при совпадении адреса команды или данных, находящегося в РАСП, с адресом, набранным на пульте.

Некоторые переключатели пульта не описаны. Например, на рисунке виден безымянный трёхпозиционный переключатель, две позиции которого подписаны как «ОБР» и «БЛОК». Вероятно, этот переключатель задаёт способ обработки машинных ошибок: в положении «ОБР» они обрабатываются обычным образом (приводят к прерыванию от схем контроля), в положении «БЛОК» игнорируются, а в третьем положении вызывают немедленный останов процессора (для него уместна подпись «ОСТ»: в описании работы схем контроля упоминаются сигналы БЛОК и ОСТ).

Пульт инженера

Выше пульта оператора и пульта ручной работы расположен пульт инженера, включающий органы управления, необходимые для поиска неисправностей процессора.

Тумблер останова по адресу ДЗУ позволяет остановить процессор, когда в РАДЗУ будет находиться адрес, совпадающий с набранным на пульте. Технически останов достигается выработкой при совпадении адресов сигнала блокировки дешифраторов микроопераций, в результате чего микрокоманда выбирается из ДЗУ, но не выполняется.

Тумблер приёма адреса в РАДЗУ позволяет разрешить приём в РАДЗУ адреса, набранного на переключателях пульта, при нажатии кнопки «Нач.».

Тумблер «Цикл./Такт.» управляет выполнением микрокоманды в режиме выполнения одиночных микрокоманд, т. е. когда переключатель режима работы находится в положении «Один.». В положении «Цикл.». дешифраторы анализов блокируются, а считанная микрокоманда выполняется циклически, без повторного считывания из ДЗУ. В положении «Такт.» блокируются все дешифраторы, однако при нажатии кнопки «Нач.» блокировка снимается на время одного из полутактов С1 и С2 или на время обоих полутактов в зависимости от положения переключателя «Режимы ДЗУ». Таким образом, эти органы управления позволяют многократно выполнять одну и ту же микрокоманду или её часть.

Тумблер «Чт. сер.» обеспечивает непрерывное считывание из ДЗУ микрокоманды, адрес которой набран на пульте. Этот режим предназначен, надо полагать, для наладки ДЗУ.

Тумблер «Бл. ДШ» блокирует работу всех дешифраторов микроопераций и обычно используется совместно с предыдущим для отладки процесса считывания микрокоманды без её фактического выполнения.

Имеется также группа переключателей для обслуживания оперативной памяти и для управления двухмашинным комплексом ВК-1010. В частности, в правом верхнем углу расположен пульт проверки ОП, упоминавшийся в статье, посвящённой обработке ошибок и диагностике процессора.

Индикаторы

Индикатор «Ввод» горит, пока продолжается процесс первоначальной загрузки программы, инициированный нажатием кнопки «Ввод». Технически он отражает состояние триггера ТИВП, устанавливаемого этой кнопкой и сбрасываемого микрооперацией ТИВП:=0 после технически успешного завершения загрузки.

Лампочка «Ожидание» горит, когда установлен бит РССП[14]. В состоянии ожидания процессор реагирует на разрешённые прерывания, но команды не выполняет.

Лампочка «Сист.» горит, если процессор находится в состоянии «счёт», а не «ожидание», т. е. выполняет какие-либо команды, либо если каналы ввода-вывода выполняют какие-либо операции ввода-вывода.

Лампочка «Руч.» горит, если процессор находится в состоянии останова (ручной работы). Строго говоря, ей управляет не уже упоминавшийся триггер ТРС, а триггер индикации состояния ТИС, который устанавливается равным триггеру ТРС по микрооперации ТИС:=ТРС перед началом выполнения новой команды.

Лампочка «Пров.» горит, если какие-либо переключатели пульта находятся в положении, отличном от необходимого для обычной работы процессора.

Группа индикаторов показывает состояние системы электропитания:

-

«Сеть» — общий индикатор наличия напряжения первичной электросети на стойке питания;

-

«Питание включено» — набор лампочек, отражающих подачу питания на различные блоки машины;

-

«Дистанционно» — набор лампочек, показывающих, что соответствующие блоки питания управляются централизованно с пульта управления, а не местными переключателями;

-

«Авария» — набор лампочек, показывающих возникновение проблем с источниками питания различных блоков;

-

«Асим.», «Макс.», «Мин.» — индикаторы, показывающие работу источников питания в асимметричном режиме, режиме выдачи максимально или минимально возможного напряжений питания.

Помимо перечисленных, имеется несколько групп индикаторов и управляющих ими переключателей, позволяющих вывести на пульт содержимое различных внутренних регистров процессора.

Общая оценка

Собственно, общую оценку я дал в самой первой статье, назвав ЕС-1030 худшей из всех машин Единой системы, здесь же я изложу некоторые технические причины для такой оценки.

Производительность

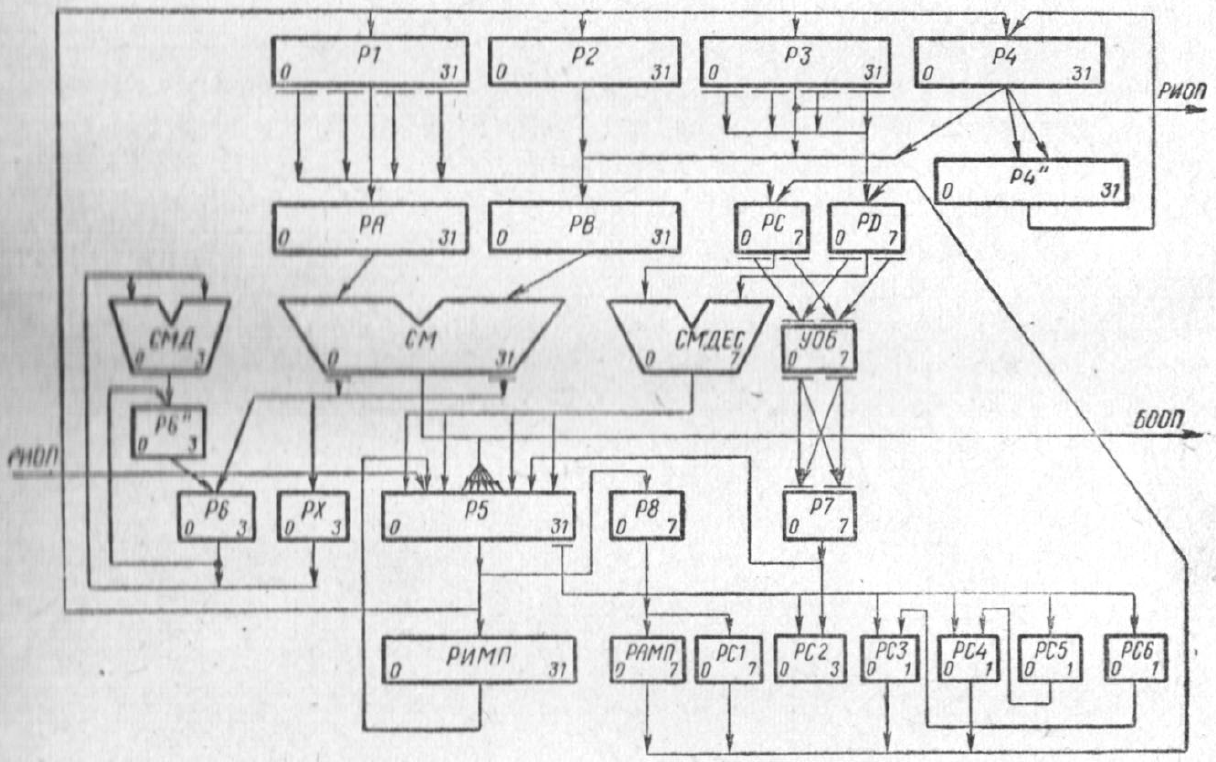

Что арифметико-логический блок, да и весь процессор, очень сложен, было понятно из простого перечисления состава регистров и списка пересылок между ними. В АЛБ присутствует семь 32-разрядных, четыре 8-разрядных и два 4-разрядных регистра, а также один 8-разрядный, один 4-разрядный и четыре 2-разрядных регистра-счётчика, причём один из 32-разрядных (Р4) и один из 4-разрядных (Р6) регистров и все счётчики содержат также регистры-дублёры (для выполнения счёта и сдвигов), что в сумме даёт 340 триггеров-защёлок — и это не считая триггеров, относящихся к местной и основной памяти или входящих в состав управляющих регистров, а также контрольных разрядов и всяких отдельных триггеров вроде ТЗН1 и ТЗН2, а там их набежит явно больше сотни. Для сравнения: у процессора ЕС-1020 для логически аналогичных функций используются всего 73 триггера.

Не отстают и блоки обработки данных. У ЕС-1020 имеется всего одно универсальное 8-разрядное АЛУ, у ЕС-1030 — один 32- и один 4-разрядный двоичные сумматоры, один 8-разрядный двоично-десятичный сумматор и узел обработки байтов, выполняющий некоторые логические функции и сравнение байтов, а также входящие в состав регистров цепи сдвига на 1, 2 или 4 разряда.

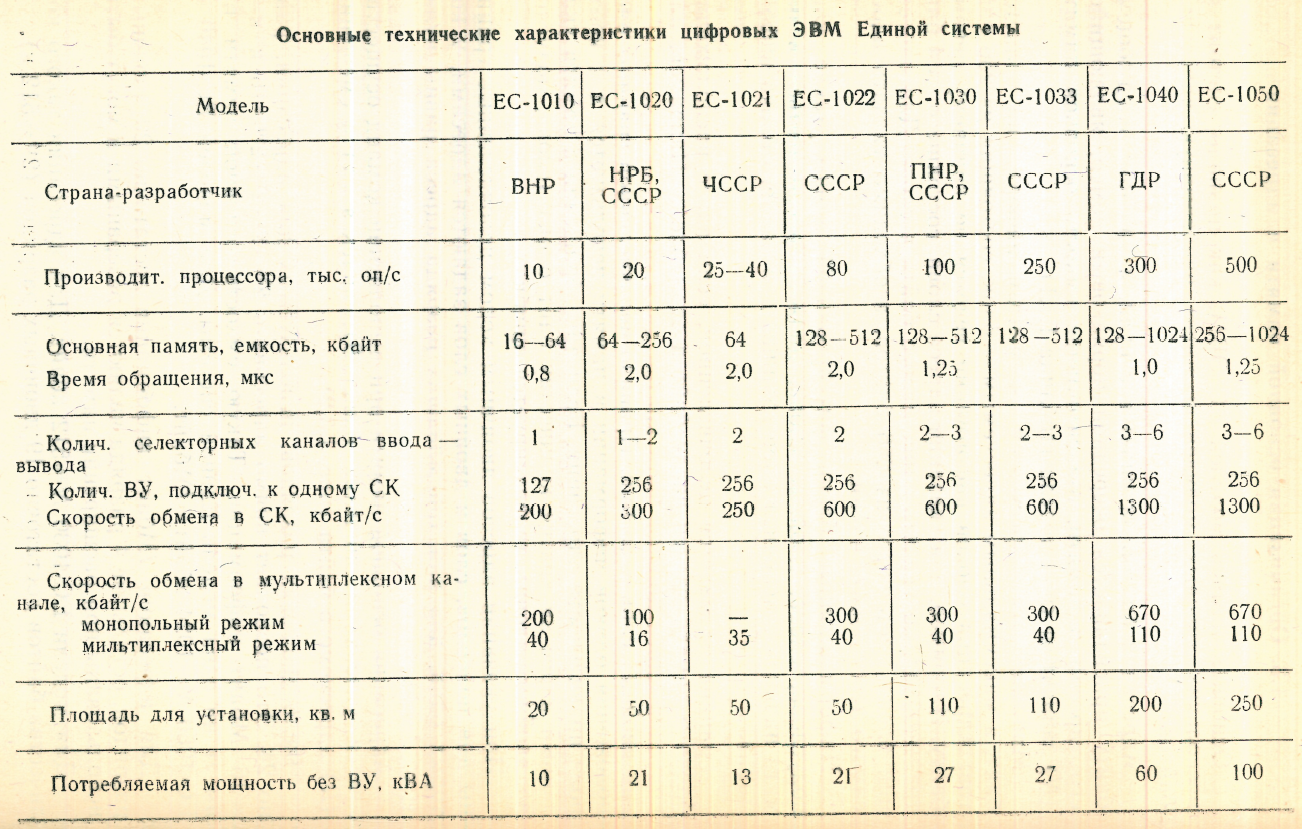

Такое резкое увеличение объёма аппаратуры, особенно с учётом использования специальной местной памяти для хранения содержимого программно доступных регистров (вместо обычной оперативной памяти, как это имеет место в ЕС-1020), было бы оправданным, если бы привело к очень значительному росту производительности. В отличие от ЕС-1020, для которой приведено время выполнения буквально каждой команды, по ЕС-1030 таких сведений нет, однако кое-какая всё-таки информация имеется. Во-первых, в первой части курса лекций по ЕС-1030 приводится такая сводная таблица по всем эксплуатировавшимся на тот момент ЕС ЭВМ:

Методика оценки производительности не приводится, и остаётся предположить, что оценивали производительность на научно-технических задачах, интенсивно использующих операции с плавающей запятой, по одной из методик «Гибсон» — это был типичный подход для СССР, где производительностью на экономических задачах и задачах общего назначения (обработка, главным образом, двоичной целочисленной, двоично-десятичной и текстовой информации) обычно пренебрегали, хотя в реальных народнохозяйственных задачах преобладали как раз вычисления именно такого рода. ЕС-1030 по сравнению с ЕС-1020 выглядит, казалось бы, весьма неплохо, показывая 100 тыс. операций в секунду против 20 тыс.

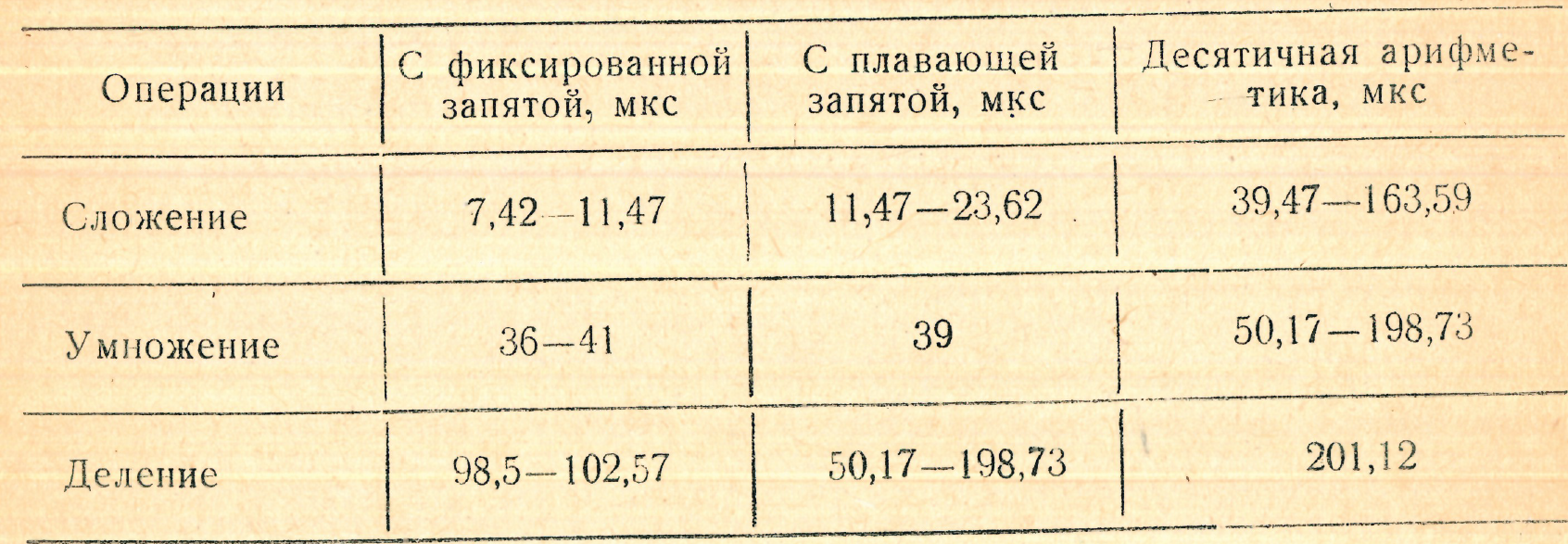

Обратимся теперь к другой таблице, из третьей части курса лекций [2]:

Как видим, даны времена выполнения всего нескольких типов операций: сложения, умножения и деления при обработке целых чисел («с фиксированной запятой», как их обычно именовали), вещественных чисел и упакованных десятичных чисел.

Теперь посмотрим, какие времена выполнения этих же команд в микросекундах даёт документация на процессор ЕС-1020:

|

|

Целые |

Вещественные |

Десятичные |

|

Сложение |

20 или 37 |

62/93 или 74/111 |

78–129 |

|

Умножение |

338 или 352 |

489/1239 или 502/1252 |

172–1810 |

|

Деление |

390 или 402 |

389/2059 или 403/2073 |

238–4032 |

Для команд обработки целых чисел на ЕС-1020 первое значение соответствует операции формата RR, второе — формата RX с использованием базового и индексного регистров, т. е. представляют собой минимально и максимально возможное время, затрачиваемое на данную операцию. Для команд обработки вещественных чисел первая пара значений соответствует формату RR для коротких и длинных операндов, вторая — формату RX. Для команд обработки десятичных чисел указаны минимальная и максимальная длительности, что определяется размерами операндов.

С обработкой вещественных чисел всё понятно: ЕС-1030 превосходит ЕС-1020 в 5–10 раз в зависимости от команды и размера операндов: всё-таки используются работающие более-менее параллельно 4-байтовый сумматор, отдельный узел для сравнения мантисс в составе УОБ, отдельный счётчик числа итераций, отдельный счётчик, в котором формируется итоговый порядок, плюс имеется возможность сдвинуть за один такт на два или четыре разряда, тем самым значительно ускорив выравнивание порядков и нормализацию — у ЕС-1020, напомним, на всё про всё имеется единственное однобайтовое АЛУ. Особенно велик разрыв на операциях умножения и деления длинных операндов: у процессора ЕС-1020 для размещения всего необходимого не хватает «железных» регистров, поэтому приходится использовать рабочую область в локальной памяти — а технически это медленная оперативная память.

С целочисленными умножением и делением картина, в общем-то, та же самая, разве что разрыв несколько меньше.

А вот с десятичными операциями всё интереснее. Умножение на ЕС-1030 ожидаемо выполняется значительно быстрей. То же самое наверняка касается и деления, хотя опубликованное в [2] единственное значение не может считаться достоверным: при операндах переменной длины операция просто не может выполняться за фиксированное время. А вот на сложении ситуация иная: минимальное время на ЕС-1020 всего в два раза хуже, чем на ЕС-1030, а максимальное — даже лучше, причём почти на четверть!

Наконец, посмотрим на целочисленное сложение: 20–37 мкс у ЕС-1020 против 7,42–11,47 мкс у ЕС-1030. Более мощная машина однозначно быстрей, но всего в 2,5–3 раза.

Проанализировав времена выполнения команд, попробуем оценить, насколько эффективно разработчики ЕС-1030 использовали потенциальные возможности «железа» для реализации простых операций.

Время выполнения одной микрокоманды на ЕС-1020 составляет 1000 нс, на ЕС-1030 — 670 нс, т. е. даже простое сокращение времени такта должно на треть ускорить выполнение команд. У ЕС-1020 основная память имеет время считывания 1000 нс (собственно, к нему и привязана длительность такта) и ширину обращения два байта, у ЕС-1030 — 750 нс и четыре байта, т. е. пропускная способность памяти больше в 2,5 раза. У ЕС-1020 программно доступные регистры процессора размещены в локальной памяти, которая технически является обычным ОЗУ с тем же временем цикла и шириной выборки; у ЕС-1030 местная память имеет ширину четыре байта и время выборки не свыше 500 нс — то пропускная способность выше уже в четыре раза. ЕС-1030 имеет четырёхбайтовый сумматор и большое количество аппаратных регистров — а соответственно, простое сложение или вычисление адреса она выполняет за один такт, а ЕС-1020 — за три (адрес) или четыре (данные). Наконец, у ЕС-1030 адрес команды находится в отдельном регистре-счётчике, значение которого увеличивается аппаратно и одновременно с выполнением других операций, а ЕС-1020 хранит его в обычных рабочих регистрах и изменяет с помощью обычного АЛУ.

Исходя только из времени цикла и ширины сумматора, команда сложения формата RR на ЕС-1030 должна бы выполняться примерно в семь раз быстрей, чем на ЕС-1020, поскольку продвижение адреса команды у ЕС-1030 вообще «бесплатное» и совмещается с другими операциями, а собственно сложение занимает один такт, в то время как ЕС-1020 вынуждена будет потратить три такта на продвижение адреса команды и ещё четыре такта на собственно сложение. Но мы видим, что разница не дотягивает и до трёх раз, а значит, ЕС-1030 расходует время весьма неэффективно — а ведь данный тип команд относится к одним из наиболее часто используемых, причём в задачах любого вида.

Вспомним теперь, что при выполнении «кода общего назначения», а не математических задач, весьма значительную роль играют логические операции, пересылка информации из одного места памяти в другое и тому подобные манипуляции, а вот частота использования умножения, деления и особенно операций с плавающей запятой стремится к нулю. ЕС-1020 выполняет логические операции с той же скоростью, что и целочисленное сложение, что неудивительно: принцип их реализации один и тот же, разница лишь в собственно выполняемой в АЛУ операции и в правилах установки кода условия. А вот у ЕС-1030 эти операции выполняются побайтово, ведь у неё нет полноценного 32-разрядного АЛУ, а только сумматор — а соответственно, на саму операцию она будет тратить четыре такта, т. е. ровно столько же, сколько ЕС-1030; как следствие, разница во времени выполнения подобных команд снизится с трёх до примерно двух раз. Что же касается, скажем, сравнения или пересылки «память-память» — весьма частые операции при работе трансляторов или финансово-экономических программ, формирующих «простыни» для распечатки, — то ЕС-1030, скорее всего, проиграет ЕС-1020, ведь, как мы видели, даже десятичное сложение при достаточно длинных операндах она выполняет медленнее!

Таким образом, можно утверждать, что лишь на научно-технических задачах ЕС-1030 демонстрирует производительность, более-менее адекватную росту её сложности по сравнению с ЕС-1020; на задачах экономических или общего назначения разрыв будет не так уж и велик, а в «патологических» случаях не исключена даже победа ЕС-1020, хотя это, безусловно, и весьма маловероятно. Попробуем разобраться, в чём причины столь невысоких результатов.

Выборка команд

Из предыдущей статьи видно, что на анализ состояния процессора, проверку наличия запросов прерываний и запросов обновления таймера требуется выполнить четыре микрокоманды — и так при выполнении каждой команды процессора! Для «долгоиграющих» команд это представляется не очень критичным: эти четыре такта «растворяются» в тех десятках или сотнях тактов, которые необходимы на выполнение собственно команды. Однако для элементарных команд эти лишние затраты времени соизмеримы со временем выполнения самой команды и даже, если уж говорить строго, превосходят его: на сложение «регистр-регистр» ЕС-1030 тратит 7,42 мкс — т. е. 11 микрокоманд, в то время как само сложение занимает лишь одну из них (а вот ЕС-1020 — 20 микрокоманд, из них 4 занимает собственно сложение, т. е. «плотность полезного микрокода» у неё оказывается вдвое выше, несмотря на намного меньший объём аппаратуры).

Таким образом, можно констатировать, что анализ режимов процессора и наличия запросов прерываний в ЕС-1030 сделан крайне неэффективно: его можно выполнить за одну микрокоманду, совместив все виды анализа в одной микрооперации. Кстати говоря, ЕС-1020, по сути, вообще не тратит времени на эти анализы: они совмещены с попыткой выборки первого полуслова команды, и всё это в намного более простом процессоре!

Работа с основной памятью

Как уже говорилось, время выборки информации из ОП на ЕС-1020 составляет 1000 нс, а на ЕС-1030 — 750 нс. Однако, если мы проанализируем алгоритм работы БООП ЕС-1030, мы увидим очень печальную картину: если запрос на чтение из памяти выдаётся в такте Т1, прочитанные из памяти данные попадут в регистр Р5 лишь в такте Т5, а использоваться в работе обрабатывающих блоков смогут лишь в такте Т6 — то есть спустя 3350 нс после выдачи запроса. А вот ЕС-1020 может использовать данные уже в следующем такте — через те самые 1000 нс после выдачи запроса на чтение, которые необходимы для выполнения этого самого чтения. Таким образом, ЕС-1020 использует пропускную способность своей памяти на 100%, а ЕС-1030 — едва ли на четверть! Вот где, похоже, кроется причина, почему сложение длинных десятичных операндов эта машина выполняет уже заметно медленнее: эта операция очень сильно зависит от пропускной способности памяти. Естественно, какая-нибудь пересылка строк будет работать ничуть не эффективней.

Использование местной памяти и аппаратных регистров

Местная память ЕС-1030 в два раза шире и в два раза быстрее локальной памяти ЕС-1020, но итоговая картина опять печальна. При считывании информации из МП она попадает в регистр Р5 — а ведь он используется для приёма данных из ОП, результата операции в основном или десятичном сумматоре, а также является конечным приёмником результата работы УОБ (хотя там есть промежуточный приёмник в лице Р7). Понятно, что если в некотором такте выполняется выборка информации из МП, в этом такте уже нельзя принимать результат из обрабатывающих блоков или данные из ОП — что, по сути, убивает возможность совмещения операций, хотя «железо», в общем и целом, вполне такую возможность могло бы предоставить.

Добавим к этому странное соединение регистров с основным сумматором (к этому вопросу мы ещё вернёмся в самом конце): в качестве входа А может использоваться только и исключительно Р1, а входа В — Р2, Р3 или Р4. Соответственно, приём в Р1 и Р2 двух половин 64-разрядного операнда лишён особого смысла: всё равно на вход А мы не можем подать вторую половину, и её придётся тем или иным способом сначала передать в Р1. Как следствие, можно смело утверждать, что и большое количество аппаратных регистров нельзя использовать наиболее эффективным образом.

Другие странные решения

Кратко остановимся на других решениях разработчиков процессора ЭВМ ЕС-1030, которые вызывают, по меньшей мере, сомнения в их обоснованности.

Исполнительные блоки. У процессора имеются 32-разрядный основной двоичный сумматор, 4-разрядный вспомогательный двоичный сумматор, 8-разрядный десятичный сумматор и 8-разрядный узел обработки байтов, а также большое количество связанных с ними регистров и триггеров. Представляется, что реализация вместо всех этих блоков вместе с их входными и выходными регистрами одного 32-разрядного универсального АЛУ была бы если и сложнее по количеству затраченных микросхем, то ненамного, но обеспечила бы повышение производительности на ряде операций (особенно логических и обработки строк, которые в ЕС-1030 выполняются на однобайтном УОБ). При этом для коммутации нужных байтов памяти на те или иные байты АЛУ можно было бы предусмотреть цепи для 8-разрядных сдвигов с сохранением «лишнего» байта в специальном однобайтовом регистре; попутно такие цепи позволили бы в определённых ситуациях ускорить сдвиги, а также выравнивание и нормализацию вещественных чисел.

Счётчики. В процессоре ЭВМ ЕС-1030 имеется шесть регистров-счётчиков РС1–РС6. Это количество явно избыточно, потребное их число не превосходит четырёх (один счётчик, способный работать как один 8- или два 4-разрядных — он нужен для хранения длины или длин операндов в командах формата SS, — и три 2-разрядных счётчика для хранения номеров обрабатываемых байтов в пределах слова — опять-таки, для команд формата SS), но возможно, что их число можно сократить.

Обработка прерываний. В ЕС-1030 запросы на прерывания программные и по вызову супервизора представлены отдельными битами регистра РФП, которые устанавливаются микропрограммно при обнаружении причины для того или иного запроса, а в процессе выполнения микропрограммы выборки команды вызывают переход к микропрограмме обработки соответствующего вида прерывания. Это решение выглядит откровенно нелепым.

Обнаружение причины для этих прерываний обычно вызывает немедленное прекращение выполнения команды и переход к выполнению прерывания. В тех случаях, когда выполнение команды всё-таки завершается, а не прерывается в точке обнаружения причины прерывания, это завершение несколько отличается от обычного завершения. Скажем, при особых случаях значимости или исчезновения порядка, если соответствующее прерывание запрещено, команда завершается формированием истинно нулевого результата, а при разрешённом прерывании сохраняется тот результат, что получился, и после этого происходит прерывание.

Соответственно, нет никакой нужды использовать для фиксации запросов прерываний отдельные триггеры РФП и затем аппаратно анализировать их наличие и вызывать переход на ту или иную микропрограмму: переход на обработку прерывания правильно осуществлять прямо из микропрограммы реализации команды, где причина прерывания обнаружена (именно так сделано в ЕС-1020).

Хранение причин программных прерываний. К предыдущему пункту примыкает выделение для хранения причин программных прерываний 15-разрядного регистра РОЦ. Посмотрим, как концептуально обрабатывает программное прерывание процессор ЭВМ ЕС-1030.

-

Микропрограмма, реализующая выполняемую в данный момент команду, неким анализом определяет наличие особого случая, который приводит к программному прерыванию (скажем, команда деления обнаружила попытку деления на нуль).

-

Эта микропрограмма выполняет микрооперацию

РОЦ[1/3,7/15]:=КОНСТ, устанавливающую в регистре РОЦ бит, соответствующий конкретной причине прерывания. Причина задаётся константой 1–15 в самой микрокоманде, а для установки нужного бита собран специальный дешифратор, устанавливающий тот или иной бит в зависимости от константы. (Заметим, что биты 4/6 связаны с особыми случаями доступа к памяти и устанавливаются другим способом, но в данном случае это неважно). -

В зависимости от конкретного особого случая микропрограмма выполнения команды либо завершает выполнение команды более-менее обычным способом, либо сразу переходит на микропрограмму выборки команды.

-

Микропрограмма выборки анализирует режимы процессора и наличие запросов прерываний, попадая, в итоге, на микропрограмму программного прерывания.

-

Микропрограмма программного прерывания заносит в РССП[16/31] код программного прерывания. Численно он равен номеру установленного в РОЦ бита, что определяется чисто микропрограммным анализом, кратко описанным в предыдущей статье. Заметим, что этот номер совпадает со значением поля константы для микрооперации

РОЦ[1/3,7/15]:=КОНСТ. -

После этого микропрограмма сбрасывает содержимое РОЦ, записывает РССП[0/63] в ОП в качестве старого PSW программного прерывания, загружает из ОП новое PSW, заносит его в РССП и вновь переходит на микропрограмму выборки команды.

Процессор ЭВМ ЕС-1020 для аналогичной задачи, обнаружив особый случай, заносит в один из своих регистров код программного прерывания (число от 1 до 15 включительно) и сразу переходит на микропрограмму обработки программного прерывания. Таким образом, он вообще не содержит специальных средств для обработки программных прерываний — они ему попросту не нужны, вполне хватает и «универсальных» возможностей аппаратуры.

Хранение кода прерывания в РССП[16/31] является ещё одним примером расточительного использования аппаратуры. Дело в том, что код прерывания играет роль только и исключительно в составе PSW, записанного в память в процессе прерывания; внутри процессора он вообще не нужен. Соответственно, наличие аппаратных битов РССП[16/31] является очередным примером безграмотности и расточительства разработчиков процессора.

Блок обращений к оперативной памяти, как очевидно из «высокой эффективности» использования пропускной способности памяти, ничего, кроме критики не заслуживает, однако отметим дополнительно несколько связанных с ним моментов.

-

Сложность взаимодействия с блоком. Микропрограмма на протяжении нескольких тактов должна пересылать ту или иную информацию, устанавливать или сбрасывать триггеры, следить за состоянием БООП... В ЕС-1020 она просто указывает, какую операцию нужно выполнить и из какого именно регистра брать адрес — и всё, дальнейшие действия полностью управляются аппаратурой. Конечно, ЕС-1030 имеет физически независимые каналы, а также допускает создание двухпроцессорного комплекса, что требует определённых усложнений, но сводятся они, по большому счёту, к необходимости ожидать установки триггера готовности памяти, а не всего того, что в БООП творится.

-

Анализ на особые случаи доступа к памяти. В ЕС-1020 проверка на особый случай спецификации, т. е. на обращение по неправильно выровненному адресу, контролируется чисто микропрограммно (нужное количество младших разрядов адреса в процессе его вычисления контролируется на нуль), а особые случаи адресации и защиты, т. е. выход за пределы имеющейся памяти и на нарушение защиты, контролируются чисто аппаратно и аппаратно же прерывают выполнение текущей микропрограммы, передавая управление специальной микропрограмме их обработки (очевидно, что если команда пытается выполнить недопустимый доступ к ОП, её выполнение невозможно и прерывается немедленно и безусловно). В ЕС-1030 все эти особые случаи обнаруживаются смесью аппаратуры и микропрограммы, причём переход на обработку особого случая доступа осуществляется чисто микропрограммно, хотя его разумнее выполнять аппаратно (тем более, схемы для принудительной установки РАДЗУ в то или иное значение имеются — они используются, например, для перехода на различные микропрограммы выполнения пультовых операций).

-

ЕС-1020 запускает считывание ключа памяти для проверки прав доступа одновременно с запуском считывания/стирания основной памяти, а поскольку память ключей защиты работает быстрее, чем ферритовое ОЗУ, нарушение прав доступа проверяется раньше, чем закончится считывание ОП, а соответственно, недопустимого использования информации не происходит. В ЕС-1030 обращение к памяти ключей происходит достаточно поздно, что не позволяет быстро запустить обращение к ОП и ещё больше увеличивает суммарное время доступа.

-

Вообще говоря, в машинах, подобных ЕС-1030 и ЕС-1050, правильней было бы выполнять память ключей защиты в составе стойки основной памяти, а не в составе процессора, и определённым образом переделать интерфейс между памятью и процессором с каналами. Во-первых, это освободило бы процессор и каналы от нужды самостоятельно управлять памятью ключей в процессе обращения к ОП (проверкой прав доступа в любом случае «рулит» аппаратура); во-вторых, позволило бы комплектовать машины произвольным объёмом ОП, не ограничиваясь лишь пределом, обусловленным имеющейся ПКЗ; а в-третьих, потенциально позволило бы модернизировать машины, заменив медленную память на более быструю (процессор или канал выдаёт запрос к памяти и ожидает сигнала готовности, а не рассчитывается на строго определённую длительность цикла). Правда, эти претензии относятся больше к московскому НИЦЭВТу, который разрабатывал ЕС-1050 и память как для неё, так и для ЕС-1030.

Аппаратный контроль и диагностика. Соответствующие блоки включают весьма значительный объём аппаратуры. Между тем, процессор ЕС-1030 имеет микропрограммное управление, и абсолютно логично было бы почти все диагностические операции выполнять микропрограммными средствами: трансформаторное ДЗУ, в отличие от логических микросхем, можно считать условно бесплатным, а для проверки работы самого ДЗУ достаточно простой схемы, считывающей всё его содержимое подряд и контролирующей чётность микрокоманд (собственно, такая схема имеется). В частности, безумным расточительством является использование тестов локализации неисправностей, загружаемых с магнитной ленты. Такое решение является логичным, а возможно, и единственно разумным для ЕС-1050, имеющей чисто схемное управление, но никак не для ЕС-1030 или любой другой микропрограммной машины.

То же самое касается и обработки сбоев. Вместо создания сложного аппаратного автомата, управляющего процессом сохранения состояния в ОП, причём частично в обход БООП, следовало бы всю логику реализовать микропрограммно: при отказе блока микропрограммного управления, БООП или самой ОП сохранить состояние в полном объёме в любом случае невозможно, при отказе других блоков даже при успешном сохранении состояния невозможно обработать прерывание от схем контроля по причине реальной неработоспособности процессора, а вот при случайном сбое микропрограммной реализации более чем достаточно (что и сделано в ЕС-1020).

ЕС-1030 и IBM 360/50

В статье «ЭВМ ЕС-1033: создание, особенности структуры и элементной базы» её автор А.У. Ярмухаметов, являвшийся одним из разработчиков этой машины, подвергает жёсткой критике ЕС-1030 (в справедливости которой сомневаться не приходится), которую приходилось выпускать Казанскому заводу в убыток себе, и, помимо прочего, говорит, что «ЕС-1030 – «цельнотянутая» копия IBM 360/50» (забегая вперёд на пару циклов статей, замечу, что ЕС-1033 — полностью отечественная разработка, для которой создали даже свою собственную микросхему К155ХЛ1, не имеющую аналога «у них»). Вот на этом вопросе стоит остановиться подробнее.

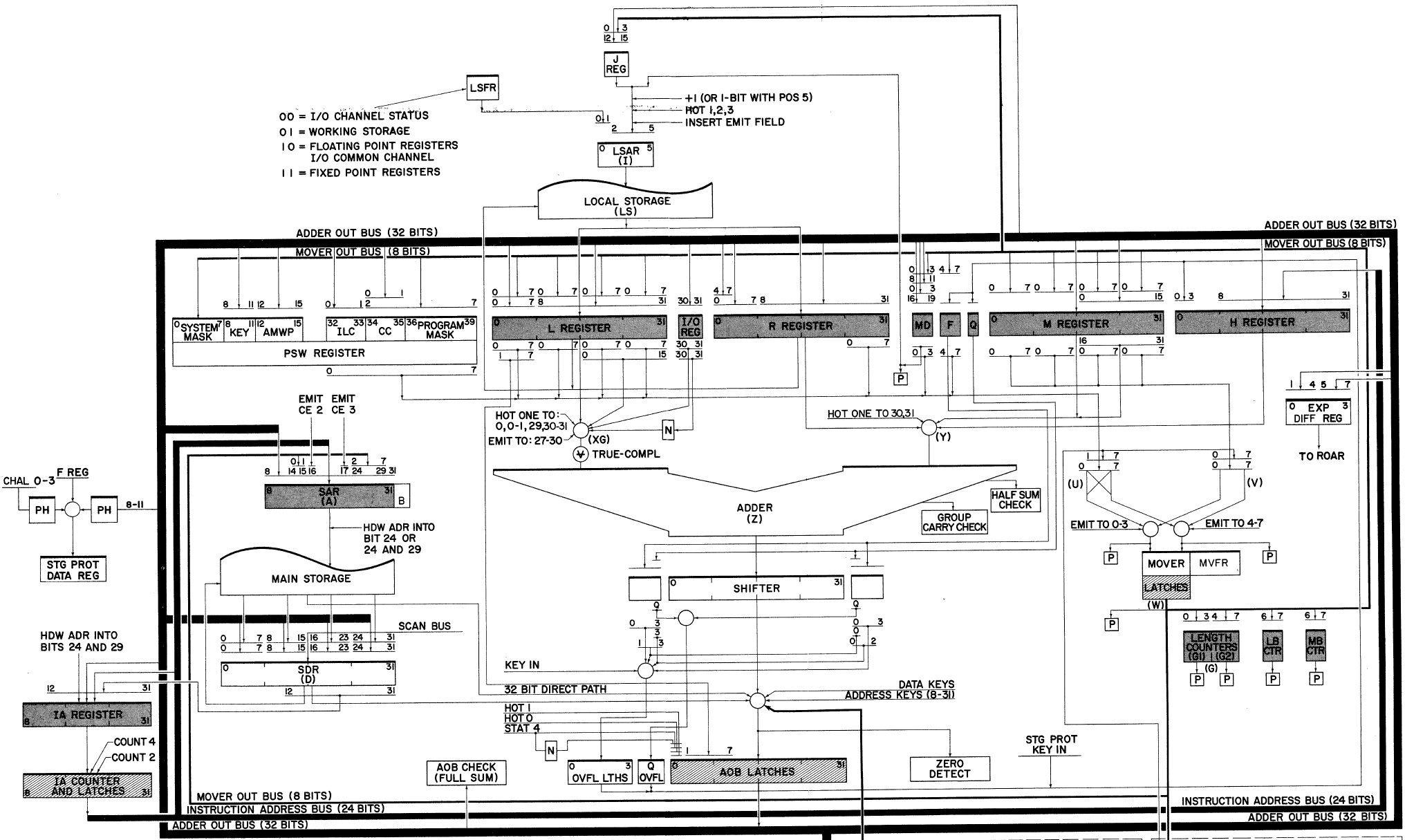

Чтобы оценить это заявление более-менее объективно, сравним блок-схему арифметико-логического блока ЕС-1030 с блок-схемой процессора IBM 360/50. Последнюю можно найти в нескольких документах, выложенных на ftp://bitsavers.informatik.uni-stuttgart.de/pdf/ibm/360; вероятно, наиболее читаемым из них в данном случае является Z22-2833-4 «System/360 Model 50. 2050 Processing Unit. Field Engineering Diagram Manual». На помещённом ниже скриншоте обрезана нижняя часть блок-схемы, показывающая соединение каналов ввода-вывода с процессором и памятью: для целей данного анализа оно несущественно.

Первое, что бросается в глаза, — это наличие в 360/50 32-разрядного сумматора, на один из входов которого информация подаётся только из регистра L (и ещё какого-то непонятного двухбитного регистра ввода-вывода), а вот на второй вход — из одного из трёх регистров R, M и H; результат работы сумматора может быть сдвинут и помещается в выходной регистр, называемый AOB LATCHES. Таким образом, общая схема включения регистров и основного сумматора выглядит идентично процессору ЭВМ ЕС-1030, включая, в первую очередь, странную подачу исходных операндов на сумматор.

Насчёт УОБ и десятичного сумматора приведённая схема определённых выводов сделать не позволяет, но имеющийся на ней MOVER вполне может заключать в себя и схемы для выполнения логических операций над байтами, и десятичный сумматор, так что можно считать, что в этой части процессор 360/50 тоже совпадает с ЕС-2030.

Однако, если присмотреться внимательней, можно увидеть явные и очень значительные различия между этими двумя процессорами.

Во-первых, нигде не видно дополнительного сумматора с его регистрами. Правда, имеется некая четырёхразрядная схема OVFL LTHS — но это больше похоже на простой счётчик количества возникших переполнений (переносов), чем на полноценный сумматор с двумя полноценными входными регистрами и возможностью участия в сдвигах, как это имеет место в отечественной машине.

Во-вторых, имеется разница в подключении основной памяти (MAIN STORAGE). Адрес в её адресный регистр (SAR) поступает либо с выходного регистра сумматора, либо из счётчика команд (IA COUNTER), считанные данные из регистра данных памяти SDR поступают на AOB LATCHES — то есть в точности как в ЕС-1030. Но вот подлежащие записи данные подаются в SDR не из местного аналога регистра Р3 (R, M или H), а из выходного регистра сумматора.

Собственно, одного этого изменения уже достаточно, чтобы проект процессора ЕС-2030 нельзя было назвать «цельнотянутым»: оно изменяет поток данных между процессором и памятью. Но посмотрим немного дальше.

Третье важное изменение касается подключения местной памяти (LOCAL STORAGE, LS). В ЕС-2030 и входным, и выходным регистром данных является регистр Р5, т. е. выходной регистр сумматора, что не позволяет использовать МП эффективным образом, о чём говорилось выше. А вот в 360/50 странная схема подключения регистров к сумматору не создаёт таких проблем с производительностью, поскольку информация из LS может приниматься прямо либо в регистр L (аналог регистра Р1, подаваемого на первый вход сумматора), либо в регистр R (аналог одного из регистров Р2–Р4, подаваемого на второй вход сумматора). Соответственно, выполняя операцию на сумматоре с приёмом результата в AOB LATCHES, процессор 360/50 может одновременно считывать из LS значение для следующей операции и помещать его в регистр L, являющийся «узким местом» в организации потоков данных.

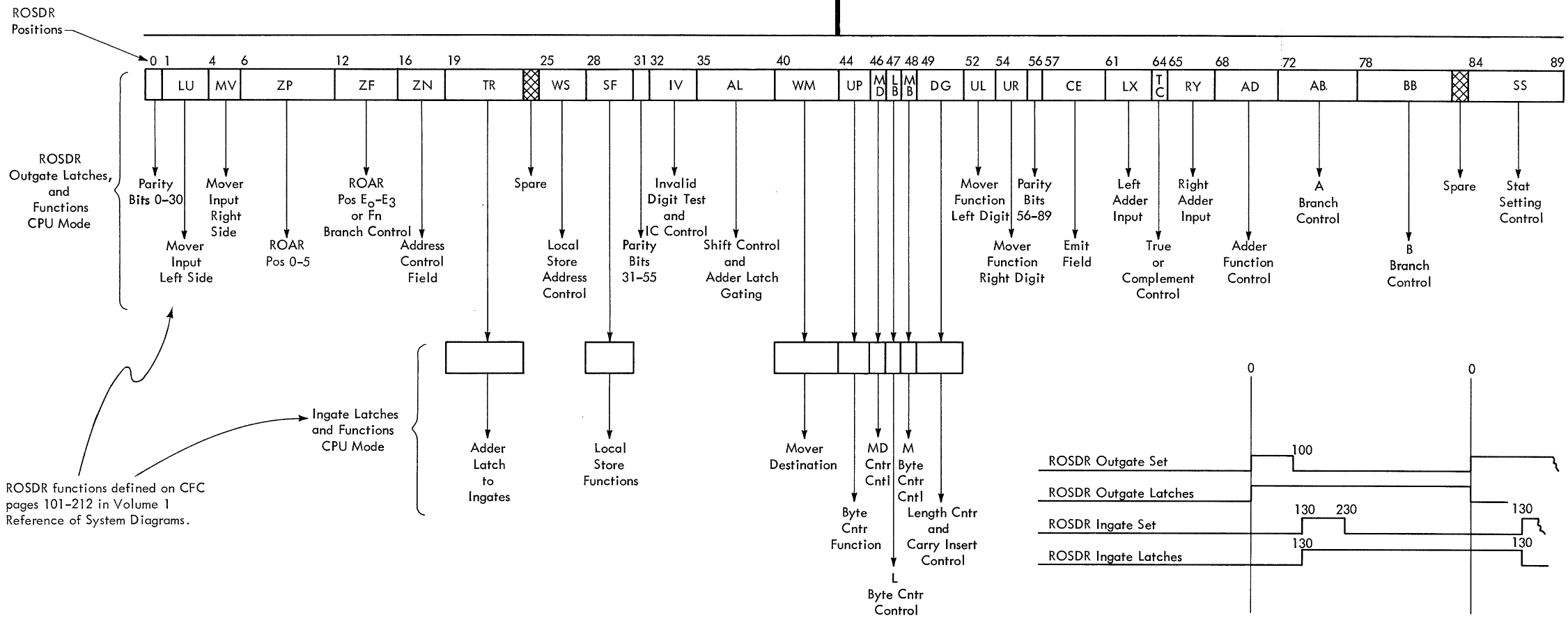

Ну и напоследок посмотрим на формат микрокоманды 360/50 (кстати, ПЗУ микропрограмм в этой машине конденсаторное). Точное назначение и кодирование полей в имеющихся документах не описано, но нам достаточно и самого формата, взятого из того же документа:

Как видим, микрокоманда имеет длину 90 бит вместо 72 у ЕС-2030, а соответственно, и микропрограммы у этих машин будут кардинально отличаться. Попутно заметим, что структура микрокоманды «американки» ближе к традиционным микропрограммам, где поля имеют более-менее фиксированное функциональное назначение: мы видим, например, Local Storage Functions (28:30), Mover Function Left Digit (52:53), Right Adder Input (65:67) и др. вместо достаточно хаотического распределения управляющих сигналов по полям микрокоманды ЕС-2030.

Таким образом, можно смело утверждать, что А.У. Ярмухаметов погорячился с «цельнотянутостью» проекта процессора ЭВМ ЕС-1030: это была всё-таки своя разработка. Очевидно, что она опиралась на IBM 360/50, что доказывается близкой организацией исполнительных блоков, регистров и потоков данных в их процессорах, но была при этом существенно переработана — причём в откровенно худшую сторону.

Ну и напоследок риторический вопрос. Если бы разработка ЕС-1030 велась при товарище Сталине, не сочли бы её разработчиков вредителями и врагами народа со всеми вытекающими?..

Автор: SIISII