Финальный этап создания электронного продукта — серийное производство, именно оно в конечном итоге определяет качество устройства. Пользователь не сможет оценить идеальную программную и аппаратную платформу новой электроники, если на сборочном конвейере произойдет сбой, поэтому контроль функциональности и тестирование сборки — обязательные этапы массового производства.

Читатели этой статьи познакомятся с основными методиками и задачами тестирования электронных устройств и получат общее понимание обеспечения качества на производстве. Особое внимание будет уделено достоинствам и недостаткам различных методов тестирования.

Виды тестирования на производстве. Краткий обзор

В общем виде процесс подготовки и тестирования электронного изделия на производстве выглядит так:

- Проектирование и создание стенда для прошивки и тестирования с использованием JTAG/ICT-тестирования

- Разработка системы тестов и параметров контроля качества и приемки на производстве

- Автоматизированная или ручная проверка функциональности

Тестирование устройства и его отдельных частей в процессе производства можно реализовать на базе следующих методик и технологий:

1. Визуальный автоматизированный контроль (AOI, AXI) — это предварительная проверка качества, которая используется на любом контрактном производстве, она проходит на разных стадиях монтажа печатных плат, в том числе с использованием рентгеновского излучения для проверки невидимых глазу или стандартным оптическим системам мест.

На фото: Печатная плата проходит визуальный автоматизированный контроль (AOI). По результатам проверки тестировщик получит данные по обнаруженным дефектам. Источник: Acculogic.

2. Внутрисхемное тестирование (ICT/FICT) – проверка соединений и компонентов на печатной плате, анализ электрических параметров всей схемы либо отдельных ее участков.

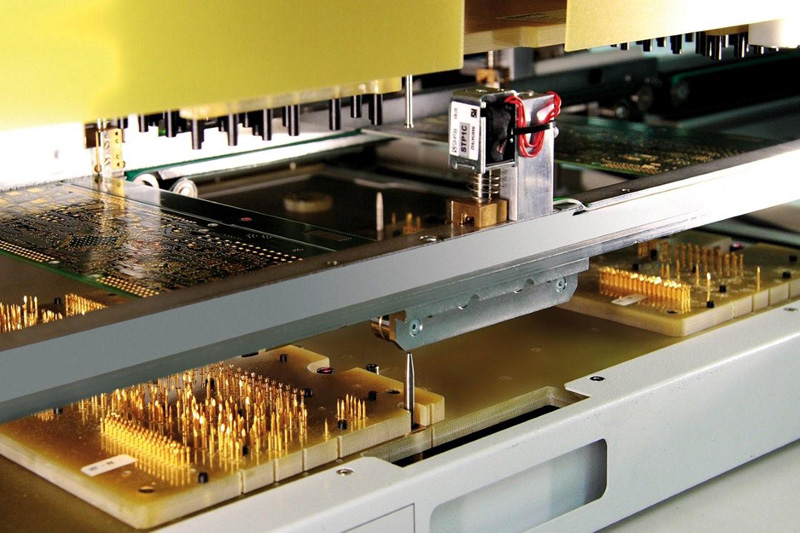

Данный метод использует контакт пробников с узлами собранной платы: это может быть как стационарное поле контактов («ложе гвоздей», англ. – bed of nails), так и «летающие щупы» (flying probe) или «летающие матрицы». Часто требует использования сложного и дорогостоящего оборудования, технологической подготовки, изготовления специальной оснастки.

На фото: тестирование печатной платы «летающими щупами» (flying probes).

Источник: Acculogic.

3. Периферийное/граничное сканирование (boundary scan) — тестирование с использованием JTAG. Основано на использовании в микросхемах поддержки стандарта IEEE 1149.

4. Функциональное тестирование (FCT) — проверка собранных или частично собранных устройств на выполнение заданной функциональности и на соответствие параметрам, которые заложены в спецификации на прибор.

Все перечисленные методики позволяют оценить качество электроники в процессе производства, однако в некоторых случаях тестирование устройства проводится только на финальном этапе. Это так называемое тестирование после окончательной сборки (EOL) — проверка функциональности и соответствия спецификации. Оценивается не только качество, но также стабильность и надежность устройства. Такой анализ электроники проходит с использованием сложного стендового оборудования, которое имитирует систему, в составе которой работает тестируемое устройство. Если по результатам такой проверки процент брака превышает предварительную оценку, тогда корректируется технология производства и запускается очередная пробная партия устройств. И так в несколько итераций.

На практике лучшие результаты показывают те методики, которые используются в процессе производства, т.е. функциональное и внутрисхемное тестирование, т.к. они позволяют оперативно получить информацию и определить конкретные этапы, на которых появляются проблемы. Благодаря этому можно внести корректировки в производственный процесс еще до окончательной сборки устройства.

Рассмотрим эти методики тестирования более подробно, от общего к частному, начиная с анализа функциональности собранных или частично собранных устройств и заканчивая особенностями внутрисхемного тестирования печатных плат.

Функциональное тестирование на производстве

Функциональное тестирование может проводиться как в ручном, так и в автоматическом режиме. Естественно, при составлении тест-планов ручной труд стараются свести к минимуму, оставив оператору лишь подключение/отключение устройства, а также контроль годности.

При грамотном подходе эта методика способна охватить практически всю функциональность устройства за рекордно короткие сроки. Однако без разработки тестового программного обеспечения и изготовления специальной оснастки тут не обойтись.

Тестирование можно разделить на проверку основных частей устройства (процессора, памяти, прочих модулей) и проверку периферийных интерфейсов. Для тестирования процессорной части создается специальная программа, которая в автоматическом режиме задает особые параметры работы, проводит инициализацию всех микросхем устройства, опрашивает их и на основе полученных результатов делает вывод о работоспособности. После проверки основных частей проводится последовательное включение рабочего режима для каждой составной части устройства и проверка её функционала. Например, для тестирования Ethernet-интерфейсов программа поочередно проводит инициализацию каждого порта, а если их несколько, задает временные MAC- и IP-адреса, пересылает пакеты и анализирует результат.

Степень покрытия изделия тестами определяется индивидуально для каждого типа устройства на основе анализа электрической схемы, доступных для тестирования модулей и интерфейсов.

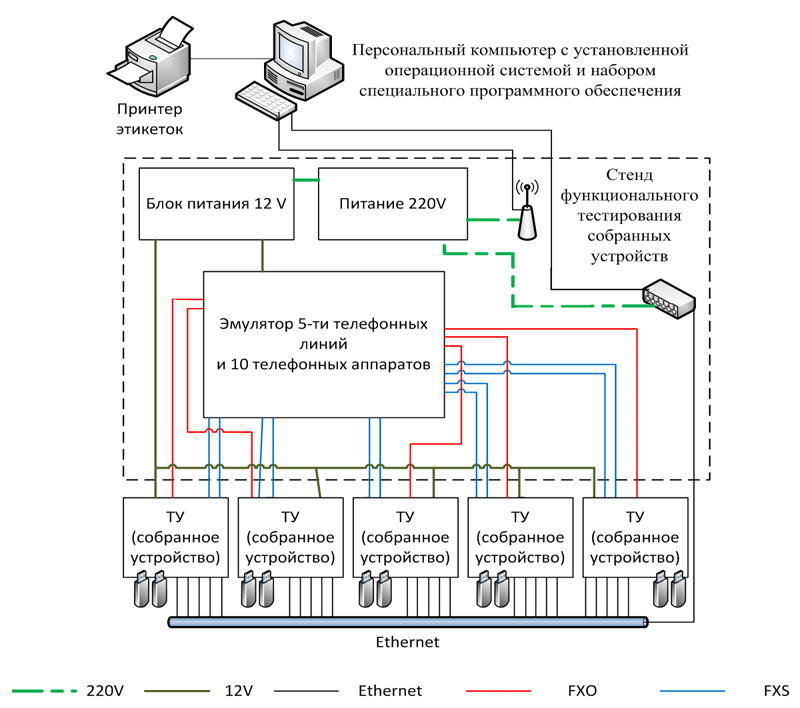

На схеме: Стенд функционального тестирования собранных устройств

Выше приведена схема стенда функционального тестирования собранных устройств. Он позволяет тестировать пять устройств одновременно, последовательно проверяя весь функционал каждого. В процессе сверяются версии прошивки отдельных модулей, и, в случае необходимости, проходит прошивка свежей версии. После удачного прохождения тестов программа выдает устройству MAC-адрес, серийный номер и предустановленные пароли.

Стенды функционального тестирования могут включать вспомогательные программные и аппаратные средства для персонализации устройства, удаленного сбора информации о тестируемых устройствах, генерации отчетности о дефектах.

На фото: Функциональное тестирование собранных устройств на фабрике в Сингапуре.

Результаты проверки отображаются на мониторе компьютера, к стенду одновременно

подключены семь приборов.

К неоспоримым плюсам функционального тестирования можно отнести возможность конечной прошивки, проверку и обновление версий ПО модулей системы, выдачу персональных данных устройству, используя высокоуровневые протоколы и скоростные интерфейсы.

Стенды функционального тестирования могут встраиваться в автоматизированные системы предприятия (производства) и обеспечивать учет и сбор статистической информации с производственных участков и ОТК.

Основные недостатки данного способа проверки устройств — это необходимость изготовления специализированной оснастки и написание программного обеспечения, также функциональное тестирование, в отличие от периферийного сканирования, не дает точного указания на дефектные цепи и выводы компонентов. Но в большинстве случаев проведение этих работ оправдано за счет максимального покрытия и короткого времени тестирования.

Тестирование электронных устройств на производстве методом периферийного сканирования

Теперь мы рассмотрим следующую методику тестирования, которая позволяет контролировать качество монтажа и отбраковывать устройства ещё до стадии функционального тестирования. Это JTAG-тестирование.

Тесты для периферийного сканирования (boundary-scan) позволяют повысить качество разрабатываемых устройств и экономить затраты на этапе серийного производства. Основное преимущество этой технологии — возможность тестирования устройств c ограниченным доступом к выводам микросхем в корпусах BGA, COB и QFP.

В последнее время в связи с большим распространением стандарта JTAG и, соответственно, микросхем с его поддержкой, метод периферийного сканирования становится все более доступным.

Производители микросхем сопровождают свои продукты BSDL-файлами, в которых содержится информация об архитектуре регистров периферийного сканирования. Современные программные средства для JTAG-тестирования позволяют автоматизировать процесс, используя данные схематики из САПР. Все это упрощает подготовку и использование JTAG-тестирования.

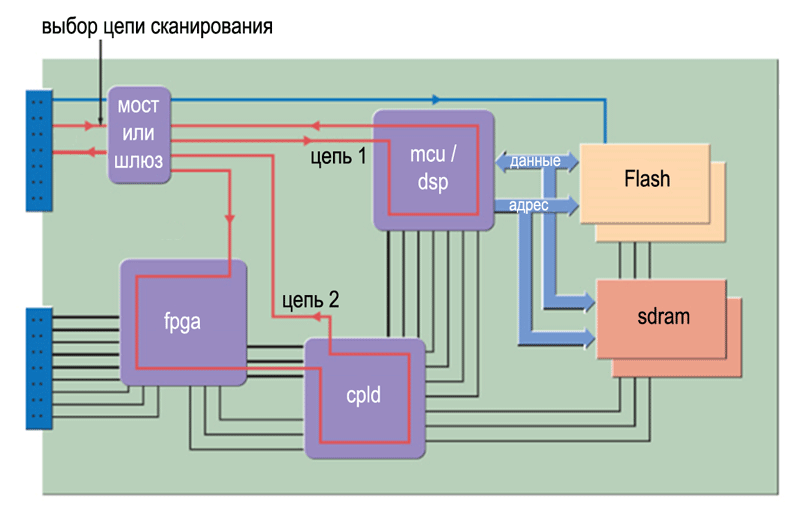

На схеме: Пример JTAG-тестирования. Тут видно, как можно проверить компоненты, которые подключены к шине тестируемой микросхемы, но напрямую не поддерживают стандарт JTAG (например, память flash и SDRAM).

При проектировании электронных устройств, требуется предварительная подготовка схемы изделия. Как минимум, это использование компонентов, поддерживающих стандарт IEEE 1149.1, правильное соединение этих компонентов, вывод JTAG-портов на внешние контакты или разъемы.

JTAG-тестирование позволяет выявить «непропай» ввыводах цифровых микросхем с разными типами корпусов, включая BGA, замыкания, обрывы, а также нерабочие микросхемы с цифровыми интерфейсами. Очень важно выявить все эти дефекты, так как если непроверенная плата переходит на этап программирования, могут возникнуть проблемы с запуском памяти и периферии. При этом будет сложно установить причину неполадок: неверные настройки ПО или дефект монтажа. JTAG-тестирование позволяет предупредить эту проблему.

Тем не менее, у JTAG-тестирования есть свои недостатки. Во-первых, это невысокая производительность по сравнению с функциональным тестированием. Во-вторых, метод предназначен для тестирования цифровой электроники, соответственно исключаются аналоговые части устройства. В третьих, важно учитывать, что JTAG-тестирование проверяет только целостность связей, но не их качество. Импеданс, паразитная емкость и т.д. — все эти качественные параметры могут существенно повлиять на работу высокоскоростных схем.

Также JTAG-тестирование имеет ряд других ограничений:

- Невозможно обнаружить дефекты монтажа, связанные с цифровыми или аналоговыми элементами, которые не имеют JTAG-поддержки, также недоступна диагностика дефектов связей между ними.

- Невозможно выполнить функциональные тесты или тесты, направленные на обнаружение неисправностей, которые являются той или иной функцией времени.

- Невозможно выполнить тесты, направленные на обнаружение таких дефектов шин данных, как, например, как дрожание фазы (jitter), паразитные связи (crosstalk), интерференция и т.д. (тесты для шины PCI).

Но в то же время JTAG-тестирование обладает серьезными преимуществами. Это глубокий анализ работоспособности микросхем и модулей для выборочной проверки электронных устройств в промышленной партии. Это важное дополнение, а в некоторых случаях — замена внутрисхемного тестирования с помощью «ложа гвоздей» или «летающих щупов». JTAG позволяет оптимизировать оборудование для полноценного тестирования либо сократить время на тестирование при комплексном подходе, когда оно используется совместно с другими методами.

Также по мере роста требований к миниатюризации электронных устройств JTAG-тестирование позволяет уменьшить габариты печатной платы, уйдя от необходимости размещать на ней группы контактных площадок для внутрисхемного тестирования с помощью «ложа гвоздей».

На фото: Внутрисхемное тестирование с помощью «ложа гвоздей». Источник: Spea.

Внутрисхемное тестирование

Хотя периферийное сканирование по технологии JTAG набирает все большую популярность, классический метод внутрисхемного тестирования, который начал развиваться с 70-х – 80-х годов 20 века, успешно применяется до сих пор.

Внутрисхемное тестирование — технология проверки отдельных компонентов на плате или фрагментов схем с использованием специального оборудования (ICT-станций) и оснастки (игольчатого адаптера). Благодаря этой методике тестирования можно анализировать отдельные компоненты и аналоговые части схем. А также успешно применять на крупносерийном производстве. Т.е. в тех случаях, когда другие современные технологии не справляются.

Условно внутрисхемное тестирование можно разделить на аналоговое и цифровое. При аналоговом внутрисхемном тестировании обычно проверяются следующие характеристики:

- наличие коротких замыканий и обрывов;

- номиналы дискретных компонентов (резисторов, конденсаторов, индуктивностей, дискретных полупроводниковых приборов);

- наличие и правильность установки микросхем.

Этот метод тестирования позволяет обнаружить большое количество дефектов сборки, поэтому аналоговое внутрисхемное тестирование часто называют анализом производственных дефектов.

При цифровом внутрисхемном тестировании цифровые микросхемы проверяются на соответствие таблице истинности.

Поскольку данная технология основана на физическом контакте иголок с контактами тестируемых компонентов, возникает ряд трудностей при реализации этого подхода в тестировании.

Постоянная миниатюризация компонентов приводит, в том числе, к уменьшению физических размеров контактных площадок и их перемещению их под корпус. Также в многослойных печатных платах значительное количество соединений реализовано во внутренних слоях. Все это приводит к необходимости вывода контактных площадок для ICT-адаптера на одну из сторон платы, что в свою очередь вызывает увеличение ее габаритов и усложняет их трассировку, а зачастую, в случае высокочастотных шин, это невозможно в принципе.

Один из вариантов решения этих проблем является использование метода тестирования «летающими щупами» или «летающими матрицами». Этот подход позволяет уйти от необходимости вывода специальных контактных площадок для тестирования, но значительно увеличивает время проверки, что является существенным ограничением для серийного производства.

На фото: еще один пример тестирования печатной платы «летающими щупами». Источник: Acculogic.

Другой и, наверное, основной способ оптимизации технологии внутрисхемного тестирования без ущерба к плотности покрытия тестами печатной платы и ко времени тестирования — комплексный подход, который заключается в совмещении классического ICT-тестирования с JTAG-тестированием. Такой подход, при предварительном расчете покрытия печатной платы тестами и распределении их между JTAG и ICT, позволяет минимизировать число площадок для иголок ICT и, соответственно, упростить и удешевить тестопригодную плату. Применение таких методов требует соответствующего подхода при проектировании электронного устройства, анализа тестопригодности электрических схем, их корректировки.

Принтскрин: пример отчета о покрытии тестами. Источник: Acculogic.

Выводы

Таким образом, мы можем сформировать основные критерии, которые определяют выбор методики тестирования:

- Масштабность производства.

- Сложность продукта.

- Наличие особых требований к качеству (пример: электроника ответственного применения).

Так, например, для сравнительно простых устройств в малых партиях достаточно использовать функциональное тестирование, а для простой электроники в крупных сериях — внутрисхемное тестирование, т.к. оно обеспечивает максимальную скорость. Для тестирования цифровой электроники с поддержкой технологии JTAG оптимальным выбором будет периферийное сканирование, оно позволяет отладить процесс производства и скорректировать его на ранних этапах.

При планировании массового производства необходимо учитывать производительность всех методов тестирования, и, соответственно, такое их сочетание, чтобы получить минимальное время на тестирование одного устройства при максимальном покрытии тестами. Например, во многих случаях тестирование с помощью «ложа гвоздей» и периферийное сканирование, являются предпочтительными методами по сравнению с функциональным тестированием и тестированием «летающими щупами» с точки зрения скоростных характеристик.

Соответственно, именно комплексное тестирование, т.е. совмещение различных технологий в грамотной пропорции сегодня является оптимальным вариантом для проверки и анализа качества электроники на производстве. По этой причине на первый план выходит предпроектный анализ тестопригодности и покрытия тестами. Он позволяет изначально спланировать и обосновать применимость и степень использования описанных выше подходов в каждом конкретном проекте.

[!?] Вопросы и комментарии приветствуются. На них будет отвечать автор статьи Алексей Фридрих, инженер по сопровождению производства дизайн-центра электроники Promwad.

Автор: Promwad