В современных условиях инженеру-проектировщику необходимо постоянно получать новые знания, чтобы быть востребованным на рынке труда. Часто получать новую информацию приходится, так сказать, “без отрыва от производства”: в ходе работы над проектом, в поездках на работу и т.п. Современный цифровой мир это позволяет, было бы желание. Однако, иногда качество получаемых знаний может страдать. Информация усваивается человеком поверхностно или даже в искаженном виде.

Общаясь с трассировщиками ПП, работающими в САПР печатных плат Cadence OrCAD/Allegro, я иногда замечал, что люди не придают большого значения цветовой индикации полей в редакторе правил Constraint Manager. А именно: пользователи не обращают внимания на то, что некоторые колонки раскрашены в желтый цвет.

На самом деле желтый цвет в редакторе правил Cadence означает, что данная проверка не может быть проведена по какой-либо причине. Причины могут быть разными:

- Проверка отключена пользователем.

- Проводящая дорожка либо не проложена вовсе, либо не доведена до конца.

- Иные причины.

В большинстве случаев не возникает фатальных ситуаций, при которых появляются ошибки, приводящие к неработоспособности ПП. Поскольку OrCAD PCB Editor обладает многоступенчатым механизмом проверок проекта на DRC, просто так, одним движением их не отключить. Однако иногда из-за досадного пробела в знаниях, или же из-за невнимательности, создаются ситуации, приводящие к возникновению некорректных ситуаций в проекте. Например, один разработчик рассказал мне, как случайно отключил проверку на закорачивание разноименных линий друг с другом. Причем, САПР ПП не будет в этой ситуации сообщать об ошибке, поскольку проверка отключена пользователем.

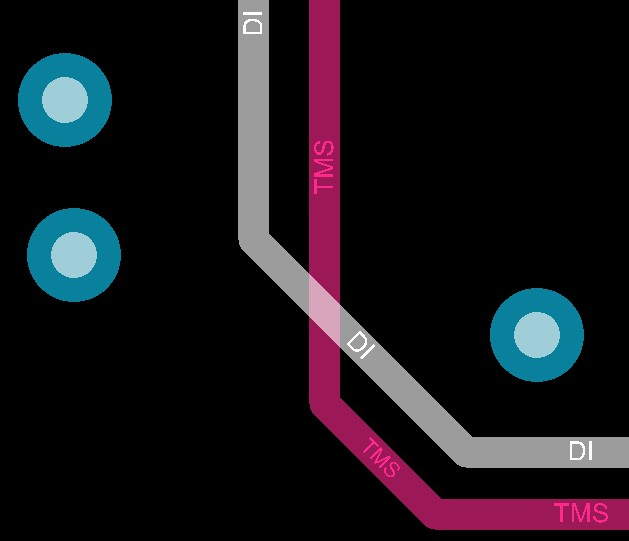

Пересечение одного проводника другим без появления сообщения об ошибке

На приведенном рисунке видно, что проводники разноименных линий пересекаются друг с другом. Однако сообщения об ошибке не возникает. Причина данного поведения программы разработчику не ясна, поскольку при онлайн-трассировке все зазоры, заданные в менеджере констант, сохраняются и поддерживаются.

Зазоры и правила в регионах поддерживаются при трассировке

Отсутствие маркера DRC кроется как раз в настройках Constraint Manager.

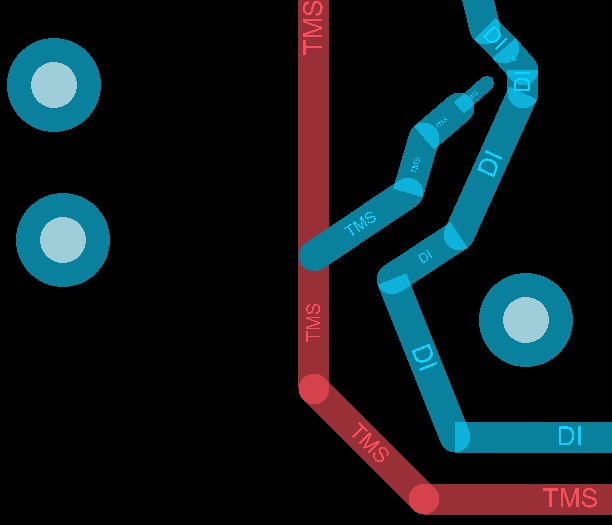

Так выглядит отключенная проверка в Constraint Manager

Желтый цвет в разделе проверок зазоров Line-to-Line означает, что проверка не проводится (или не может быть проведена). Из-за этого маркер DRC и не возникает. Конечно, частичное отключение проверок иногда очень удобно и позволяет сократить общее время проверки проекта, но …. Это может привести к фатальным последствиям, если при сдаче проекта и генерации файлов для производства разработчик не включит все необходимые проверки и не проведет с ними финальную DRC-проверку.

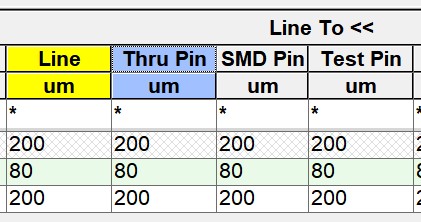

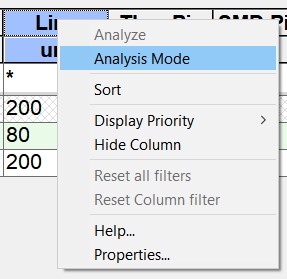

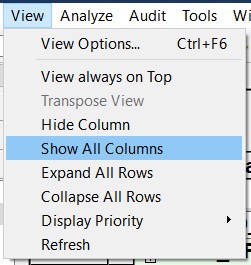

Отключить или включить определенную проверку в Cadence очень просто: достаточно кликнуть на шапке интересующей ячейки и выбрать из выпадающего меню Analysis Mode.

Быстрое включение или отключение определенного вида проверок

При включенной проверке цвет шапки серый, при отключенной проверке цвет шапки желтый.

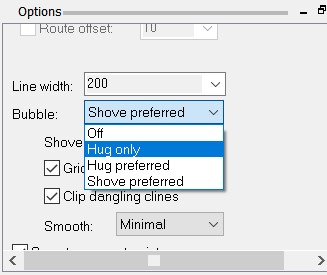

Почему же при отключенной проверке в Constraint Manager при трассировке все-таки поддерживаются необходимые зазоры и OrCAD PCB Designer не дает пользователю нечаянно совершить ошибку? Это происходит как раз из-за того, что система проверок DRC состоит как бы из двух частей: проверки в режиме реального времени Online DRC, и проверки по требованию Batch Mode DRC. Batch Mode DRC как раз и отключается принудительно в Constraint Manager. Online DRC продолжает работать, если в режиме трассировки значение параметра Bubble в окне Options отлично от состояния OFF.

Возможные значения, которые может принимать параметр Bubble

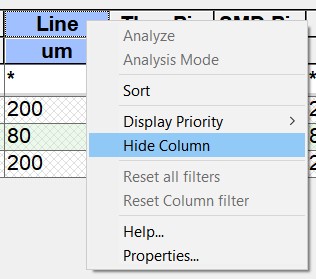

Если инженер не хочет видеть отключенные проверки или же какие-то разделы в редакторе правил Constraint Manager, то их можно легко скрыть.

Скрытие колонки или раздела из рассмотрения

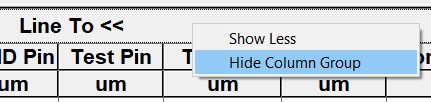

Когда проверка снова станет необходима, ее можно вернуть в поле отображаемых колонок.

Возвращение скрытых колонок

Хочется отметить, что табличный редактор правил САПР Cadence Allegro / OrCAD, при всей своей мощи, очень удобен и прост в настройках, а сами проверки выполняются довольно быстро, поэтому зачастую нет нужды что-то принудительно отключать.

С другой стороны, если уж потребовалось отключить какие-то особенно медленные проверки, разработчик может сначала сохранить «технологический» файл, содержащий настройки всех необходимых проверок, потом отключить их временно, а при выпуске конструкторской документации после завершения трассировки – вновь подгрузить тот технологический файл со всеми проверками и запустить окончательный DRC.

Да, кстати, если вспомнить о том разработчике, который отключил проверку на КЗ между цепями – к счастью, производитель печатных плат при запуске заказа обратил его внимание на проблему замыкания между цепями, так что им удалось избежать финансовых и временных потерь. Но, по опыту работы в компании, которая занималась изготовлением печатных плат, могу сказать, что проблема отключения «лишних» проверок встречалась очень часто, у большинства клиентов, и не зависела от того, в каких САПР работают разработчики. Так что не забывайте их включать в нужный момент!

Автор: PCBgeek