Пришло время заключительной статьи из цикла на тему разработки сложных плат на процессорах. Я постарался наиболее подробно описать процесс, стараясь как можно доступнее структурировать материал.

По просьбе Indemsys немного расширю эту статью и кратко расскажу о трассировке различных интерфейсов. Спасибо за замечание, почитываю Ваши статьи.

Приглашаем 10 октября на Selectel Tech Day

Приглашаем 10 октября на Selectel Tech Day

Расскажем о новинках на рынке и обновлениях в наших продуктах. Вас ждут доклады, нетворкинг, мастер-классы и вечерняя программа. Участие бесплатное, но нужно зарегистрироваться.

Используйте навигацию, если не хотите читать текст полностью:

→ Задание на расчет импедансов. Получение рабочего стека

→ Процесс выравнивания дифференциальных пар

→ Экранирование определенных сигналов

→ Мультипликация платы для производства

Задание на расчет импедансов. Получение рабочего стека

Как я уже писал ранее, для корректной работы интерфейсов без подсчета волновых сопротивлений не обойтись. Это касается высокоскоростных шин данных (в том числе оперативной памяти). Чем длиннее трасса и чем больше переходных отверстий на пути прохождения сигнала, тем сильнее это сказывается на его целостности. При значительном ухудшении параметров сигналов характер и проявление могут быть разными. Если говорить о видео-интерфейсах, то это появление артефактов на изображении, чаще всего в виде зашумленности на краях экрана, образование цветных пикселей и полос на изображении и т. д. Реже — срывы изображения. Для MIPI DSI/CSI проявление может быть более фатальным, вплоть до полной неработоспособности (из-за особенностей работы с этими интерфейсами). Для SDIO и USB характерны потери данных и обрыв связи. Для I2S — это артефакты записи и воспроизведения звука. При рассогласовании линий оперативной памяти (особенно это касается DDR3 и выше) появляется очень высокая вероятность получить неработоспособную или же работающую с постоянными сбоями плату, что бывает очень сложно отследить, а тем более исправить без переразводки.

На завод по производству печатных плат обычно передаются только гербера (я не считаю бланк заказа, так как там только общая информация по плате). Если вам необходимо выполнить контроль импедансов, то нужно будет подготовить соответствующий документ. Инженер, проверяющий плату, ничего не знает о микросхемах, которые вы установили, и может лишь косвенно догадаться, где проложена шина данных, линия сброса или же полигон питания (в данном случае неотличимый от GND). Да ему это и не нужно.

Я пользовался тремя способами подготовки задания. Расскажу обо всех, начиная с худшего и сложного, заканчивая правильным. На производстве инженеру необходима информация о проводниках, волновое сопротивление которых нужно контролировать, опорных слоях, относительно которых делается контроль, и непосредственно сами импедансы.

В первый раз у меня была простая плата на шести слоях. Я сделал примерно так.

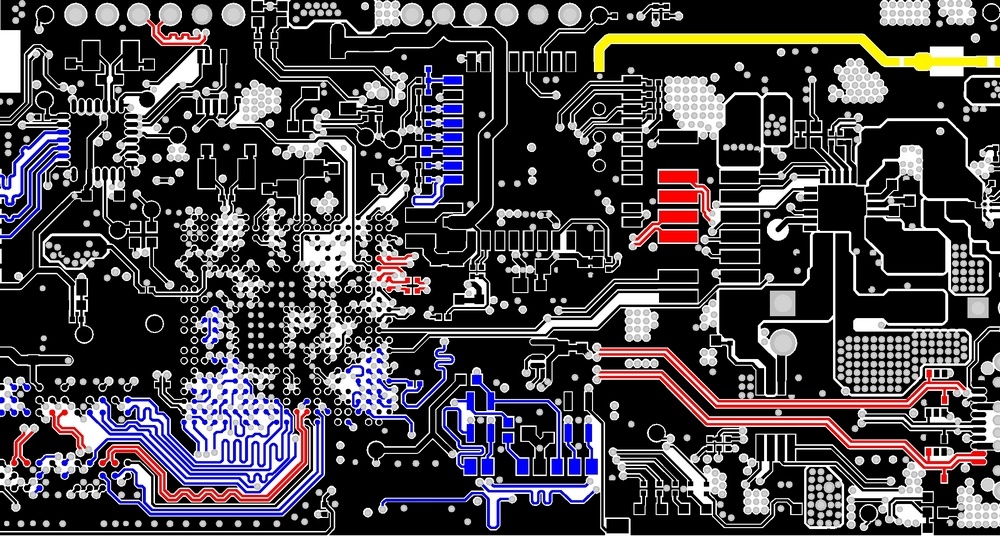

Выделение цветом необходимых проводников.

У меня получилось четыре картинки с выделенными разными цветами проводниками в зависимости от волнового сопротивления. Дальше я сделал таблицу, в которой указал цвет, волновое сопротивление и опорный слой. Это довольно трудоемко, можно пропустить критичный проводник, а инженеру нужно выискивать на герберах по картинкам необходимые линии и тоже не ошибиться.

Второй способ — создание в проекте отдельных информационных слоев, на которых будут нанесены необходимые проводники.

Отдельный слой для контролируемых проводников.

То есть создаем слой, например Bottom_Mech, и копируем туда проводники. Altium 14 позволял просто выделять проводники и переносить их на любой слой. Дальше прямо тут можно указать волновое сопротивление и сделать любые другие пометки, например какой слой считать опорным, если контролируемые проводники находятся в середине стека. Процесс тоже трудоемкий и остается высокая вероятность ошибки.

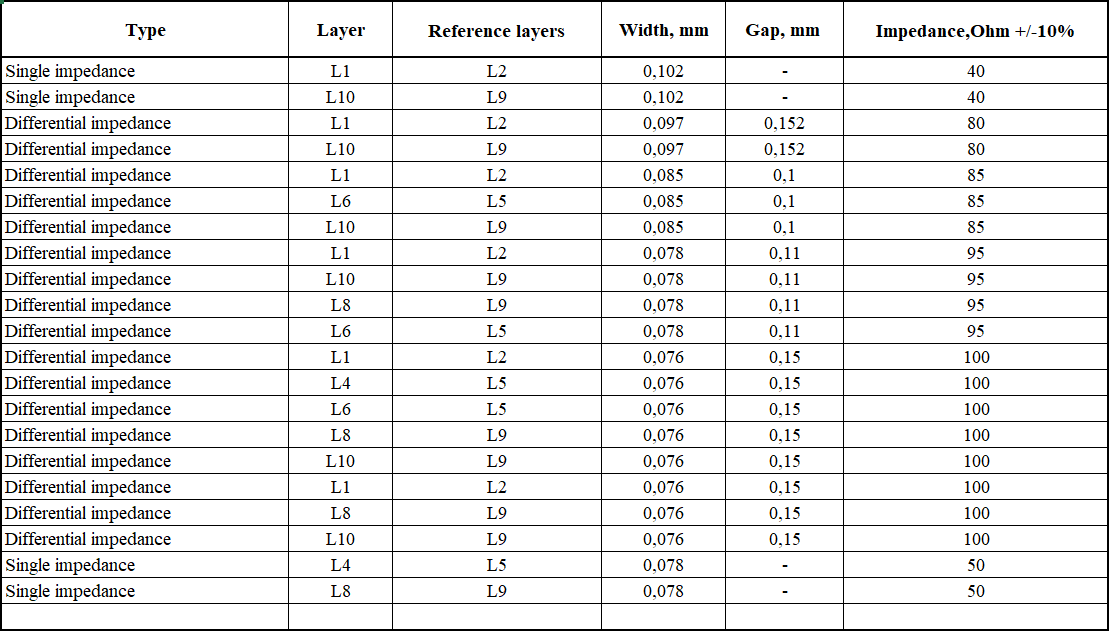

Третий способ. Создается таблица интерфейсов и волновых сопротивлений.

Таблица задания импедансов.

- Тип проводника, одиночный или пара.

- Слой, в котором расположен проводник.

- Опорный слой для проводника.

- Ширина проводника.

- Зазор между проводниками, если это диффпара.

- Необходимое волновое сопротивление.

На производстве мне порекомендовали использовать различные ширины проводников для разных импедансов. Это существенно упрощает задачу инженера. В ответ приходит похожая таблица, в которой указаны волновые сопротивления, получившиеся на плате с учетом используемых материалов и толщины меди. Если все устраивает, то высылается стек предполагаемой платы.

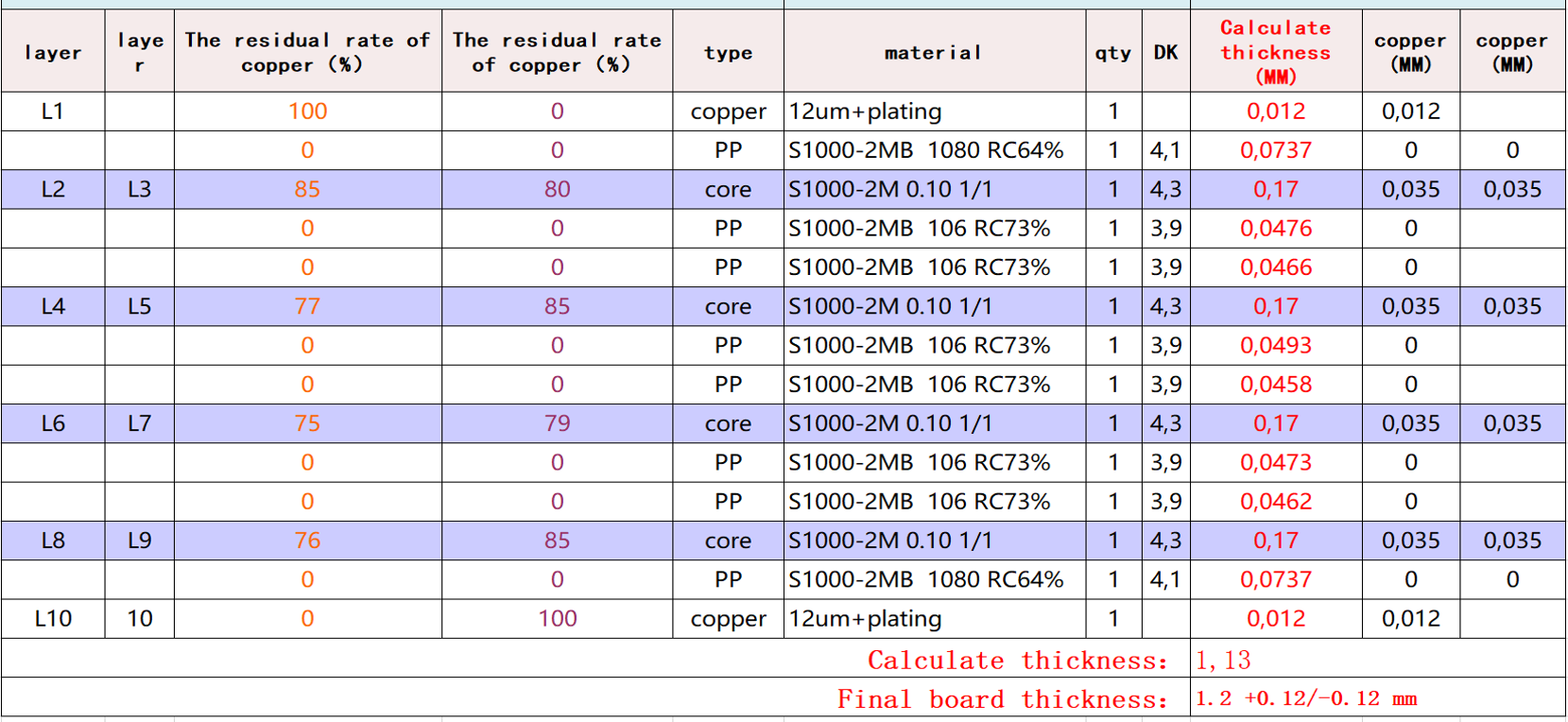

Стек платы на десять слоев.

Тут можно посмотреть диэлектрическую проницаемость и названия материалов, толщины слоев и итоговую толщину платы.

Процесс выравнивания дифференциальных пар

Как я писал ранее, на этой стадии проектирования печатной платы нужно учесть одну особенность. Для корректировки длин понадобится дополнительное место на плате. С учетом того, что трассы групп дифференциальных пар имеют существенную ширину, места может понадобиться много. Если (до выравнивания) вдоль всей трассы будут плотно установлены компоненты и переходные отверстия, то с корректировкой длин могут возникнуть сложности. Ниже я привел пример, когда в процессе проектирования оставлены места для выравнивания.

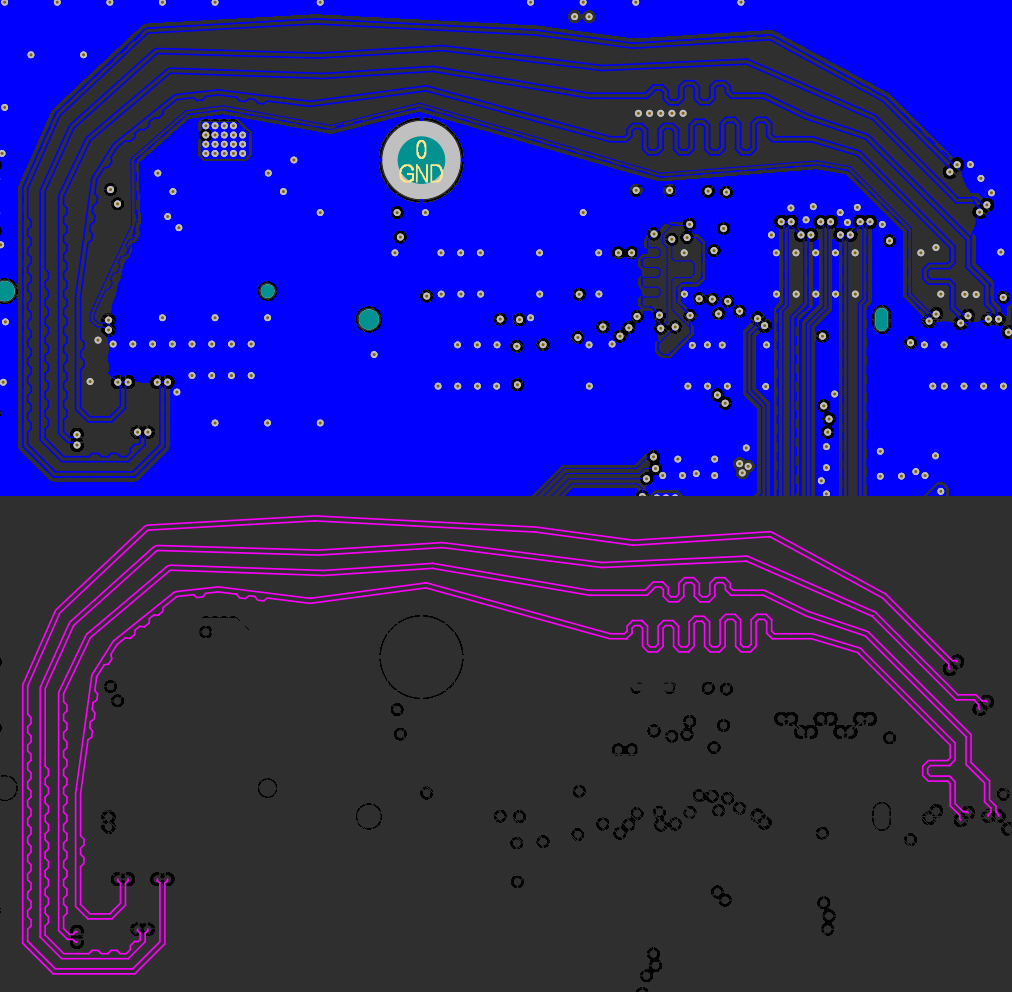

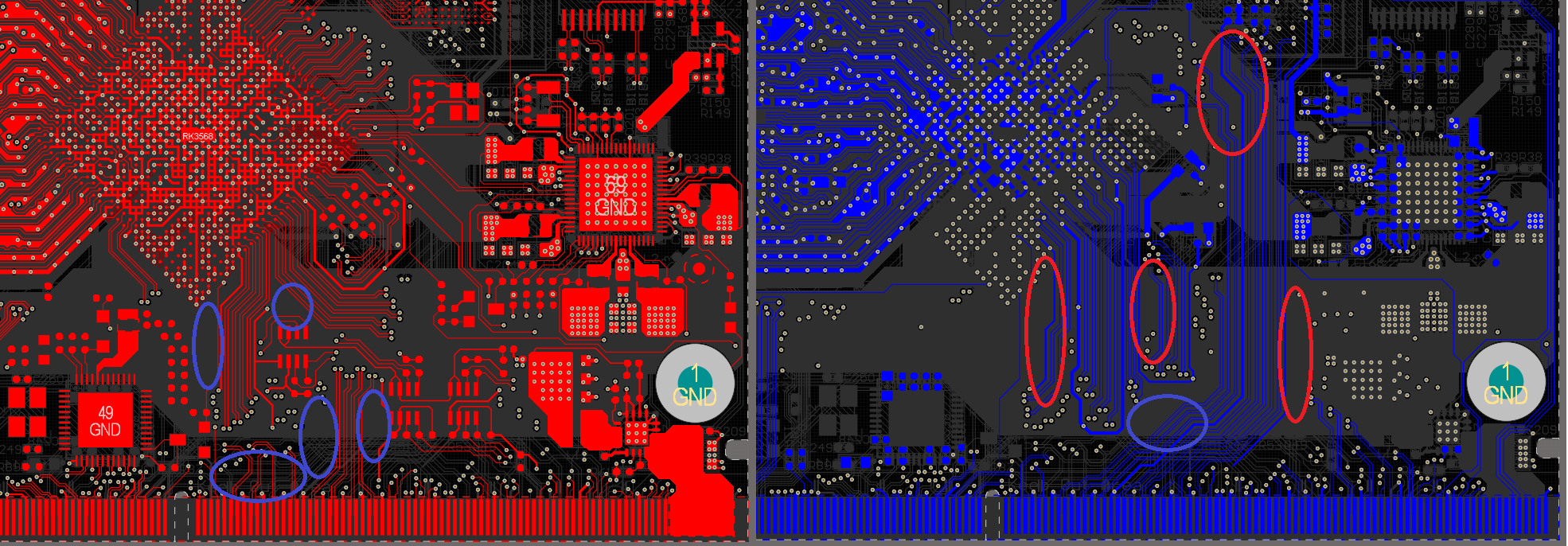

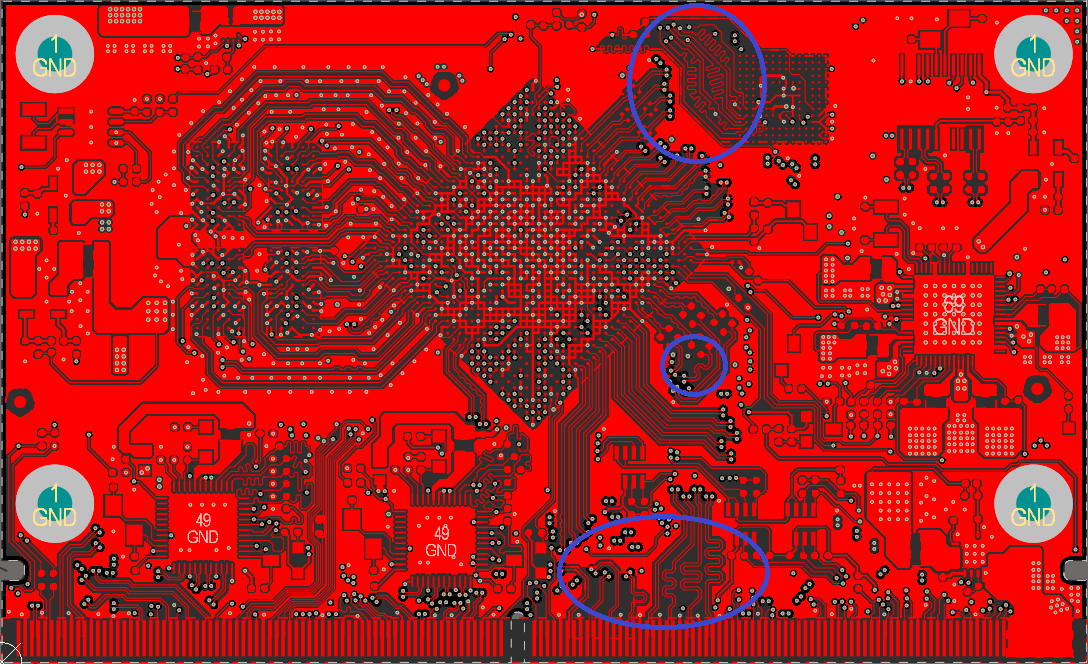

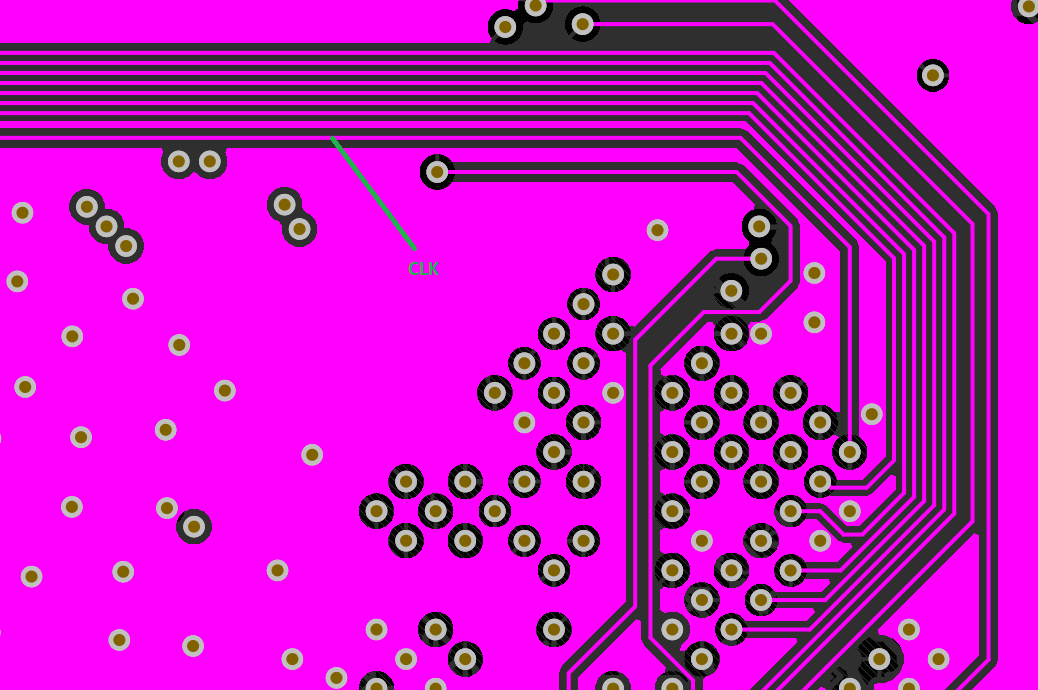

Зоны для выравнивания длин проводников.

Если монтаж плотный, придется делать выравнивание до конечной расстановки компонентов. То есть необходимо заранее (во вкладке PCB) посмотреть, на сколько примерно придется корректировать длины и какую площадь это займет.

Использование зон для выравнивания проводников.

На рисунке выше видно, что в итоге задействованы не все зоны, так как некоторые интерфейсы выравнены в других слоях. Непосредственно выравнивание выполняется с помощью инструмента «Accordion» (с параметрами из прошлой статьи). Стоит помнить: чтобы исключить взаимное влияние проводников (либо групп проводников) друг на друга, необходимо выполнять условие минимального зазора (не менее 0,254 мм). Оптимальным будет прокладывание полигона земли между различными интерфейсами.

Экранирование определенных сигналов

Отдельно хочу отметить, что существуют одиночные проводники и группы сигналов, которые необходимо экранировать друг от друга. Это достигается путем увеличения зазора, либо прокладыванием полигона земли. Для примера можно рассмотреть такие интерфейсы, как SDIO и I2S. Эти (и многие другие) интерфейсы включают в себя сигналы клоков.

Критичным является как влияние клока на соседние линии данных, так и возможная порча сигнала в результате воздействия на него других элементов топологии печатной платы.

Думаю, вы встречали экранирование кварцевого резонатора и его сигналов полигоном земли. Сильная помеха на эти проводники может вызвать срыв синхронизации и зависание микроконтроллера/процессора.

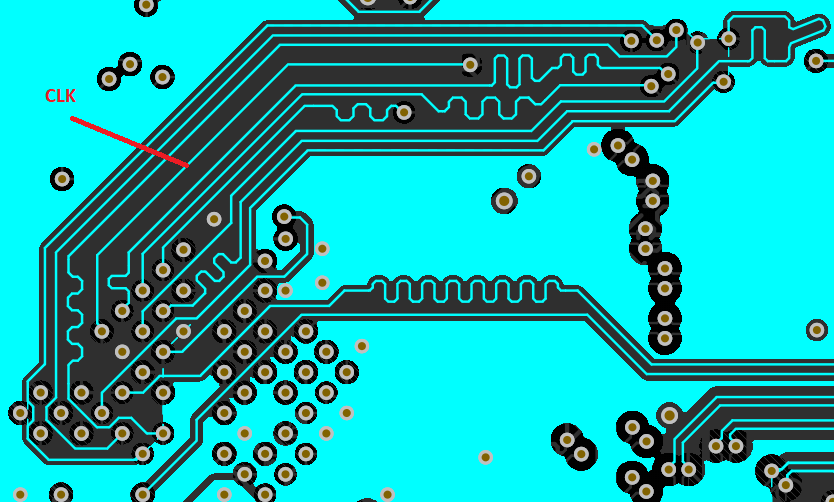

Экранирование SDMMC_CLK.

На картинке выше видно, что для линии SDMMC_CLK используется больший зазор, чем для других проводников SDIO интерфейса. В данном случае это поможет избежать помех на линии данных, которые проложены рядом.

Экранирование AUDIO_MCK.

Клоки AUDIO_MCK я отделил землей от остальной шины данных интерфейса I2S и других сигналов. В крайнем случае, если по-другому сделать не получается, клоки можно экранировать «медленным» GPIO, например, индикационного светодиода, либо проводником (или полигоном) питания.

Влиянию помех также подвержены аналоговые линии данных. Категорически запрещено трассировать аналоговые линии в непосредственной близости от «шумящих» проводников. Это относится и к соседним слоям печатной платы. Не стоит забывать об излучающих помехи компонентах, таких как катушки индуктивности, трансформаторы, ШИМ-контроллеры, шины мощных ключевых транзисторов, кварцевые генераторы и т. д.

Стоит помнить, что последствия влияния одних проводников на другие могут быть различными. Если линию сброса процессора (микроконтроллера) провести в непосредственной близости от линии PWM либо катушки индуктивности DC/DC преобразователя, то можно получить периодически перезагружающееся устройство.

Рекомендую увеличивать зазоры между проводниками для таких интерфейсов, как SPI, I2C, UART, SDIO, I2S. Например, для I2C и UART я делаю зазор >2W (где W — ширина проводника), а если позволяет место, прокладываю между проводниками землю.

Расстояние между двумя проводниками — это не только расстояние между линиями данных, но и между переходными отверстиями, образованными сменой слоя.

Мультипликация платы для производства

Решил вынести эту тему отдельным пунктом, так как тут тоже есть свои нюансы. Для начала необходимо разобраться, что такое мультипликация (панелизация) плат и для чего она нужна, а потом уже перейдем к основным требованиям при ее создании.

Мультиплицирование или панелизация — это объединение нескольких печатных плат в одну заготовку с разделением на отдельные элементы (платы) путем скрайбирования или фрезеровки. Независимо от выбранного типа разделения панель остается единым целым. Не редко можно встретить совмещение фрезеровки и скрайбирования на одной панели.

Фрезеровка — это разделение печатных плат путем обработки контура платы фрезой с оставленными перемычками для обеспечения жесткости панели. После установки компонентов платы разъединяются, а перемычки удаляются. Обычно используются фрезы диаметром один или два миллиметра.

При фрезеровке завод-изготовитель печатных плат устанавливает перемычки между платами либо на свое усмотрение, либо по Вашим требованиям. Важно знать, что при установке компонентов на производстве может потребоваться указать места этих перемычек. Это можно сделать, запросив «рабочие гербера» у производителя печатных плат.

Радиусы внутренних скруглений контура на печатной плате не могут быть меньше радиуса фрезы.

Скрайбирование — это разделение печатных плат путем нанесения линейных разрезов V-образной формы с обеих сторон заготовки. Обычно используют фрезы с углом 30 градусов.

Скрайбирование производится по всей длине (ширине) заготовки под углом 90 градусов. Логично применять только для одинаковых плат.

Панелизация применяется, во-первых, для возможности «захвата» печатной платы станком — сборочно-монтажного производства. Во-вторых, для увеличения эффективности сборки печатных плат. Размеры самой заготовки и технологических полей для «захвата» лучше всего согласовывать с установщиком компонентов.

Если на одной панели разместить разные платы, то могут возникнуть проблемы с автоматизированной установкой компонентов, так как элементы с одними и теми же позиционными обозначениями будут разными. Например, R1 на первой плате 10 кОм, на второй плате 1 МОм.

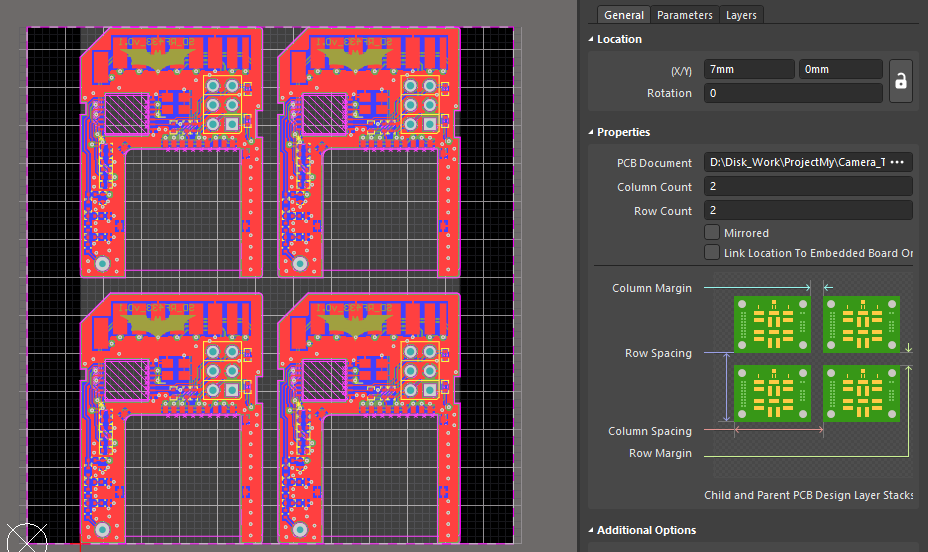

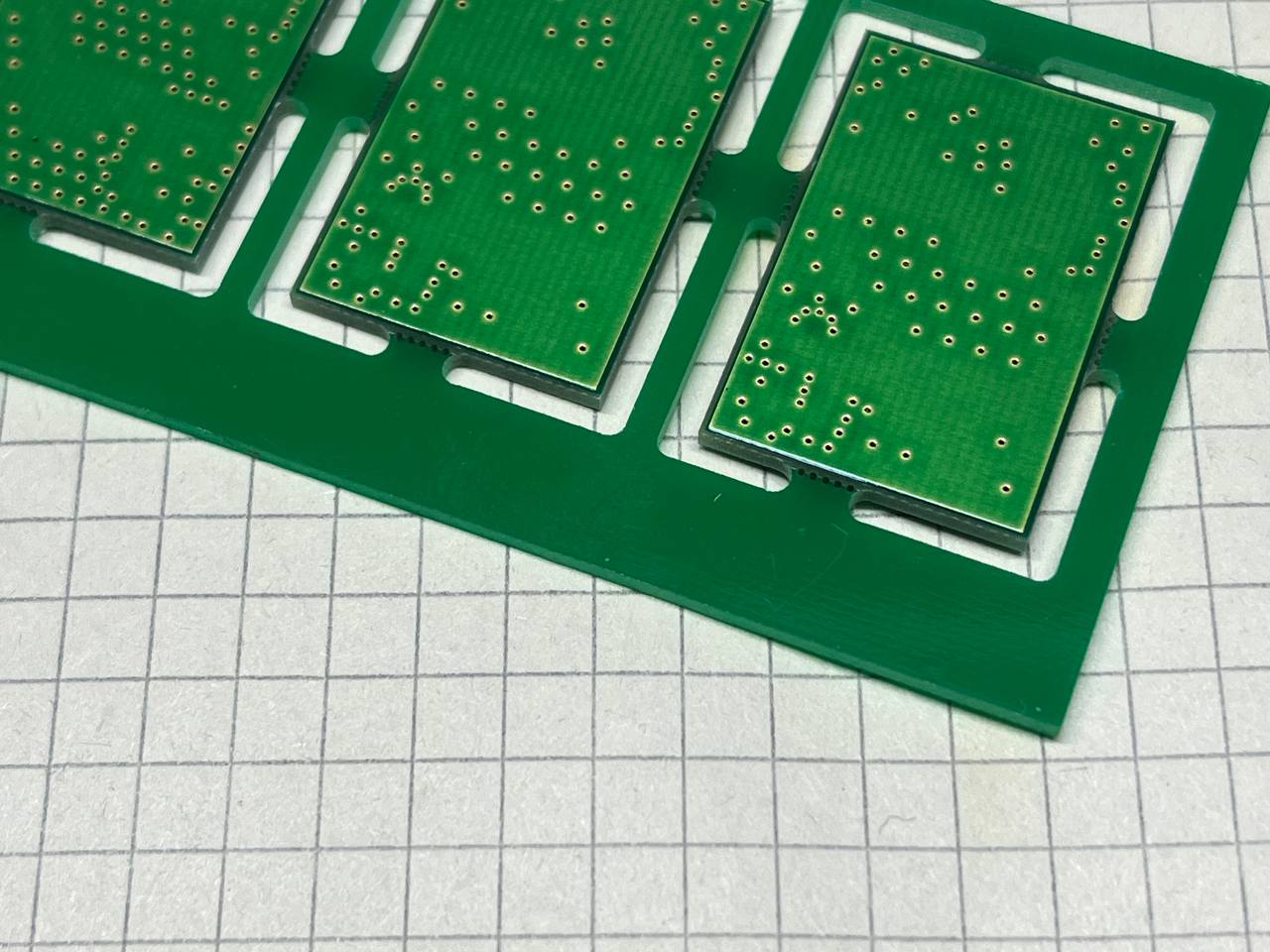

Ниже приведен пример панели из четырех плат, с технологическими полями семь миллиметров c фрезеровкой контура. Мультипликация выполняется в отдельном файле pcb с использованием инструмента «Board Array».

Заготовка мультипликации из четырех плат.

Ниже показано, как отличаются методы разделения плат в заготовке. Слева-направо: скрайбирование, фрезеровка, совмещение методов.

Методы разделения плат в заготовке.

При выборе метода разделения плат необходимо руководствоваться несколькими принципами. Совмещенный метод используется, если на плате присутствуют скругления контура. При этом можно использовать фрезеровку, но будут оставаться перемычки, которые необходимо удалять. Если сделать зазор между платами в три диаметра фрезы, то удаление не потребуется, но расход текстолита будет больше.

Перемычки с технологическим зазором.

Наиболее удобным является метод скрайбирования, но в этом случае нужно учитывать, что отступ металлизации от края платы должен быть больше, чем при фрезеровке. Обычно составляет не менее 0,4 мм. Также скрайбирование не может проходить по металлизации платы. Если Вам необходимо сделать металлизированные краевые полу-отверстия, то обработка производится только методом фрезеровки.

При создании мультизаготовки необходимо учитывать, что компоненты, установленные на краях платы, могут помешать разделению плат. Также нужно помнить, что технологические поля должны оставаться пустыми (не должно быть нависающих компонентов) либо быть достаточно широкими.

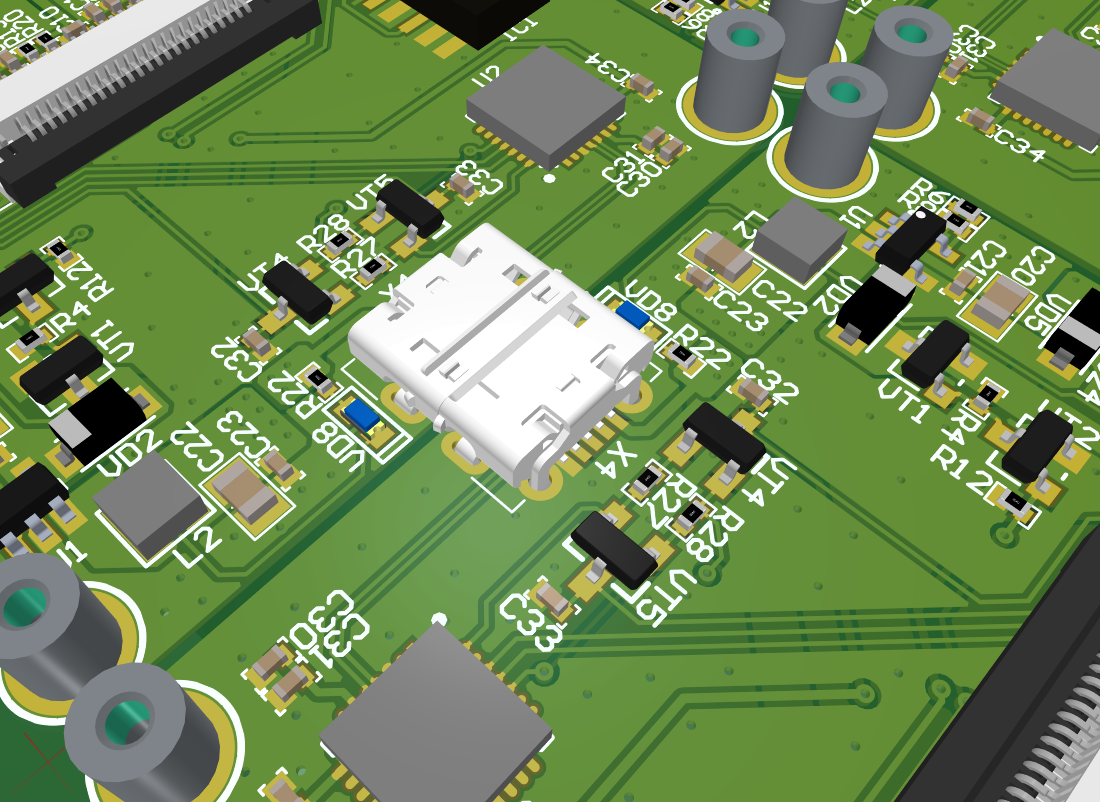

Ниже приведен пример того, как два разъема microUSB мешают установке. Если со всех сторон платы похожая ситуация, то нужно предусмотреть пустые поля между платами и желательно применять фрезеровку контура. В противном случае (при использовании скрайбирования) в процессе разделения плат есть высокая вероятность повреждения данных компонентов.

Разъемы мешают друг другу при установке.

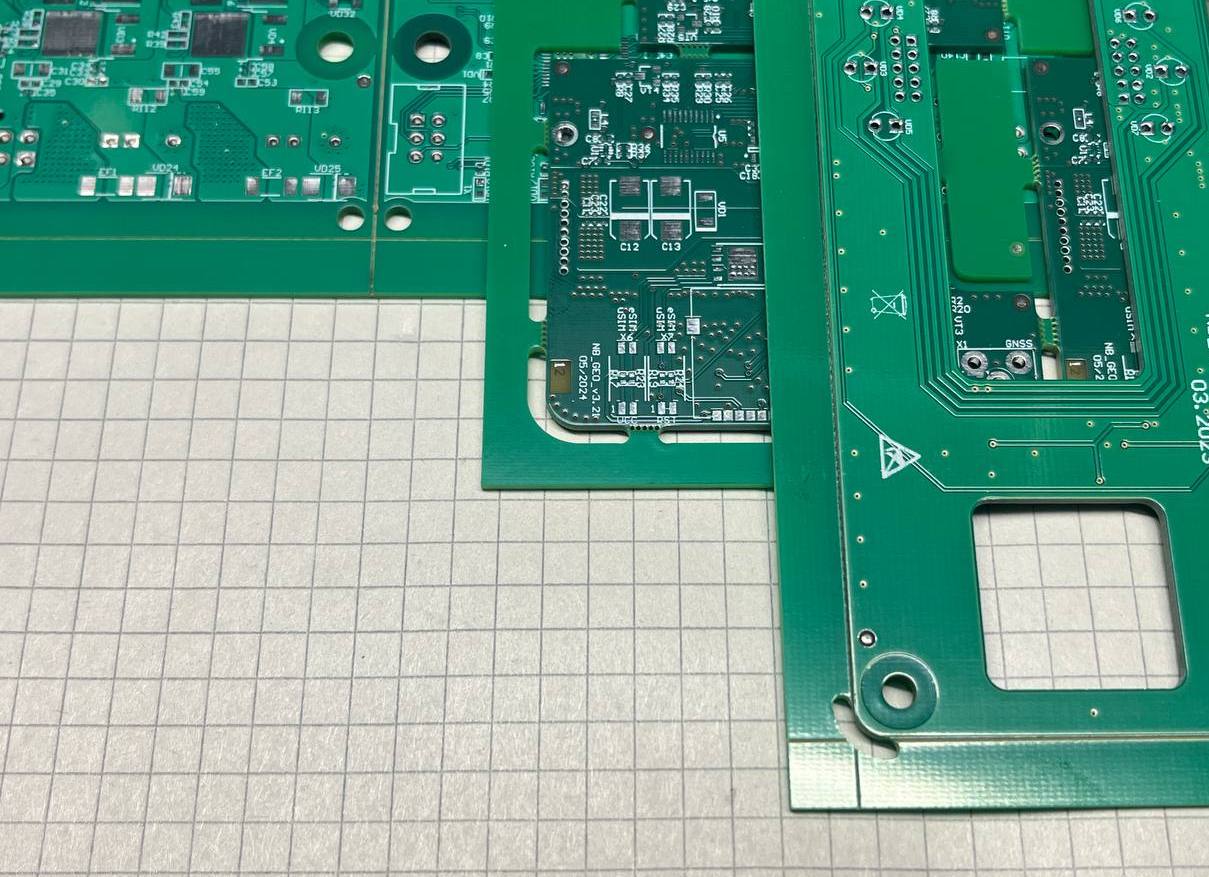

Особое внимание следует уделить платам с боковыми контактами, как у SMARC. Для изготовления групповой заготовки мне пришлось расположить платы встречно, так как краевой разъем имеет определенную механическую обработку. При обычном скрайбировании после разделения плат может оставаться ворс от волокон текстолита, что недопустимо для модулей такого типа. Фрезеровка же не подходит, так как на плате должна быть снята фаска. Когда с производства придут печатные платы я обязательно добавлю фотографию.

P.S: На всякий случай ссылки на предыдущие статьи оставлю здесь:

- Разработка сложных процессорных систем на примере модуля SMARC

- Разработка сложных процессорных систем на примере модуля SMARC. Продолжение

Надеюсь, цикл статей вам понравился. Спасибо за внимание и успехов!

Автор: the_bat