Несколько дней назад Intel объявила о том, что производственные проблемы (недостаточный выход годных) вынудили ее сместить старт коммерческого производства на проектных нормах 10 нм с конца этого года на начало следующего. А TSMC уже начали серийное производство 7 нм, с пятью десятками проектов в этом году. Это одна сторона медали.

Другая сторона — вчерашний перевод статьи о школьнике из США, который сделал то, что не удалось BarsMonster, и в гараже произвел микросхему. С проектными нормами 175 микрон!

В комментариях к этому переводу было некоторое количество вопросов “когда уже можно будет купить опенсорсный процессор?”, “когда появятся 3D-принтеры для микросхем?”, и я решил немного осветить вопрос того, что происходит с проектными нормами между 10 нм и 175 мкм, в том числе применительно к их доступности для любителей и маленьких компаний.

Спойлер: ASIC для майнинга — это неподъемно дорого (десятки миллионов долларов).

Производится ли что-то вообще по устаревшим проектным нормам?

Что такое вообще проектные нормы? В классическом понимании фраза “проектные нормы Х нанометров” означала, что длина затвора транзистора составляет эти самые Х нанометров. Начиная с какого-то момента (ниже 20 нм) уменьшение размеров транзисторов (известное также, как закон Мура) перестало работать, пришлось изобретать разные ухищрения (например FinFET), но маркетологи были неумолимы: заветную цифру надо двигать дальше вниз. Поэтому в современных 10 нм процессах актуальная длина канала — все те же 20 нм. Но важнее то, что первые десятилетия своего существования закон Мура двигал полупроводниковую отрасль вперед не только потому, что меньше — круче, но и потому, что каждый транзистор в следующем поколении проектных норм был дешевле, чем в предыдущем. То есть, за те же деньги на кристалле того же размера было можно поместить больше функционала. Но и это закончилось, и 28 нм были проектными нормами с самым дешевым транзистором, после них транзисторы стали дорожать. Это, в свою очередь, привело к тому, что для многих применений переходить на передовые проектные нормы стало экономически невыгодным. И это касается отраслей, где маленькие проектные нормы традиционно широко использовались, а ведь есть еще и применения, где они и так не были нужны.

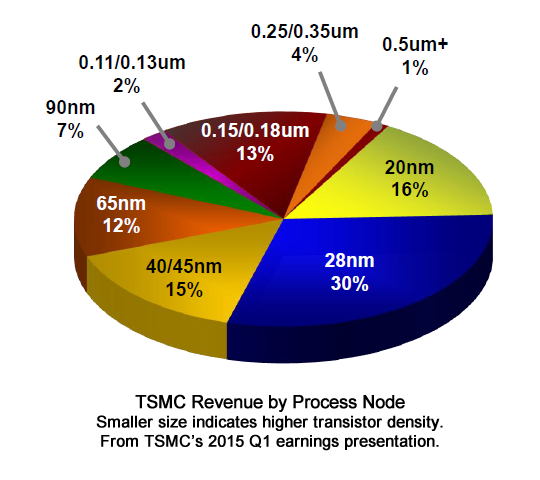

Давайте посмотрим на срез продаж крупнейшей в мире фабрики TSMC (около половины всего рынка). Сверху один из кварталов 2015 года, снизу — 2009.

Что мы видим на этих графиках? То, что и в 2009, и в 2015 году две самые тонкие проектные нормы приносили TSMC только половину всей выручки, и что 15-20 процентов приносят технологии как минимум десятилетней давности! На графике 2009 года есть 4% от 40 нм, но ими мы для простоты пренебрежем, потому что это были первые недели после запуска технологии.

Еще из этих графиков можно заметить, что за семь лет доля техпроцесса 130/110 нм сократилась в восемь раз, 90 нм — в пять раз, а 65 нм и 180/150 нм — только в два раза. Особенно хорошо это видно на графике 2015 года — сектора с ростом проектных норм сужаются, сужаются, а потом идет один широкий сектор.

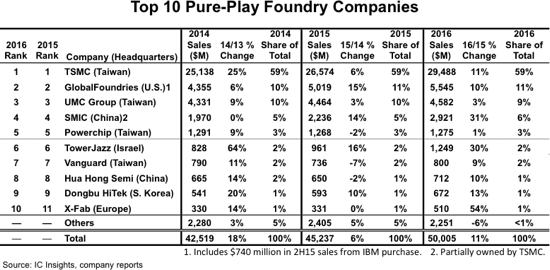

Замечу, что мы сейчас говорим о десяти процентах выручки крупнейшей фабрики в мире, а это больше, чем вся выручка фабрики, занимающей четвертое место, и в восемь раз больше такого уважаемого на рынке игрока, как немецкий XFAB (у которого, кстати, в принципе нет технологий ниже 130 нм). Во сколько раз это больше, чем у зеленоградского “Микрона”, тоже имеющего проектные нормы 180 нм, я даже думать боюсь.

При этом рынок растет, и производства по старым проектным нормам это тоже касается. Более того, в строй даже вводятся новые фабрики, работающие с «устаревшими» пластинами 200 мм.

Почему так? Для того, чтобы ответить на этот вопрос, давайте сходим на сайт TSMC, в раздел “технологии”.

Там мы увидим три подраздела: “планы”, “логические технологии” и “специальные технологии”. С планами все понятно, в разделе логики мы увидим ряд, отсортированный по проектным нормам, а вот в разделе “специальные технологии”… проектные нормы не упоминаются вообще! Подразделы отсортированы по применениям, и именно в этой части и собраны заказы на микросхемы по самым разным проектным нормам. Например, описание раздела технологий для аналоговых схем:

“The Company's comprehensive analog process portfolio offers options from 0.5µm to 16nm for applications including smartphones, tablets, automotive electronics, computers, audio, electronic medical equipment and home appliances.”

Вдумайтесь! В 2018 году крупнейшая в мире фабрика, законодатель и первопроходец, рутинно рекламирует производство по 500 нм. Почему? Потому что это экономически выгодно.

Стоимость производства интегральной микросхемы удваивается с каждым новым шагом проектных норм, и разница между 28 нм и 180 нм составляет десятки раз. Когда вы проектируете видеокарту, которую планируете продавать сотнями миллионов штук, себестоимость кристалла не так важна (зато, кстати, играют роль затраты на более дорогое ПО, специфические корпуса и т.д.), зато если вы собираетесь выпустить всего десять тысяч каких-нибудь хитрых ASIC для управления DC/DC преобразователем, то разница между 180 и 350 нм вполне может определить окупаемость вашего изделия.

Особенно если ваше изделие не чисто цифровое. Сайт TSMC не очень-то открыт для посторонних, но не ими едиными. Сходим на сайт фабрики XFAB, к слову довольно популярной в России. В разделе “технология” длинный список, причем на каждые проектные нормы дано по несколько вариантов. Один процесс для аналоговых схем, другой для силовых, в третьем есть встроенные фотоприемники…

Если открыть даташит техпроцесса XP018 (180 нм), то мы увидим внутри десяток типов транзисторов, и столько же резисторов и конденсаторов. При этом обратите внимание на предельное значение Vgs — напряжения на затворе транзистора, там будут не только и не столько ожидаемые для 180 нм 1.8 Вольт, но и 5 Вольт! На самом-то деле этот техпроцесс — это не только 180 нм, в нем на едином чипе могут быть реализованы 180 нм транзисторы для быстрой и малопотребляющей логики, 500 нм транзисторы для аналоговых схем и схем ввода-вывода, и 1000 нм силовые ключи, способные работать с напряжениями в десятки Вольт. А у TSMC на том же кристалле могут быть еще транзисторы по 90, 65 и 40 нм, различающиеся не только геометрией, но также уровнями легирования и толщиной подзатворного диэлектрика, определяющими рабочие режимы транзистора. Общая стоимость произодства чипа обычно сопоставима с самыми тонкими имеющимися на нем проектными нормами: стоимость масок для фотолитографии нелинейно растет с уменьшением проектных норм, а вот дополнительные маски для более грубых опций увеличивают стоимость линейно, на единицы процентов каждая.

А что, если в вашем проекте основную часть занимают высоковольтные транзисторы, а логики совсем немного? Если вы способны потерпеть перенос логики с 40 нм на 180, или со 180 на 600, вы можете здорово сэкономить. И вот после изъятия 180 нм логики, техпроцесс XP018 волшебным образом превращается в техпроцесс XHB06 с проектными нормами 600 нм, и при этом становится существенно дешевле в производстве.

Вот отсюда и берется хорошая загруженность таких безнадежно устаревших технологий: мир требует не только новые процессоры для мобильных телефонов, но и новые драйверы для светодиодов во вспышке, управляющие схемы для электромотов беспилотных автомобилей, да просто микроконтроллеры для чайников и стиральных машин. А, например, для такого быстро растущего рынка, как интернет вещей, важна не столько производительность, сколько низкая потребляемая мощность, которой передовые технологии похвастаться не могут. И тот же TSMC сейчас активно разрабатывает не только техпроцесс 5 нм, но и новые опции для процесса 20 нм, которые позволят сделать новые поколения устройств для IoT лучше и дешевле.

Вот например, реклама Global Foundries про их технологии для микросхем интернета вещей, здесь десяток техпроцессов, от 22 до 180 нм. Про 7-10 речи не идет).

Сколько стоит и где взять?

Первое и самое важное, что надо понимать: очень много денег (десятки или сотни тысяч долларов в год) стоит САПР. Но есть и хорошие новости. Если не рассматривать варианты пиратства, то, во-первых, лицензии на САПР есть у некоторого количества ВУЗов (кто знает, может быть пора навестить alma mater), а во-вторых, на крупных проектных нормах можно собрать маршрут проектирования из разной степени удобности открытых и университетских тулов. Есть Electric VLSI (полностью бесплатно, GNU), есть редактор топологии Magic, есть симулятор verilog Icarus и на самом деле довольно много чего еще. Самое сложное — это проверка соответствия топологии правилам проектирования (DRC) и проверка соответствия топологии и схемы (LVS), но по 180-350-600 нм их вполне реально нормально сделать в том же Electric VLSI.

Также полезно сходить на Opencores.org и посмотреть там довольно много готовых и полуготовых проектов разной степени сложности. Здесь, например, можно найти опенсорный и уже проверенный в кремнии процессор архитектуры OpenRISC.

Сколько стоит производство?

Здесь самый сложный вопрос — даже не где взять денег, а как сделать так, чтобы фабрика вообще с вами заговорила. Про российские реалии разговор особый, на “Микрон” ходить бесполезно, а вот на пыхтящем со времен Брежнева производстве, которых в разных концах России сохранилось, пожалуй, больше десятка, может и выгореть. Что касается зарубежных заводов, то вам с вероятностью 100% потребуется юрлицо, и даже с ним большинство фабрик будут думать, спрашивать о ваших планах на масс-продакшен и т.д. и т.п. Большинство, но не все, так что можно пробовать. А еще можно все же сходить в alma mater и попробовать сделать через них, к университетам и отношение всегда хорошее, и цены вполне могут быть более лояльными.

В любом случае, для проверки работоспособности дизайна до запуска в серию у большинства фабрик есть сервис MPW (Multi-Project Wafer) — за довольно скромные деньги вам выдают площадь (обычно от 9-10 до 25 квадратных миллиметров), потом собирают много-много таких проектов вместе, производят и выдают каждому участнику несколько десятков чипов. Это стандартный маршрут при производстве, применяемый небольшими компаниями по всему миру. Стоимость MPW для проектных норм 180-600 нм у разных фабрик находится в диапазоне 500-1500 евро за квадратный миллиметр, производство занимает 3-6 месяцев. Небольшая серийная партия обойдется, скорее всего в 50-200 тысяч евро, в зависимости от фабрики, специфики проекта и т.д. и т.п.

Для проектных норм 28-20 и дальше речь будет идти уже о сотнях тысяч евро за тестовый запуск и миллионах за серийное производство.

Примеры цен на MPW можно посмотреть на сайте крупного университетского агрегатора Europractice. Нужно, разумеется, учитывать, что это цены для университетов, но разница с ценами для простых смертных не очень большая.

Для стартапа найти десять тысяч евро на запуск вполне реально (но, разумеется, в этом случае это только одна и не самая большая статья расходов), а для любителя наверное дороговато. Но десять квадратных миллиметров — это на самом деле очень много, и наверное можно попробовать присоединиться к университетскому проекту или найти еще несколько таких же энтузиастов и замутить стартап вскладчину реализовать на одном чипе несколько проектов. Опять же, это в любом случае дешевле, чем собирать собственное производство в гараже, а технического веселья вам в итоге вполне хватит с корпусированием (если не заказывать его на фабрике), макетными платами и измерительной аппаратурой.

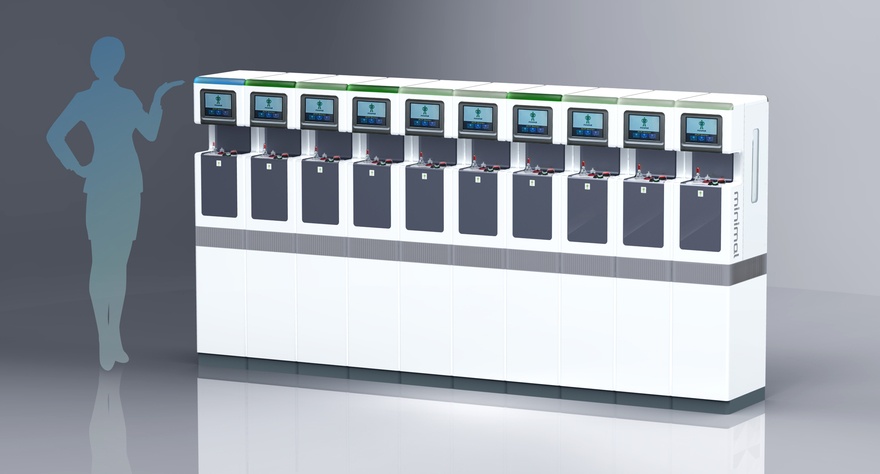

И напоследок — самую малость о «3D-принтерах для микросхем». Классический набор оборудования для производства стоит от нескольких сотен миллионов долларов до нескольких десятков миллиардов, и еще столько же придется вложить в подходящее помещение, но уже довольно давно в Японии разрабатывается проект Minimal Fab, конечной целью которого заявлена возможность производства микросхем хоть поштучно, без чистой комнаты и сложных требований к инфраструктуре, и за на несколько порядков меньшие деньги. Если все получится — это станет очень важной вехой в истории полупроводниковой индустрии, и сделает ее намного доступнее и гибче.

Вот так, по мысли авторов, оно будет выглядеть.

Я не слежу за этим проектом подробно, но в прошлом году его представители уже были на российских отраслевых выставках и конференциях, и вели переговоры о поставках. Насколько я понимаю, сейчас они уже близки к тому, чтобы обеспечить полный цикл производства, и речь идет о проектных нормах в диапазоне между 500 и 100 нм.

Автор: Валерий Шунков