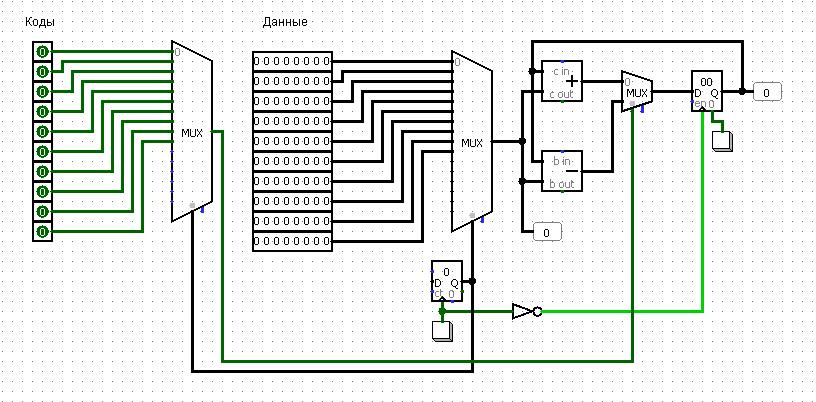

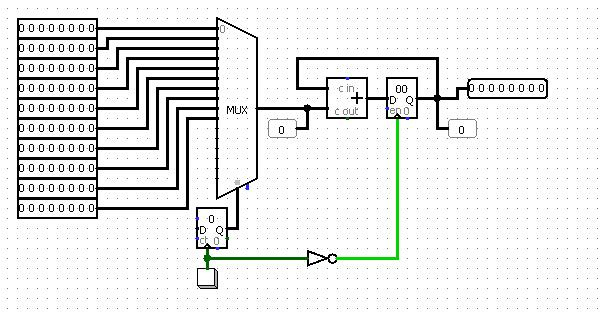

Одна из глав книги «Код» (Автор: Чарльз Петцольд) посвящена проектированию CPU и в начале главы описывается устройство, позволяющие суммировать наборы чисел, хранящихся в памяти. Спроектируем эту схему в Logisim'е. Возьмем набор восьмиразрядных чисел и подключим его к мультиплексору, переход от одного числа к другому будем осуществлять с помощью счетчика, подключенного к выбирающему входу мультиплексора, а к выходу мультиплексора подключим сумматор и аккумулятор. В качестве тактового генератора будем использовать кнопку. Данные будут загружаться в аккумулятор при отпускании кнопки (это осуществляется с помощью элемента НЕ, подключенного к кнопке).

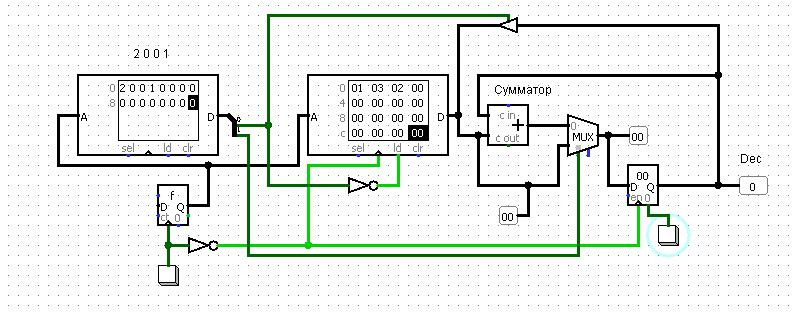

Далее реализуем операцию «вычитание», и будем хранить наши операции (команды) в отельном массиве. Команда «0» выполняет сложение, а команд «1» — вычитание. Далее эти команды подаются на вход мультиплексора, подключенного к Сумматору и Вычитателю.

Далее, допустим, нам нужно найти три суммы: трёх слагаемых, двух слагаемых и еще двух слагаемых. Реализуем устройство, позволяющее загрузить в аккумулятор значение из памяти и сохранить в памяти значение из аккумулятора, для этого уберем из схемы «вычитатель», а мультиплексор, который мы использовали для выбора операции мы будем теперь использовать для выборки данных из памяти.

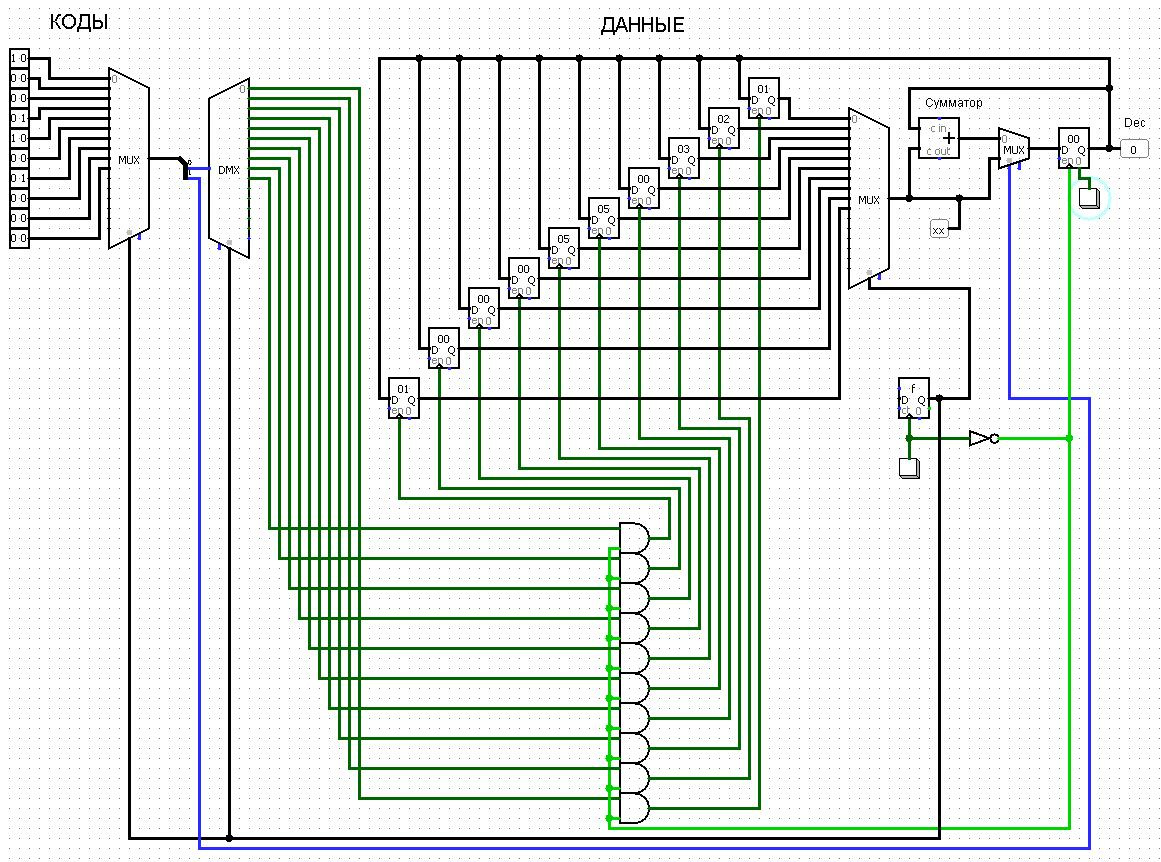

Для того, чтобы реализовать команду «сохранить», в массиве «данные» заменим элементы «Контакт» восьмиразрядными регистрами, добавим демультиплексор (дешифратор) для записи в регистры.

Увеличим разрядность команд: команда 10 загружает элемент из памяти в аккумулятор,

команда 00 прибавляет число из памяти к аккумулятору, команда 01 сохраняет в памяти значение из аккумулятора. «Разветвитель» позволяет разделить разряды команды, младший разряд отправить на мультиплексор, старший на демультиплексор.

Заменим отдельные регистры массивами RAM.

Будем использовать схему с одним синхронным портом чтения/записи (доступна по умолчанию). Для записи будем использовать управляемый буфер.

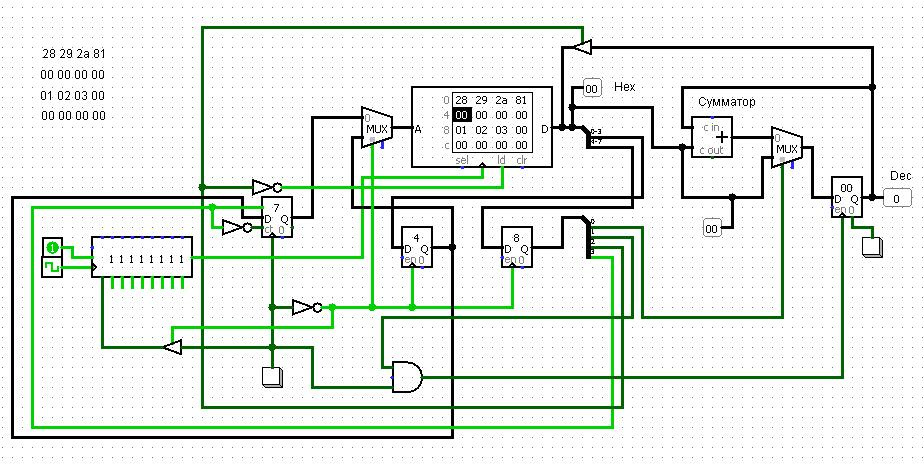

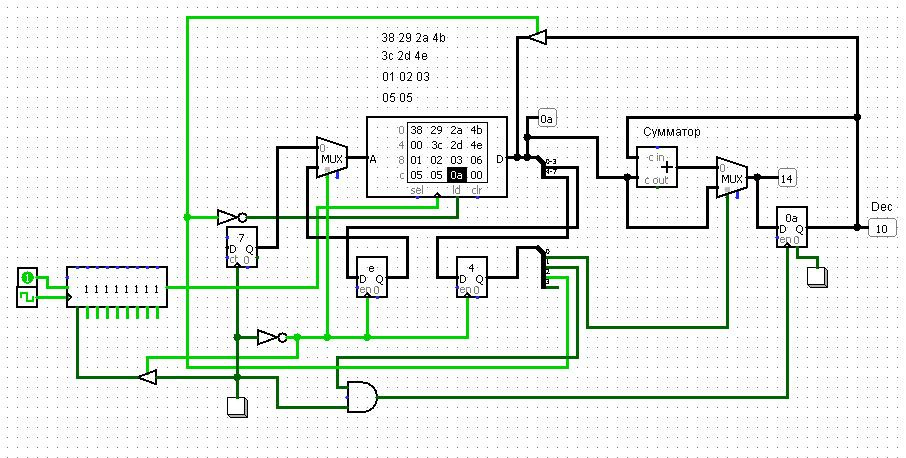

В нашем устройстве коды и данные хранятся в разных блоках памяти (Гарвардская архитектура). Спроектируем устройство, в котором коды и данные будут храниться в одном блоке (архитектура фон Неймана).

В первых четырех разрядах восьмиразрядной ячейки памяти будет храниться команда, во вторых четырех разрядах будет храниться адрес (абсолютная прямая адресация).

Будем загружать адрес и команду в отдельные регистры, а затем с помощью мультиплексора переходить по сохраненному адресу. Для записи данных в ОЗУ будем использовать схему задержки подачи импульса на основе сдвигового регистра.

Команда 3 загружает элемент из памяти в аккумулятор, команда 2 прибавляет число из памяти к аккумулятору, команда 4 записывает содержимое аккумулятора в ОЗУ.

Вот пример программы, которая складывает три числа (ячейки 8, 9, a) и сохраняет результат в свободную ячейку (ячейку b): 38 29 2a 4b.

Добавим также возможность совершать безусловные переходы.

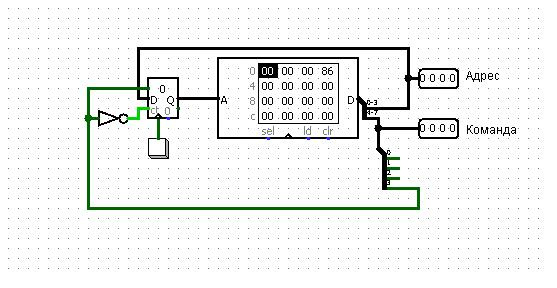

Реализуем устройство, в котором будет выполняться всего одна команда — команда безусловного перехода. Для этого на счетчик, генерирующий адрес, будем отправлять четыре младших разряда (собственно, адрес), а на порт загрузки будем подавать команду, хранящуюся в старших разрядах ячейки памяти.

Например, для прыжка в ячейку с адресом 6 используется команда 86.

Добавим это устройство к основной схеме.

Вообще, на geektimes уже была статья, посвященная проектированию CPU в Logisim.

Все схемы, представленные в статье, можно скачать одним файлом.

Logisim можно скачать здесь

Автор: demser