На Хабре достаточно много статей посвященных микроконтроллерам и языкам программирования на них, но не часто можно встретить статьи о программировании ПЛИС. Прошивки для ПЛИС можно писать на языках описания аппаратуры или рисовать схемы в САПРах фирм, производящих ПЛИС. Сегодня я хочу показать как можно запрограммировать АЛУ на ПЛИС фирмы Actel A3P250 (ProASIC 3 с числом эквивалентных вентилей 250 000) на языке описания аппаратуры SystemVerilog. Данная ПЛИС интересна тем, что позволяет прототипировать заказные микросхемы ASIC или БМК. Прошивки, которые синтезируются для данной ПЛИС можно превратить с серийную микросхему.

Кому интересно добро пожаловать под кат.

Итак, создание прошивки можно разделить на несколько этапов:

1. Определяем, что мы хотим получить, рисуем на листке бумаги, в голове или в Visio структурную схему будущего устройства. В моём случае это АЛУ, у него есть входы: два операнда по 4 разряда, вход сброса, вход синхронизации, вход кода операции 2 разряда ( 00 — сложение, 01 — вычитание, 10 — умножение, 11 — результат равен 0) и выход с результатом 8 разрядов.

2. Если проект сложный, то необходимо написать поведенческую модель, на каком-нибудь языке высокого уровня например на C#, по которой можно понять как это будет работать, в данном случае я этот пункт пропущу, т.к написать на Си или C#модель данного устройства смогут многие и я уверен лучше меня.

3. Собственно пишем код, я для этого использую NPP с подсветкой синтаксиса SystemVerilog хотя писать можно в любом текстовом редакторе или в одной из программ для моделирования, синтеза или трассировки микросхемы, но об этом далее.

Код прошивки на данном этапе я буду называть логической моделью, хотя в разных источниках может быть по разному.

4. Пишем тест для нашей логической модели, для этого можно использовать несколько методов. Так же на этом этапе объединяем тест и модель.

5. Запускаем нашу модель с тестом в среде моделирования. Я использую для моделирования QuestaSim, это продвинутая версия ModelSim от фирмы Mentor Graphics.

6. Если тесты выполнены успешно, то можно приступать к синтезу. Для синтеза я использую Precision Synthesis фирмы Mentor Graphics. Но можно использовать тот софт, который предоставляет вам производитель микросхемы. В результате синтеза мы получаем файлы в формате *.edf и Verilog, это логическая модель, собранная САПР синтеза из тех блоков, которые есть в ПЛИС, а так же описание связей между ними. Я буду называть эти файлы нет-листами.

7. Файл нет-листа в формате Verilog необходимо подключить вместо логической модели и заново запустить моделирование, что бы убедится в том, что синтез прошел успешно и синтезатор ничего не выкинул лишнего, он это очень хорошо умеет. Так же на данном этапе можно воспользоваться средствами формальной верификации, которая проверит соответствие полученного нет-листа логической модели.

8. Если нет-лист прошел тестирование можно приступить к размещению и трассировке нет-листа в ПЛИС, для этого я буду использовать Actel Designer, входящий в состав Actel Libero IDE. На данном этапе мы получаем готовую прошивку ПЛИС и, что не менее важно переработанный нет-лист и временные задержки в его цепях, нет-лист опять же имеет формат Verilog, а задержки генерируются в формате *.sdf.

9. Теперь необходимо промоделировать нет-лист, полученный в результате трассировки с временными задержками и убедиться, что всё работает.

10. Если все действительно работает, то можно прошивать.

Теперь вернемся к АЛУ.

Код в SystemVerilog состоит из модулей, во всяком случае в той части, что касается описания аппаратуры, т.к. при тестировании появляются ключевые слова class и program.

Как это не печально, но тега для SystemVerilog или хотя бы Verilog нет, но есть тэг для VHDL, пришлось использовать его…

Разберем модуль АЛУ по частям.

Сначала мы объявляем название модуля и входы/выходы, помните мы их определили на первом этапе.

module ALU

(

input rst, clk, // Сброс и синхронизация

input [1:0] cmd, //Командное слово

input [3:0] a,b, //Операнды

output logic [7:0] res //Результат

);

Затем объявляем несколько внутренних линий для соединения комбинационной части и триггерной.

logic [3:0] A, B;

logic [1:0] Cmd;

logic [7:0] outpRes;

Теперь опишем комбинационную или асинхронную часто АЛУ:

always_comb

begin

unique case(Cmd)

2'b00:

begin:add

outpRes = A+B;

end:add

2'b01:

begin:sub

outpRes = A-B;

end:sub

2'b10:

begin:mul

outpRes = A*B;

end:mul

2'b11:

begin:div

outpRes = 0;

end:div

endcase

end

И наконец триггерную или синхронную часть АЛУ, т.к АЛУ у нас будет синхронным

always_ff @(posedge clk, posedge rst)

if (rst)

begin

res <= '0;

A <='0;

B <='0;

Cmd <='0;

end

else

begin

A[3:0] <= a;

B[3:0] <= b;

Cmd <=cmd;

res <= outpRes;

end

Модуль закроем ключевым словом:

endmodule

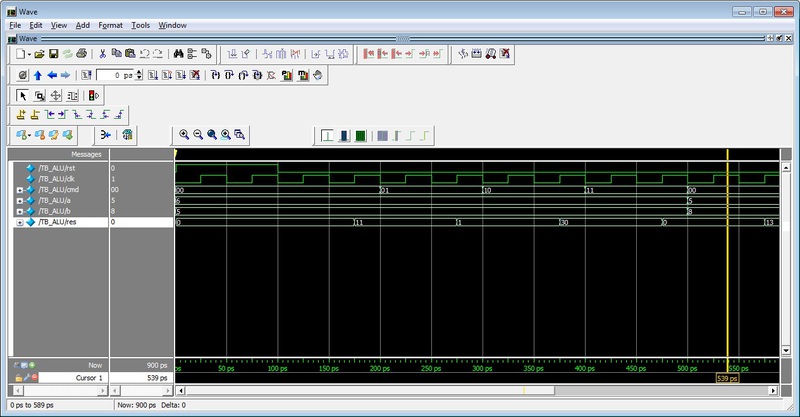

Теперь напишем тест и запустим моделирование, получим следующую временную диаграмму:

Как мы видим операции выполняются, но из-за двух триггеров на входе и на выходе получается задержка в 2 такта, это можно исправить, но мы же просто рассматриваем пример, а не создаем Core i7, поэтому оставим так и перейдем к синтезу:

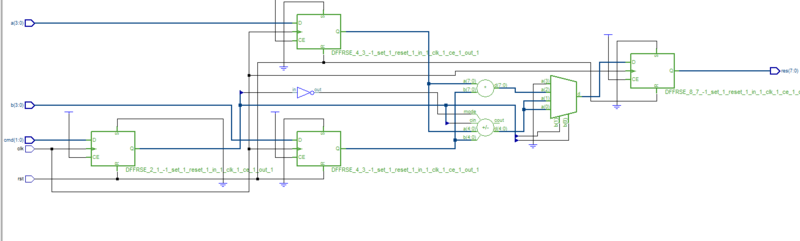

Синтезатор решил, что наша схема будет выглядеть так, как на рисунке сверху, вообщем-то тут я с ним согласен, хотя это бывает не всегда и поэтому даже не буду запускать тест ещё раз сразу приступим к трассировке в кристалл.

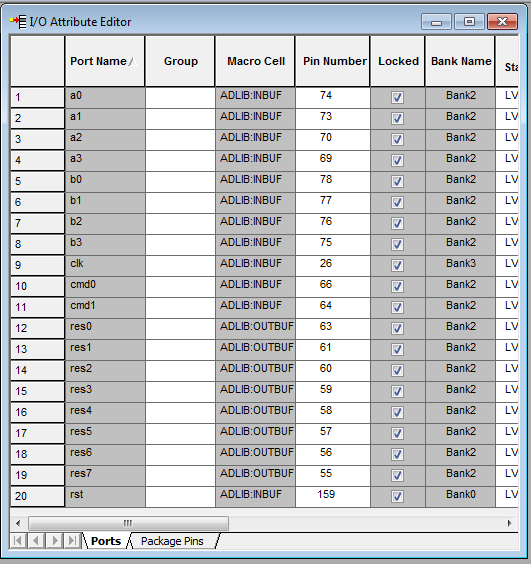

Т.к. у меня есть дизайн кит, то я расставлю выводы ПЛИС следующим образом:

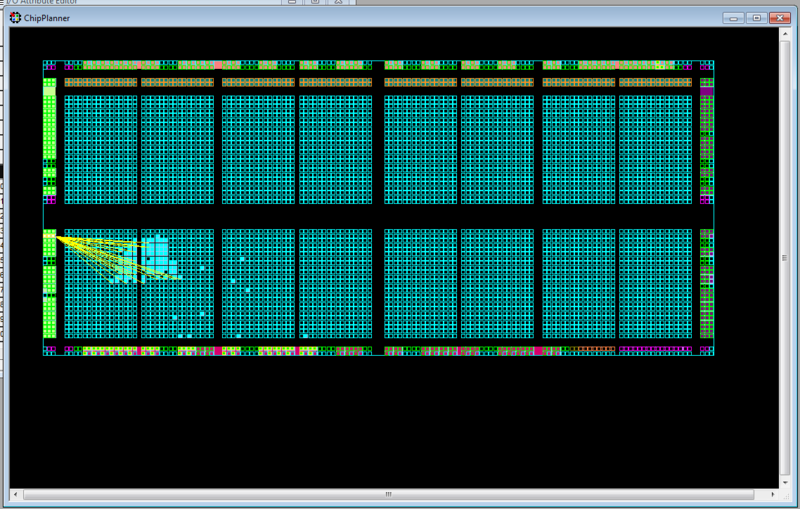

Результат работы трассировщика (размещение элементов в кристалле) на рисунке ниже, кстати на данном этапе можно подвигать элементы по кристаллу.

Жёлтым выделена цепь тактового сигнала.

На этом я хочу закончить свой рассказ, видео будет позже.

Спасибо всем, кто дочитал до конца, извиняюсь за стиль и возможные ошибки в тексте, но я не писатель только учусь.

P.S. Кому интересно ПЛИСами занимаюсь уже 3 года, данный проект АЛУ сделан за час, необходим был простенький макет для проверки одной методики внесения сбоев.

Автор: Fandir