Упаковка чипов (chip packaging) играет критически важную, хоть и не всем заметную роль в производстве электроники. Будучи физическим интерфейсом между процессором и материнской платой, упаковка является передаточным звеном для электрических сигналов и питания. Чем выше требования предъявляются к процессору, тем сложнее становится проблема упаковки.

В этой статье мы коротко расскажем о новейших технологиях упаковки, представленных буквально в этом месяце и покажем слайды маленькие презентационные видеоролики.

Итак, упаковка — это не просто последний этап в процессе изготовления процессора — это один из объектов инновации. Продвинутые технологии упаковки позволяют объединять разнородные вычислительные элементы, созданные по различным технологиям, при этом производительность остается на уровне однокристальной системы, а размер намного ее превышает. Эти технологии кардинально изменяют всю архитектуру системы, увеличивая ее производительность и эффективность.

Вот о каких инновациях в упаковке Intel поведала миру на прошедшей в июле в Сан-Франциско конференции SEMICON West.

Co-EMIB. Технологии Intel EMIB и Foveros используют высокоплотные интерконнекты для обеспечения высокой пропускной способности при низком потреблении; таким образом достигается высокая плотность ввода-вывода.

Intel Foveros — первая в отрасли технология объемной компоновки логических микросхем. Она обеспечивает большую гибкость по сравнению с похожей технологией с пассивной объединительной подложкой. Однокорпусная система может быть разделена на большее число блоков, которые располагаются вторым слоем поверх базового кристалла, на котором сформированы блоки ввода-вывода, память SRAM и цепи питания.

Co-EMIB позволяет осуществить взаимное соединение двух и более элементов Foveros с производительностью одночиповой системы. В отличие от конкурирующих технологий для Co-EMIB не требуется дополнительный соединительный кристалл.

ODI (Omni-Directional Interconnect) обеспечивает еще большую гибкость в коммуникациях между элементами упаковки. Главный чип может взаимодействовать с другими чиплетами так же, как и при использовании EMIB. Также взаимодействие может происходить вертикально через сквозные кремниевые переходы — through-silicon vias (TSV) с базовым кристаллом внизу, как в Foveros. ODI использует крупные вертикальные перемычки для доставки энергии к верхнему кристаллу от основания. Большие TSV имеют меньшее сопротивление, обеспечивая более надежный подвод энергии и меньшую латентность. Кроме того, данный подход уменьшает число необходимых TSV, освобождая место для активных элементов и экономя место в упаковке.

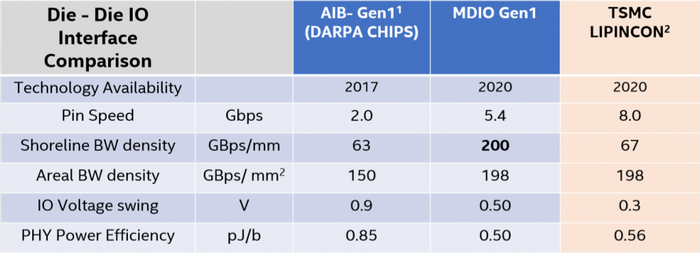

MDIO (Multi-Die I/O), интерфейс взаимодействия между кристаллами, построен на базе Advanced Interface Bus (AIB). Данная технология позволяет реализовывать модульный подход к дизайну систем, имея в своем составе библиотеки интеллектуальной собственности чиплетов. MDIO обеспечивает лучшую энергоэффективность, а также вдвое большую скорость на пин и плотность полосы пропускания. В таблице ниже приводится сравнение MDIO с предшествующей технологией и конкурентом от компании TSMC.

Эти технологии могут употребляться совместно. Мы увидим их уже в ближайших поколениях SoC Intel.

Автор: saul