Как быстро выяснить схему соединений, когда на плате 70 микросхем в BGA?

Как протестировать плату, начиная с проверки соединений и заканчивая функциональными испытаниями?

Что можно вытворять с помощью JTAG сканирования? Где применять?

Возьмите в свой арсенал этот действительно полезный и могучий инструмент!

❯ Что такое пограничное сканирование (JTAG Boundary Scan)?

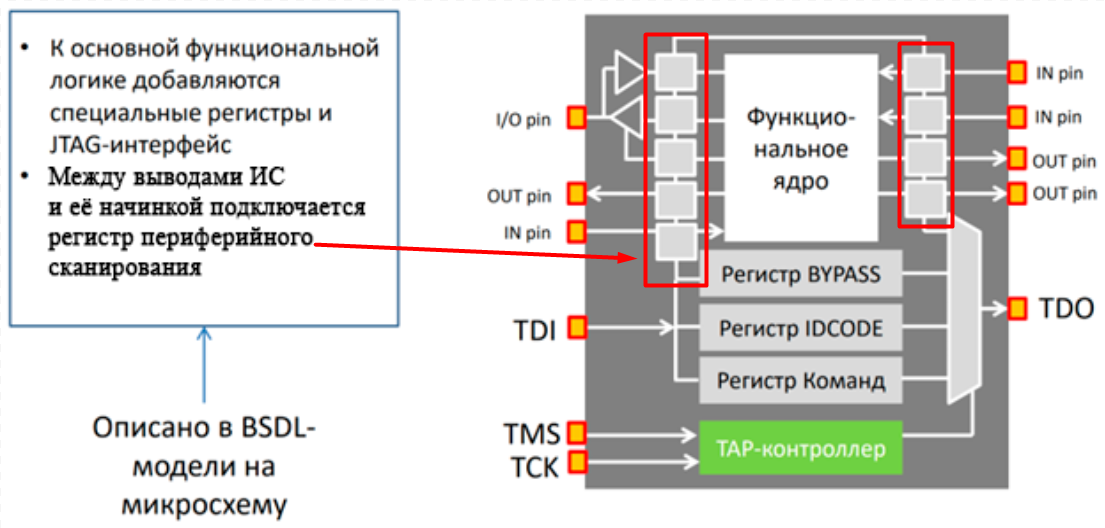

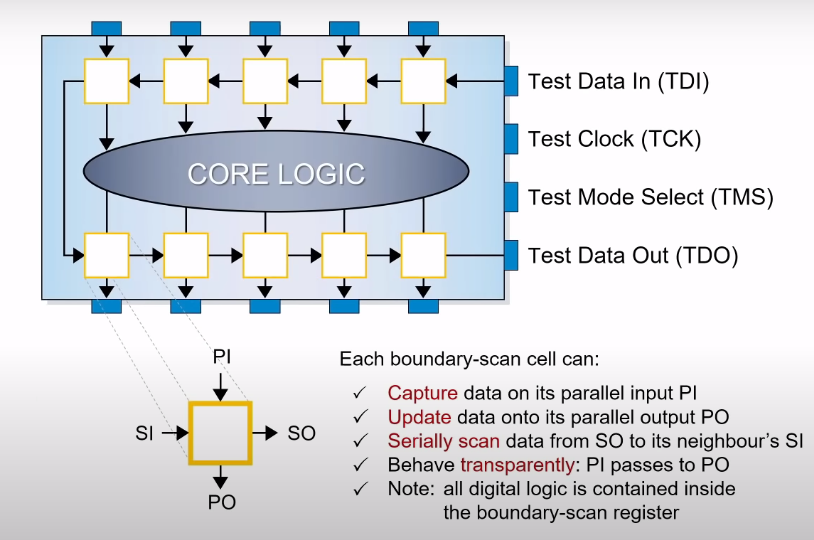

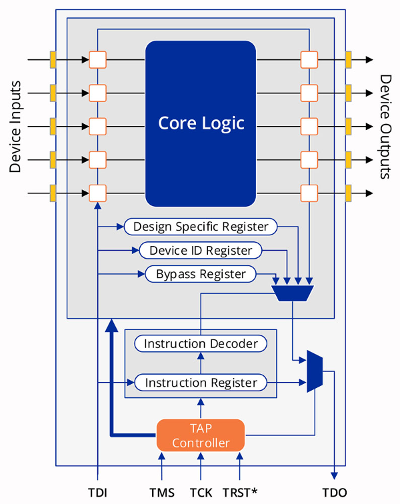

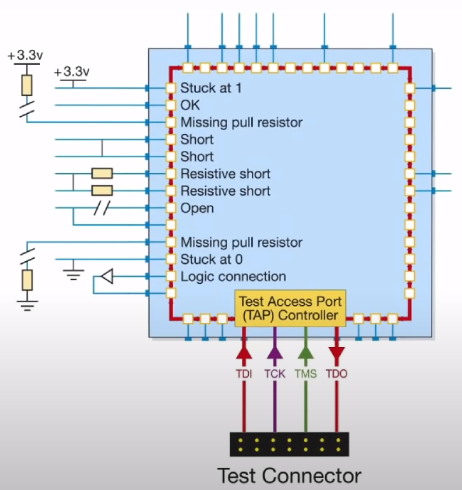

Помимо основной схемы, в микросхему добавляют регистры JTAG интерфейса и немного «кремния», который изолирует основную логику от контактов.

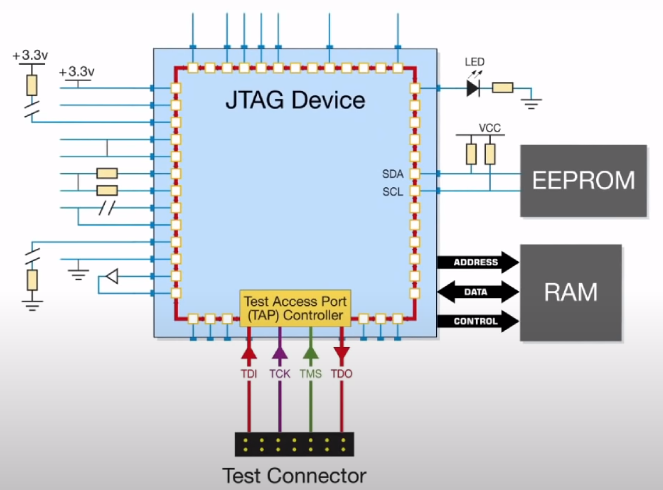

Это позволяет напрямую управлять выводами через JTAG без необходимости настраивать, включать или программировать основную логику устройства. Поэтому не имеет значения, является ли ядром микросхемы FPGA, процессор, Ethernet PHY, память DDR или что-то ещё. В этом и заключается концепция пограничного (или периферийного) сканирования: сделать тестирование на уровне платы независимым от типа устройств, установленных на неё.

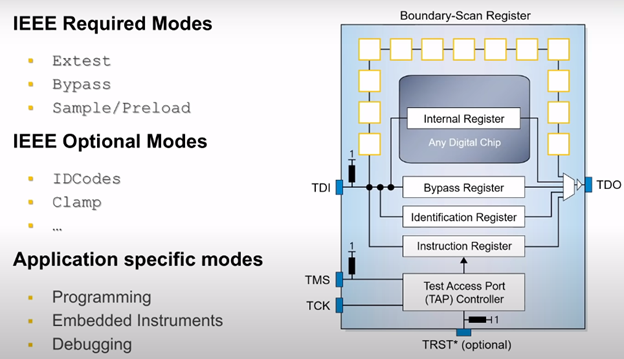

JTAG – четырехпроводной интерфейс (TMS, TDI, TDO, TCK – обязательные линии, TRST – дополнительная), позволяющий управлять тестовым портом доступа (Test access port, TAP), который представляет собой относительно простой конечный автомат. Внутри конечного автомата можно настроить разные регистры.

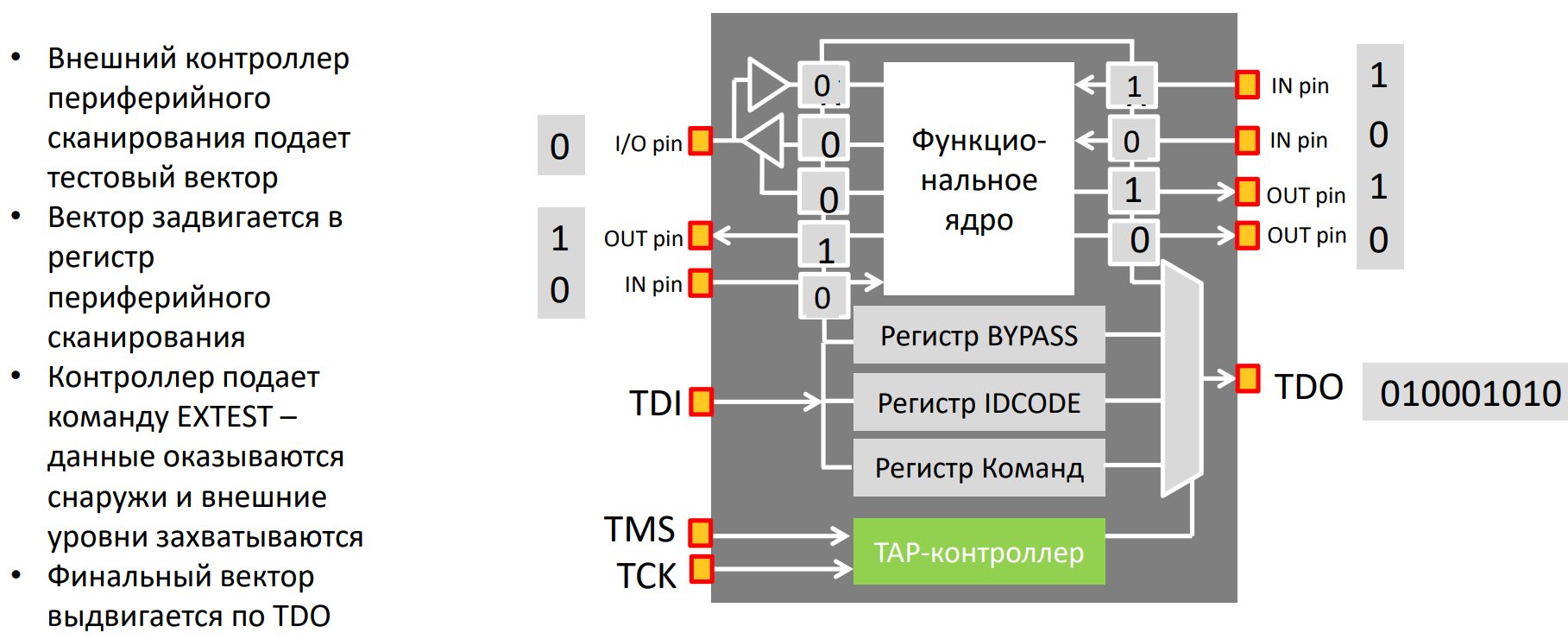

Регистр EXTEST даёт контроль над выводами устройства. Изменяя биты в этом регистре, можно устанавливать или считывать состояния контактов.

В регистре IDCODE хранится уникальный 32-битный код микросхемы, содержащий информацию о производителе, типе микросхемы и версии кристалла. Подделать этот код не представляется возможным, поэтому при несовпадении ID кода с информацией на упаковке или корпусе микросхемы можно сделать вывод, что она поддельная (входной контроль компонентов с поддержкой JTAG).

JTAG даёт возможность выявлять в цепях различные дефекты: разрыв, короткое замыкание между цепями или на линию питания (зависание 0 или 1) и др. Можно проверять простые логические цепи, подавая воздействие и ожидая известный результат, и прочее.

Если к выводу подключен генератор, то можно проверить его работоспособность по наличию переключений.

Можно взаимодействовать с устройствами, не имеющими JTAG, имитируя целевой интерфейс (I2C, SPI, управление оперативной памятью, датчиками и т. д.) с помощью «ногодрыга» (bit-bang). Скорости обмена информацией при имитации интерфейсов с помощью JTAG будут медленнее, чем при использовании штатных модулей интерфейсов. Но работоспособность проверить или сделать ещё что-то полезное можно.

В последовательную цепочку JTAG можно соединять более одного устройства.

Кроме управления выводами и стандартных режимов производители могут закладывать в свои устройства присущие конкретному приложению (application specific) функции и предоставлять к ним доступ через JTAG.

Программирование, отладка, встроенные инструменты (например, опрос датчика температуры ядра) и др.

❯ Где можно использовать?

Встроенный JTAG есть у большинства 32-битных микроконтроллеров, процессоров, у всех FPGA и CPLD, и даже у некоторых Ethernet PHY.

Из принципа работы видно, что пограничное JTAG сканирование можно применять для производственных испытаний собранных плат, входного контроля микросхем (выявление подделок), прямой и обратной разработки, ремонта.

Прямая разработка:

- Проверка правильности и целостности связей в электрических цепях, поиск обрывов, коротких замыканий и т. д.

- Проверка работоспособности простых устройств (вроде логических схем, светодиодов, кнопок, генераторов колебаний и прочего).

- Проверка работоспособности различных устройств без интерфейса JTAG: памяти, модулей, датчиков, АЦП, микросхем RS-485 и т. д.

- Загрузка/считывание прошивки flash памяти, CPLD, FPGA, процессоров, микроконтролеров и т. д.

- Отладка (относится к расширенным функциям JTAG).

- …

Обратная разработка:

- Чтение/запись памяти, регистров устройств по I2C, SPI и других.

- Создание каких-то вспомогательных условий (записью в регистры), нужных в данный момент для обратной разработки.

- Выяснение схемы соединений между устройствами. Особенно актуально для BGA корпусов и многослойных плат.

- Загрузка/считывание прошивки из flash памяти, CPLD, FPGA, процессоров, микроконтролеров и т. д.

- Отладка (относится к расширенным функциям JTAG).

- …

– Мы делаем штучные платы в лаборатории. Допустим, монтажники принесли собранную плату. Было бы очень удобно быстро проверить, всё ли работает (как спаяли).

Примеры применения и возможности периферийного JTAG сканирования удобно рассмотреть, изучив некоторые программные инструменты для его выполнения.

❯ Пакет программ XJTAG

Возможности XJTAG в удобной структурированной форме коротко и довольно ёмко описаны на официальном сайте. Cостав пакета XJTAG

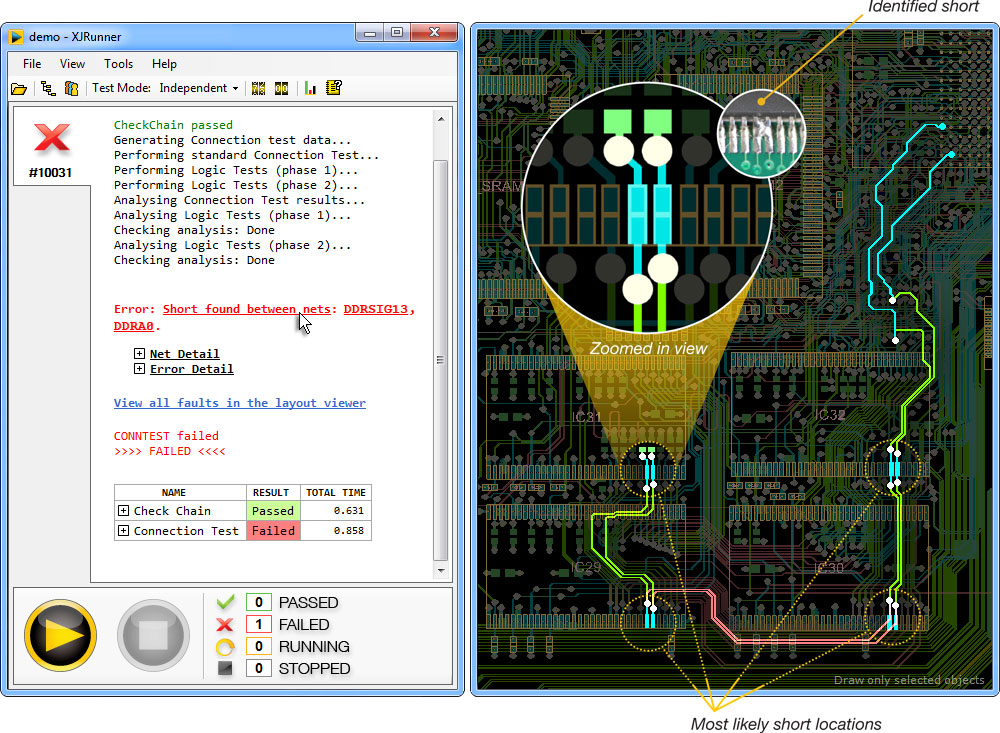

В XJRunner можно запускать созданные с помощью XJDeveloper тесты межсоединений, производить внутрисистемное программирование, тестирование устройств без JTAG и др. Есть богатая встроенная библиотека с файлами для разных устройств, на основе которой можно с минимальными усилиями создавать свои тесты для проверки прототипа или испытаний на производстве.

Если на плате найден дефект цепи (обрыв, замыкание и др.), Layout Viewer покажет наиболее вероятные места его расположения. Это позволяет быстро найти точное физическое место нахождения компонента, цепи и контакта на тестируемой плате. Layout Viewer показывает топологию печатной платы, которую он извлекает из ODB++ файла. Такие файлы можно создавать и в Altium Designer.

Для упрощения навигации по плате можно наложить на цепи фото платы. Так гораздо удобнее!

Такой инструмент значительно упрощает поиск неисправностей.

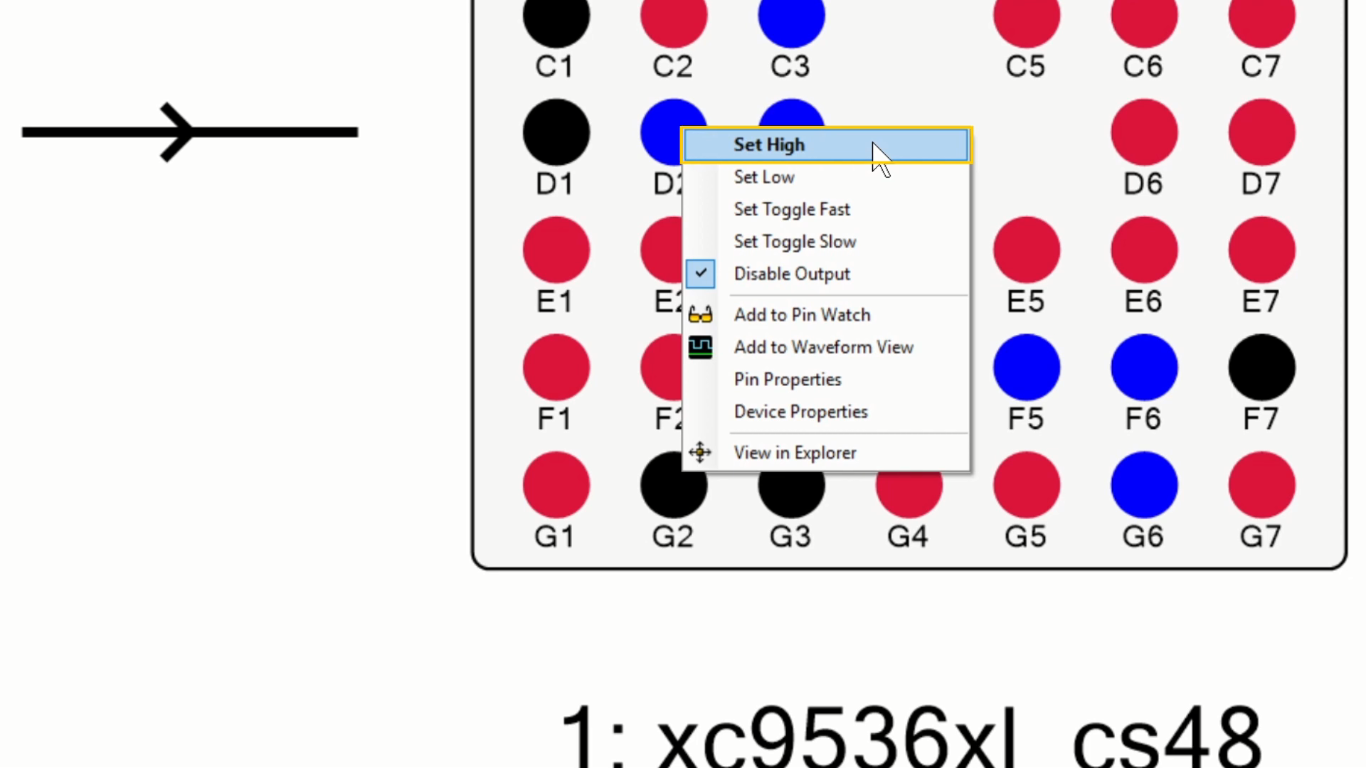

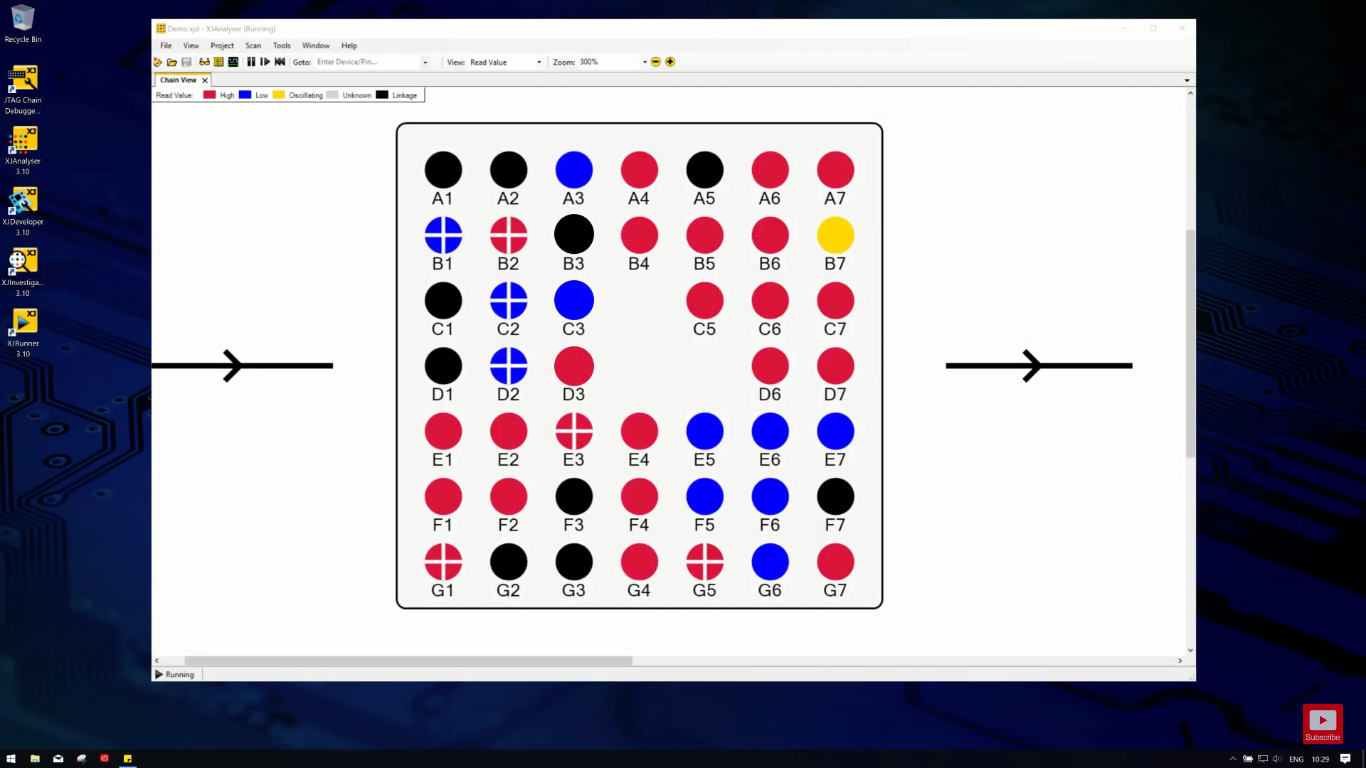

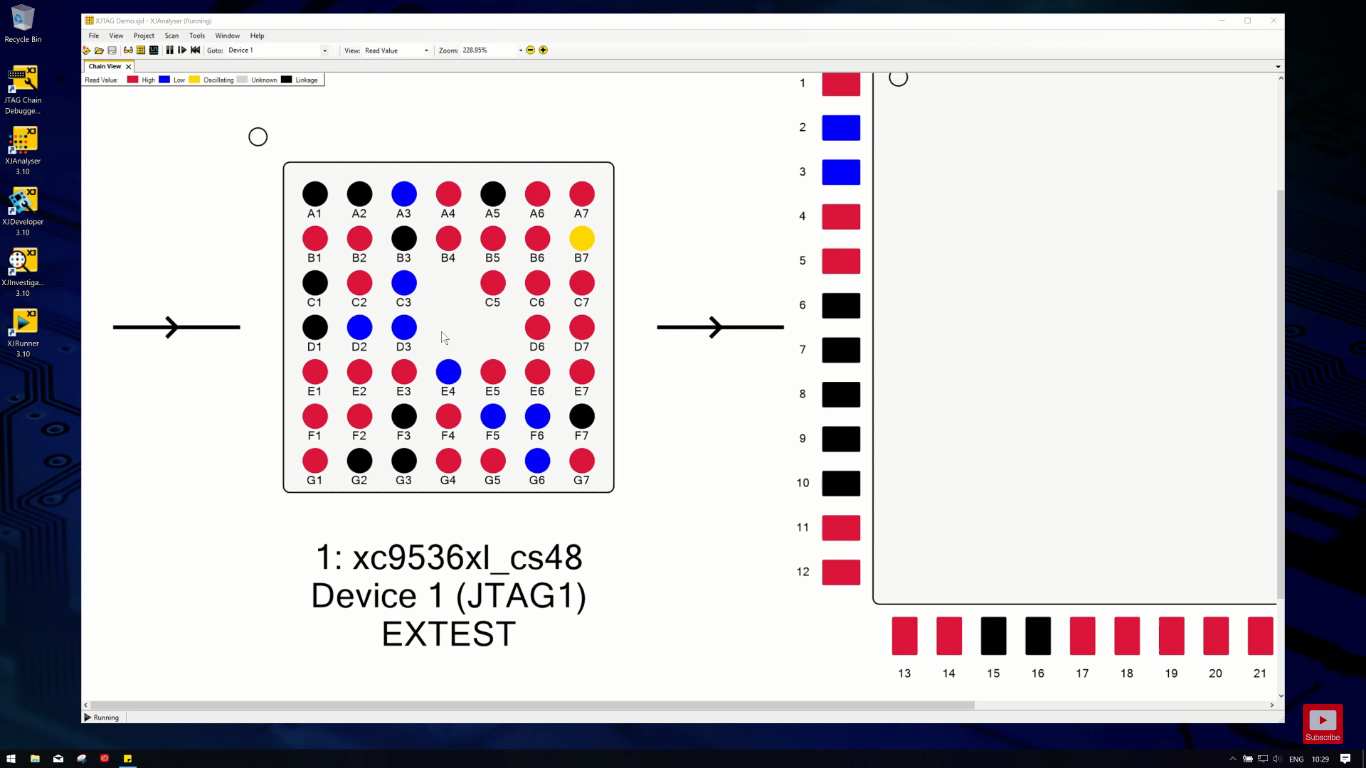

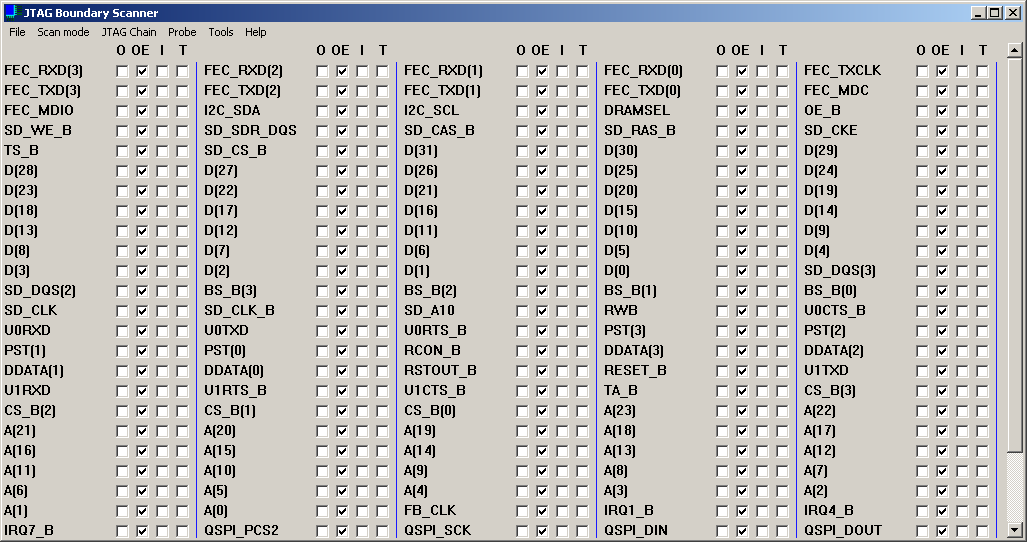

XJAnalyser — мощный инструмент для визуализации и отладки цепей в реальном времени. Позволяет выбирать отдельный вывод и прямо с компьютера устанавливать его состояние: высокий или низкий уровни, постоянное быстрое или медленное переключение, отключение вывода (перевод в высокоомное состояние). И все это с помощью интуитивно понятного графического интерфейса.

Состояния контактов можно не только устанавливать, но и считывать. Красный цвет соответствует высокому логическому уровню, синий – низкому, черный – это непригодные для использования контакты (например, питание).

Что интересно, на плату можно подать какой-то внешний меняющийся сигнал, который придёт на определённый вывод микросхемы. Тогда этот вывод будет переключаться и мы увидим это на экране.

Можно сделать наоборот: с помощью JTAG включить постоянное переключение вывода и искать этот сигнал с помощью осциллографа на плате. Это полезно для выявления дефектов цепей (замыканий, обрывов и прочего), а также для обратной разработки.

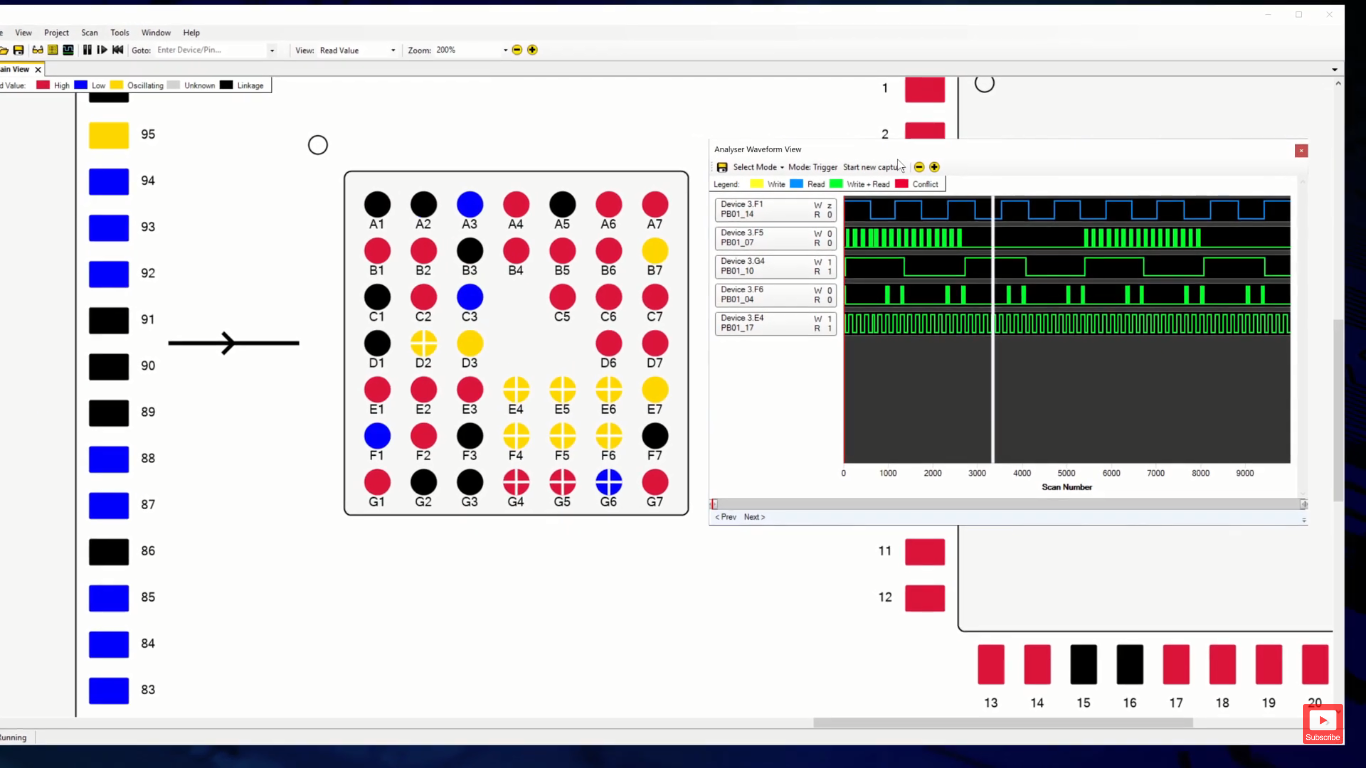

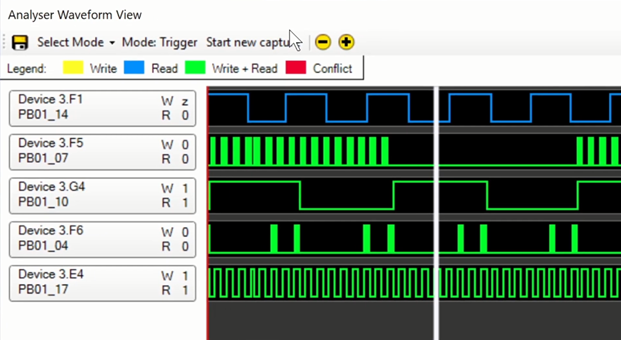

XJAnalyser может представлять данные цепочки JTAG в стиле логического анализатора с помощью Waveform Viewer:

Это упрощает отладку, предоставляя возможность для захвата и отображения цифровых сигналов отдельных контактов или шин с течением времени, что помогает выявить и исправить трудноуловимые временные неисправности. Настраиваемый триггер делает процесс ещё более удобным.

В динамике всё это выглядит ещё интереснее (рекомендую посмотреть XJAnalyser – Real-time visual PCB analysis and debug). Короткая и ёмкая демонстрация возможностей профессионального пакета XJTAG с понятным объяснением – JTAG Testing with XJTAG Boundary Scan.

Для использования XJAnalyser не нужно писать прошивку микросхем на плате. Можно даже не запускать тактирующие генераторы.

❯ Кряк, ты вылечишь это от жадности?

Пакет программ XJTAG видится полезным и весьма интересным. Он может пригодиться как любителям электроники для прямой и обратной разработки, ремонта, так и профессиональным инженерам.

Можно скачать полнофункциональную 30-дневную пробную версию XJTAG.

Для работы нужно подключить испытываемую плату к компьютеру с помощью фирменной коробочки XJLink 2 (характеристики) и загрузить BSDL файлы (Boundary Scan Description Language) для каждой микросхемы с JTAG. Файлы BSDL можно скачать с сайтов производителей или в других местах.

Интересно, что XJLink 2 можно приобрести на Али примерно за 70000 р (на конец ноября 2024 г). Возможно, получится подружить пакет XJTAG с какой-то значительно более дешёвой коробочкой/платой.

Кряк любит такие инструменты и уже заинтересовался! ☺ А вы?

❯ 70 микросхем в BGA. Как быстро и просто выяснить схему соединений?

Пример поиска соединений между BGA корпусами можно найти здесь.

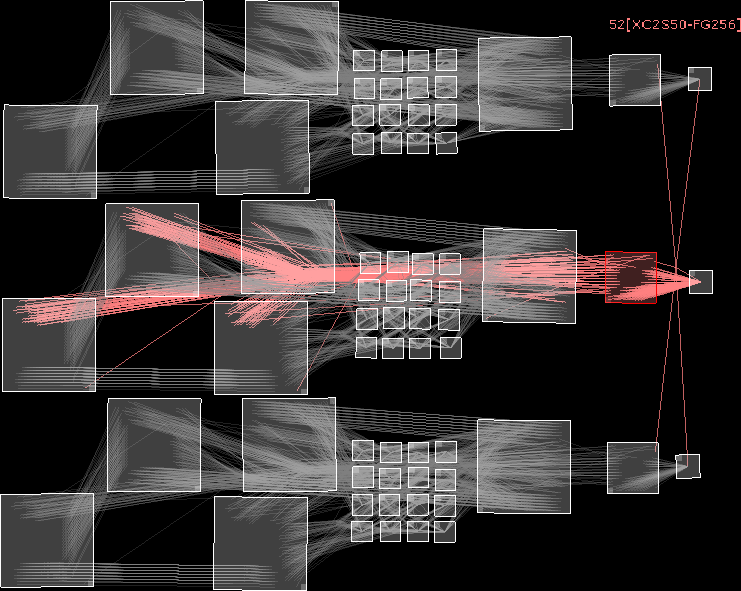

Задачу авторы проекта решили с помощью граничного JTAG сканирования. Для удобства разработали инструмент jrev, который исследует все пары JTAG-сканируемых контактов на плате. Результаты можно визуализировать в виде интерактивных рисунков с помощью jvis.

Алекс Форенчич несколько изменил код и выложил на Гитхабе.

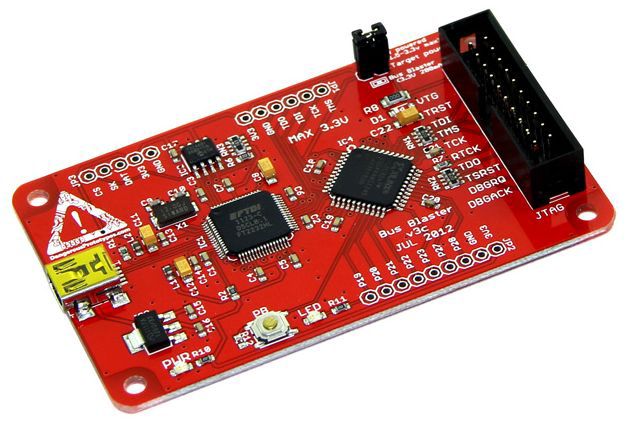

Программа FTjrev совместима с Bus Blaster v2+, о чём говорится на странице проекта Bus Blaster, и вообще с платами JTAG на базе FT2232 (проект находится здесь).

❯ Какие ещё есть инструменты?

Бесплатные.

Кроме открытых FTjrev, jrev и jvis есть другие бесплатные варианты.

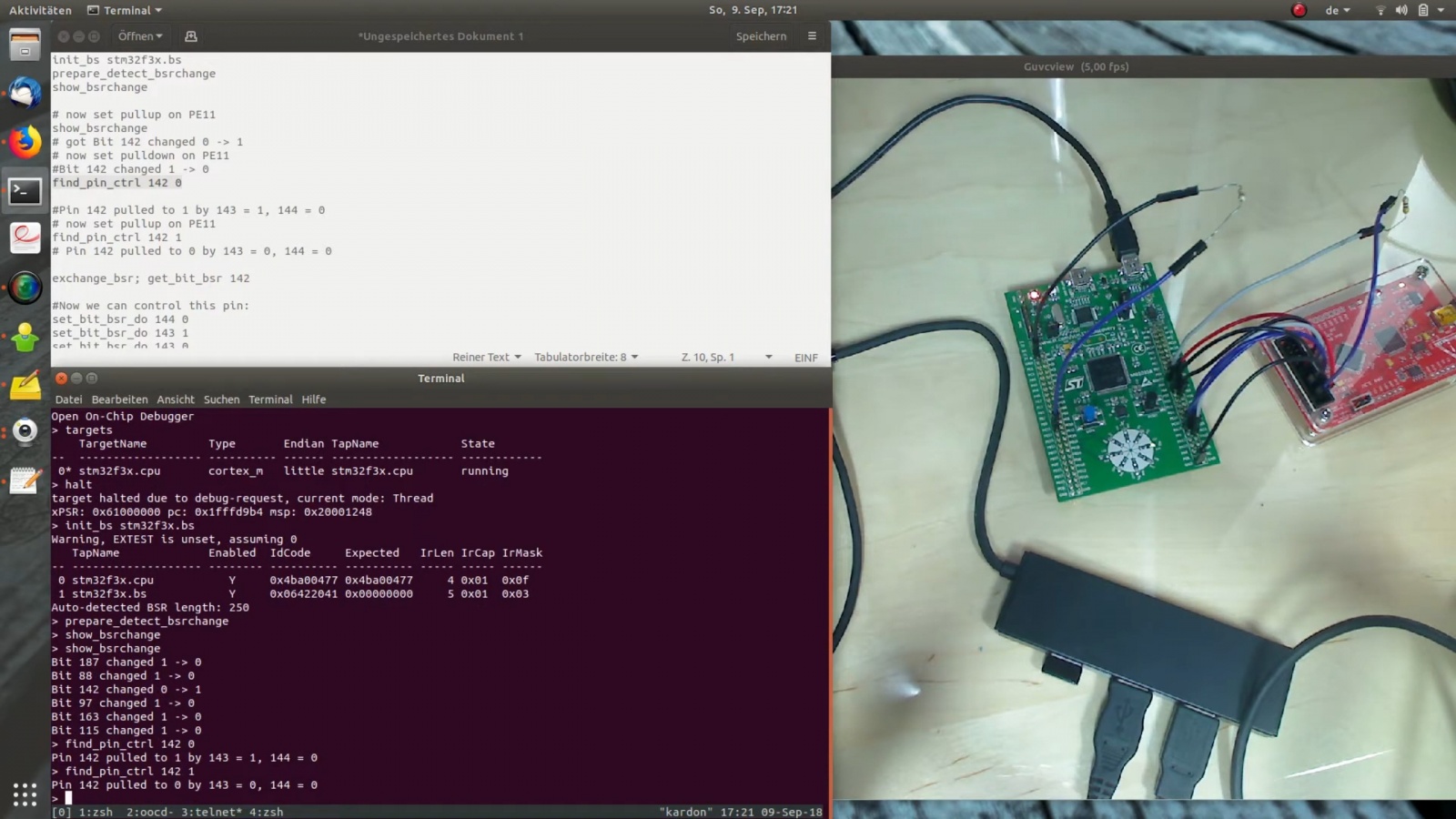

Использовать JTAG сканирование и управлять платой можно и с помощью связки OpenOCD + Bus Blaster v3, как показано здесь.

В платном пакете JTAG Live Studio есть бесплатная программа JTAG Live Buzz, которая может:

- Проверять работоспособность JTAG-цепочки (считывается TAP-регистр идентификатора микросхемы, и проверяется на совпадение с идентификатором, который находится в BSDL-файле). Можно использовать для выявления поддельных микросхем. ID код у них обычно отличается от оригинальных микросхем.

- Проверять соединения между двумя выводами.

- Считывать состояние вывода в реальном времени.

- Проверять узел разветвленной цепи, к которой подключены один выход и несколько входов.

JTAG Boundary Scanner от Viveris.

Открытый проект для отладки или тестирования через JTAG. Работает с платами на основе FT2232H, JLINK и др.

Даёт возможность смотреть состояние и управлять контактами ввода-вывода микросхем; имитировать I2C, SPI, MDIO и др. Поддерживает скрипты.

Управлять программой JTAG Boundary Scanner можно с помощью Питона. Для этого есть проект Pyjtagbs. Дополнительно можно посмотреть здесь.

Платные.

Более-менее подробно мы рассмотрели XJTAG. В целом, возможности у платных инструментов похожи. Поэтому рассмотрим остальные инструменты кратко.

JTAG Live Studio платная. Предлагает минимальный уровень автоматизации тестов. Краткое описание пакета, демонстрация всего пакета JTAG Live Studio. Работает с разными платами, в том числе на основе FT2232H.

Сложные изделия тестируют в старшей системе – JTAG ProVision. Она практически полностью автоматизирована, поддерживает большое число TAP-портов. Включает в себя огромную библиотеку не-JTAG компонентов, которые можно также протестировать. Можно интегрировать с Альтиум дизайнером через JTAG Maps. Но и стоит раза в 4 дороже.

Это не полный список инструментов. Есть другие.

Дополнительно можно посмотреть, например, список JTAG Boundary Scan Software.

❯ Коротко о главном

Помимо основной схемы, в микросхему добавляют регистры JTAG интерфейса и немного «кремния», который изолирует основную логику от контактов.

Это позволяет напрямую управлять выводами через JTAG без необходимости настраивать, включать или программировать основную логику устройства. Поэтому не имеет значения, является ли ядром микросхемы FPGA, процессор, Ethernet PHY, память DDR или что-то ещё. В этом и заключается концепция пограничного (или периферийного) сканирования: сделать тестирование на уровне платы независимым от типа устройств, установленных на неё.

Встроенный JTAG есть у большинства 32-битных микроконтроллеров, процессоров, у всех FPGA и CPLD, и даже у некоторых Ethernet PHY.

Можно взаимодействовать с устройствами, не имеющими JTAG, имитируя целевой интерфейс (I2C, SPI, управление оперативной памятью, датчиками и т. д.) с помощью «ногодрыга» (bit-bang).

В регистре IDCODE хранится уникальный 32-битный код микросхемы, содержащий информацию о производителе, типе микросхемы и версии кристалла.

Из принципа работы видно, что пограничное JTAG сканирование можно применять для производственных испытаний собранных плат, входного контроля микросхем (выявление подделок), прямой и обратной разработки, ремонта.

Для этого существуют различные платные и бесплатные инструменты. Предоставляемые ими возможности впечатляют и часто значительно упрощают задачу.

- Длинное видео про JTAG Boundary Scan. В первой части теория и основы. Во второй части демонстрация возможностей пакета программ XJTAG Every HW Engineer Needs To Know This About JTAG (with David Ruff)

- XJAnalyser – Real-time visual PCB analysis and debug

- Короткая и ёмкая демонстрация возможностей профессионального пакета XJTAG с понятным объяснением – JTAG Testing with XJTAG Boundary Scan

- XJTAG: состав пакета программ; структурированное, короткое и ёмкое описание возможностей.

- Использование JTAG для обратной разработки. Программные инструменты jrev и ftjrev.

- OpenOCD boundary scan on STM32 JTAG сканирование и управление платой с STM32 через OpenOCD и Bus Blaster v3.

- Тестирование встраиваемых систем: разработка тестового ПО или JTAG Functional Test?

- Что такое JTAG сканирование, затем демонстрация пакета программ JTAG Live Studio (доклад на конференции FPGA-Systems 2021.1, презентация).

- Краткое описание платного пакета JTAG Live. Запуск бесплатной JTAG Live Buzz с адаптером на чипе FT2232H.https://microsin.net/adminstuff/others/jtag-live-and-ft2232h-adapter.html

- EEVblog #499 — What is JTAG and Boundary Scan? С демонстрацией XJTAG, XJLink 2 в конце.

- JTAG Boundary Scan Software. Список ссылок на ПО с некоторым описанием.

- Входной контроль компонентов с поддержкой JTAG (Представительство JTAG Technologies)

- Инструкция по созданию файла ODB++ в Altium Designer.

- https://iosifk.narod.ru/jtag_page.htm

- BSDL Files Library for JTAG

- JTAG Functional Test (JFT).

Уважаемые читатели, будьте так любезны и ответьте на вопросы. Нам всем будут интересны результаты. Благодарим за голосование!

Автор: Kopcheniy