Год 2017 стал годом больших изменений в зарождающейся экосистеме российской микроэлектроники. Эти изменения заметило даже ранее безразличное к российскому железу общество. Российский чип ELISE для умных камер от ЭЛВИС-НеоТек вышел на удобной плате для разработчиков. Эту плату показали по Первому каналу российского телевидения. C российским процессором Байкалом-Т теперь может поработать любой программист через доступ к серверам удаленной лаборатории, которую байкаловцы создали вместе с МГУ. Российские процессоры от НИИСИ стали использовать для телекоммуникационного оборудования.

Для перехода от единичных успехов к развитой экосистеме необходимо подкрутить образование. В сентябре в Томске прошло совещание, на котором преподаватели и инженеры из Москвы, Сибири, Поволжья, Калифорнии и других мест обменялись опытом в преподавании микроэлектроники. Одновременно там же прошел учебный семинар по SystemVerilog, VHDL, FPGA, CPU IP, на который пришли не только россияне, но и студенты из Китая и Вьетнама, среди которых быстро распостранилась информация, что рядом учат чему-то полезному для их карьеры. Под катом — отчет об этом и сопутствующих событиях. Действующие лица: томские и новосибирские университеты, московские МГУ, МФТИ и МИЭТ, новосибирские лицеи, российская компания МЦСТ, американские MIPS, AMD и National Instruments, британская Imagination и казахский Назарбаевский Университет.

Прежде чем вы увидите фотографии довольно обедающих участников семинара в ресторане сибирской кухни, скажем пару слов о позиции обсуждаемых технологий в мироздании, для тех, кто пришел в этот пост из другой части технологической вселенной.

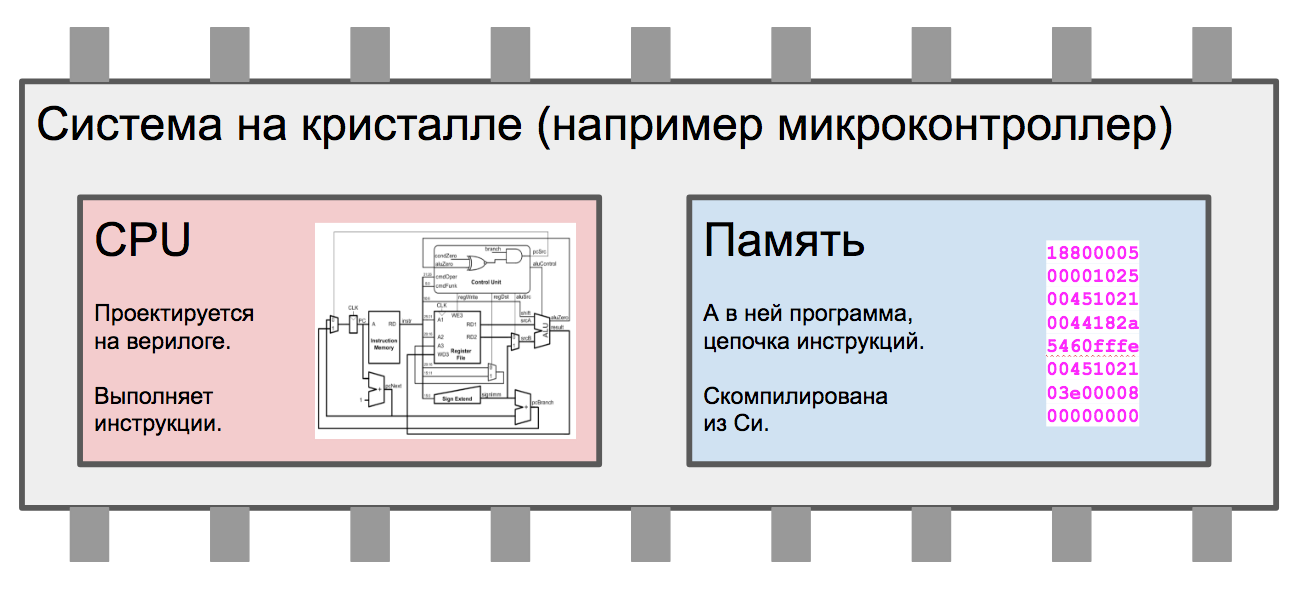

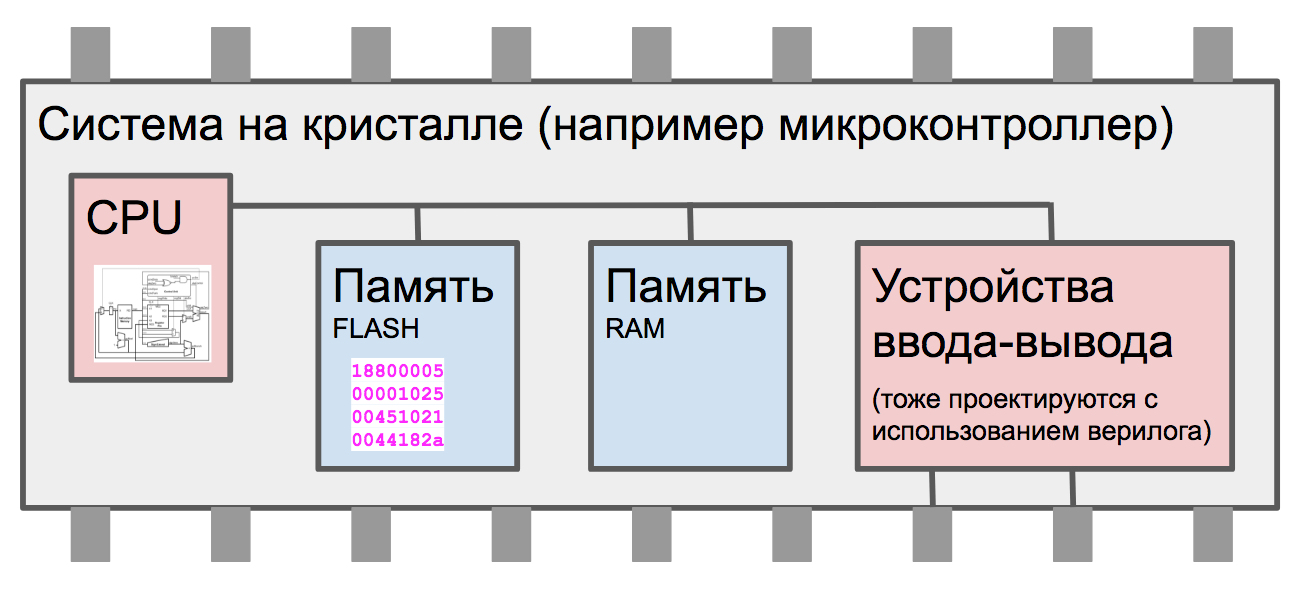

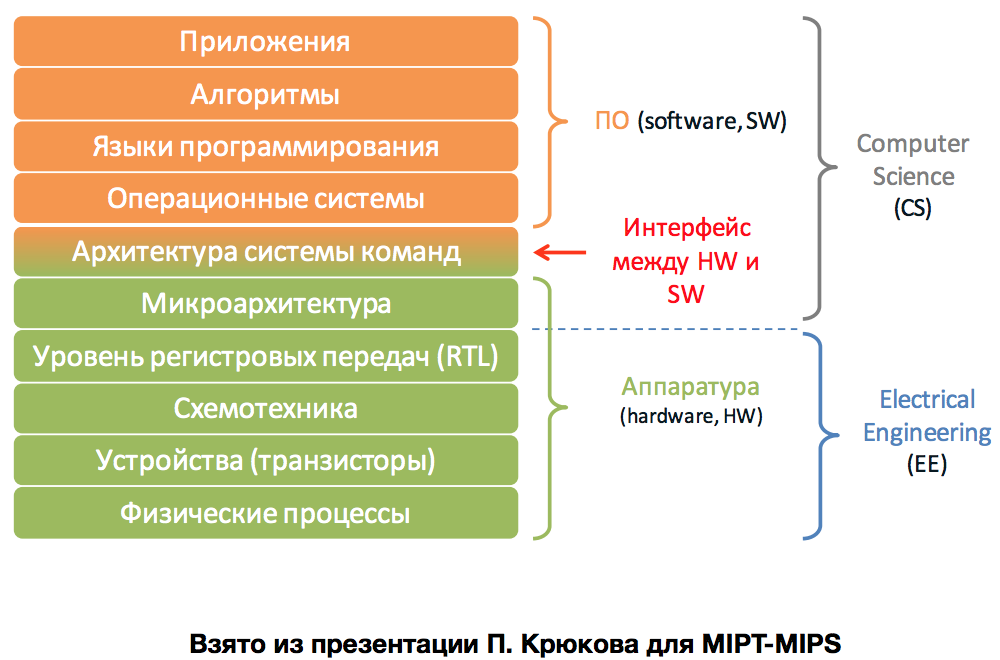

В любом серьезном современном электронном устройстве есть аппаратно-программный дуализм:

На языках описания аппаратуры проектируется не только процессор, но и контроллеры периферийных устройств и их соединения в системе:

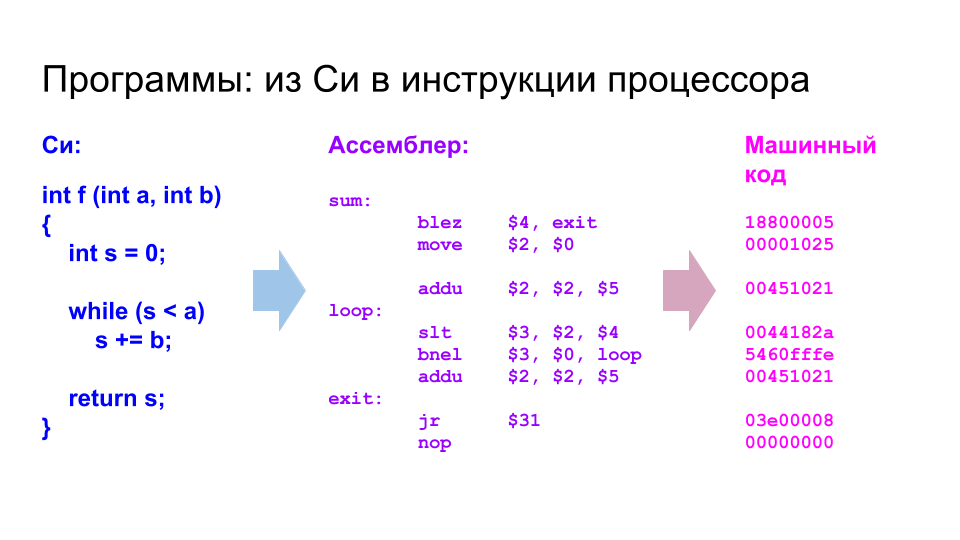

Вы все знаете, как компилируются программы — в инструкции, которые исполняет процессор:

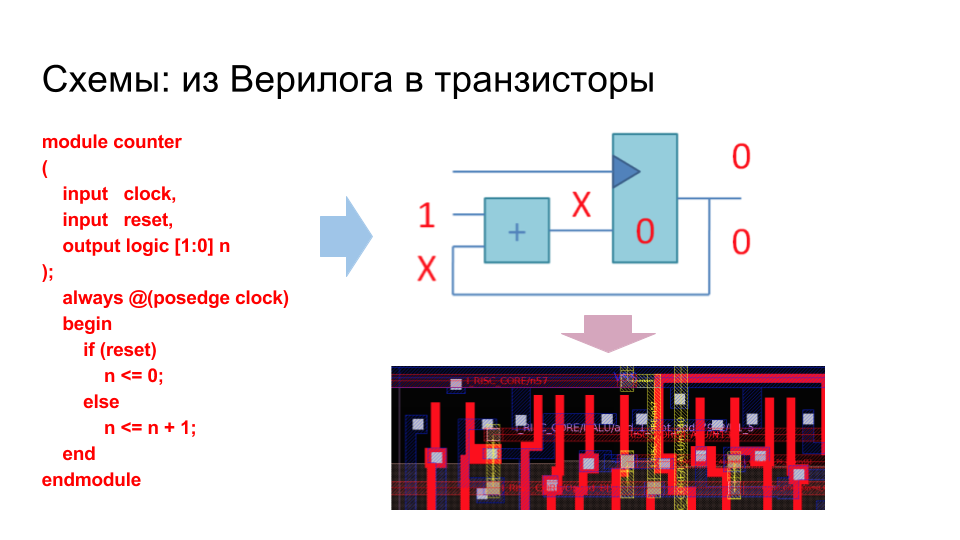

Но вот описания схем на языке описания аппаратуры Verilog компилируются (синтезируются) не в инструкции, а в схемы. Как частный случай — в схему процессора который берет из памяти и выполняет инструкции. В конечном итоге описание на верилоге превращается в дорожки и транзисторы микросхемы. Это не «микрокод», честно («микрокод» — это о другом). Поэтому говорить «программирование на верилоге» не вполне корректно, это как говорить «программирование на HTML» Программы — это цепочки инструкций для фон-нейманновской машины, а не схемы (хотя верилог можно использовать и для программирования, как на самолете ездить по шоссе). Корректно говорить «проектировать схемы на верилоге на уровне регистровых передач» или просто «писать код на верилоге».

Теперь перейдем к событию в Томске. Идея сделать семинар по разработке цифровых микросхем родилась в декабре 2016 года вот за этим столом в пивной посередине Silicon Valley, Калифорния. Физик/химик Анатолий Коркин (второй слева) изначально планировал сделать в Томске чисто конференцию для физиков и химиков, в том числе тех, кто создает технологии производства в полупроводниковвой промышленности. Сам Анатолий в свое время работал в компании Motorola в Аризоне, а некоторые из его коллег, которых он пригласил на конференцию, разрабатывали технологии производства микросхем памяти.

Проблема в том, что физики без программистов сами компьютерную систему не построят. Хуже того — физики не построят эту систему и с программистами. Чтобы компьютер или гаджет работал, между физикой и программированием должен быть мост из цепочки технологий, в которые входит микроархитектура, логическое проектирование аппаратуры на уровне регистровых передач (register transfer level — RTL), автоматизация проектирования с помощью логического и физического синтеза (logic synthesis, floorplanning, place & route). Поэтому Анатолий встретился с преподавателем из Университета Калифорнии Чарльзом Данчеком, который в прошлом году прочитал очень популярные лекции в МИСиСе с обзором цепочки проектирования микросхем (первый слева), а также менеджером AMD Тимуром Палташевым (первый справа), и вашим покорным слугой. И было решено семинар в Сибири делать (хотя Тимур и Чарльз смогли участвовать только дистанционно).

Томск оказался визуально интересным городом, с уютным центром и большим количеством зданий, сильно отличающихся от архитектуры Silicon Valley:

В городе высокий процент жителей — студенты, так как в Томске находится несколько университетов, в том числе Томский государственный университет (в нем мы проводили семинар), Томский политехнический университет (из него к нам приходили слушатели) и Томский университет систем управления и радиоэлектроники (ТУСУР), из которого к нам приходили слушатели:

В первый день студентов учили Никита Поляков из МЦСТ и МФТИ (с бородой слева — он преподавал Verilog) и Илья Кудрявцев из Самарского университета (с бородой справа — он преподавал VHDL). VHDL — это тоже язык описания аппаратуры, его любят военные всех стран и некоторые группы некоторых компаний (Texas Instruments, IBM, Imagination Technologies). PoverVR внутри Apple iPhone написан на VHDL.

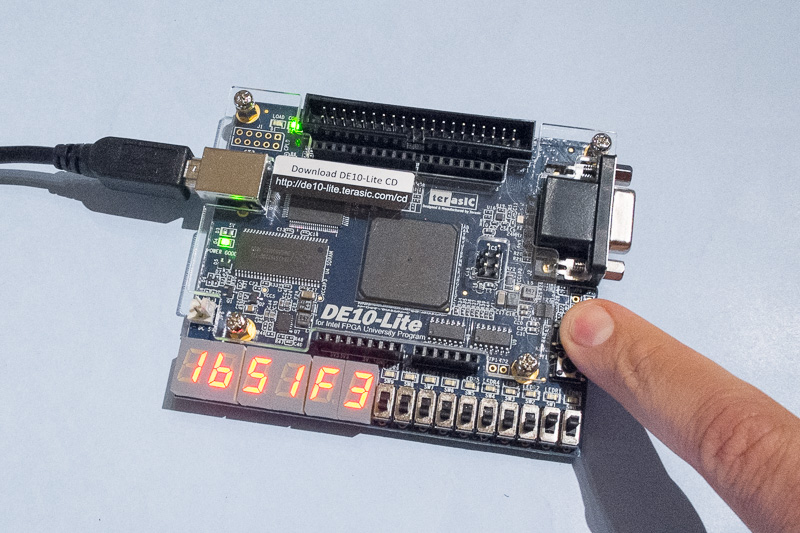

Обратите внимание что у студентов на столах лежат вот такие платы:

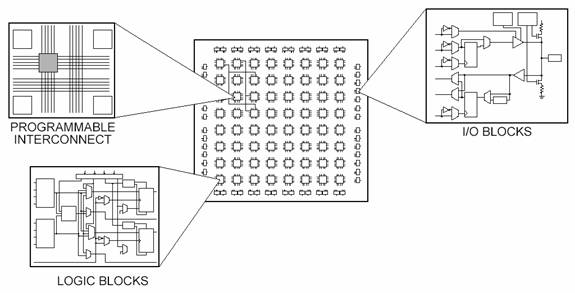

Центральный чип на этой плате — это микросхема «изменяющегося железа» ПЛИС (Программируемая Логическая Интегральная Схема) или по английски FPGA (Field Programmable Gate Array). ПЛИС / FPGA — матрица из ячеек с изменяемой логической функцией. Одна ячейка может стать И, другая — ИЛИ, третья — битом памяти. В этом ПЛИС нет процессора, но его можно создать на лету, с помощью изменения содержимого специальной конфигурационной памяти, биты которое подсоединены к мультиплексорам, которые меняют функцию ячейки:

На совещании в другой комнате было интересно наблюдать, что когда речь заходит об обучении электронике, у каждого российкого вуза есть собственное лицо:

1. Московский институт электронной техники (МИЭТ), как вы видите на фотографии Александра Силантьева с его слайдом ниже, примечателен связями с зеленоградскими электронными компаниями (http://multicore.ru, http://milandr.ru, http://km211.ru), фабриками Микрон и Ангстрем, и окружающими их другими компаниями.

2. Московский физико-технический институт (МФТИ) упирает в процессорную архитектуру и микроархитектуру. Так получилось из-за сотрудничества МФТИ с МЦСТ (разработчиком Эльбрусов) и Интелом.

3. Московский государственный университет (МГУ) акцентирует усилия на алгоритмах для автоматизации проектирования электроники (Electronic Design Automation — EDA).

4. Региональные университеты — Нижегородский НГТУ, Самарский университет (бывший Самарский государственный аэрокосмический университет — СГАУ), Новосибирский НГТУ — смотрят больше не на проектирование чипов, а на системный уровень, предлагая курсы по микроконтроллерам, DSP и FPGA, с ориентацией на спрос со стороны российских производителей оборудования.

Помимо Тимура Палташева от AMD и меня от MIPS, на совещании выступали представители и других компаний-разработчиков, в частности:

1. Сергей Бражников (НПК «Технологический центр») рассказал про их программы для проектирования полузаказных СБИС средствами САПР «Ковчег».

2. Александр Камкин, ведущий научный сотрудник Института системного программирования РАН (ИСП РАН) рассказал про верификацию. Он сделал доклад «Общая методология верификации микропроцессоров: тестовые программы, трассы исполнения, ко-симуляция RTL-модели и модели архитектуры. Автоматизация генерации тестовых программ для микропроцессоров с архитектурой MIPS с использованием инструмента MicroTESK».

3. Представители National Instruments рассказали про их средства прототипирования контролирующих устройств, в частности LabVIEW.

Как я уже упомянул, часть докладов на семинаре были удаленные. Чарльз Данчек, автор популярного дистанционного курса от eNano (образовательного отделения РОСНАНО) и Тимур Палташев, менеджер AMD, выступили по скайпу из Калифорнии.

В серой шапке в верхнем ряду стоит Станислав Жельнио, создатель проект schoolMIPS — самого простого RISC процессора во Вселенной.

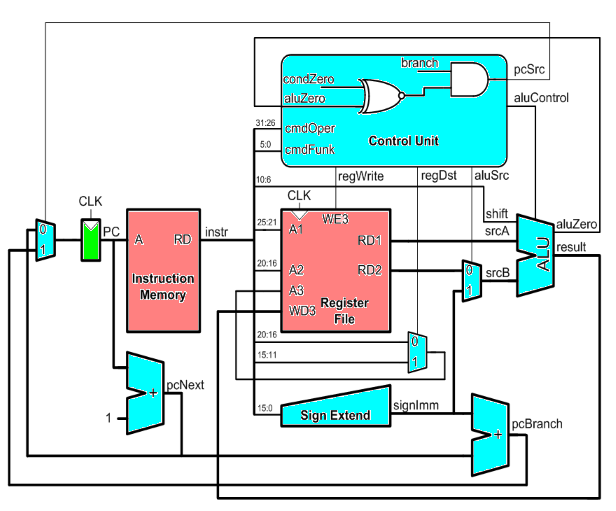

Структуру schoolMIPS могут понять даже школьники, его описание занимает всего несколько сот строк на верилоге. Но при этом на schoolMIPS можно выполнять программы, скомпилированные с помощью стандартной GCC toolchain:

Станислав Жельнио также существенно расширил процессор MIPSfpga — вариант промышленного процессорного ядра MIPS microAptiv UP, бесплатно лицензируемый университетским исследователям для проектов типа создания собственных сопроцессоров и наблюдения работы конвейера. Станислав сейчас ведет проект MIPSfpga+, к которому он добавил контроллер прерываний, интерфейс с внешней памяти SDRAM, и спортировал на него Linux на плате от Altera / IntelFPGA.

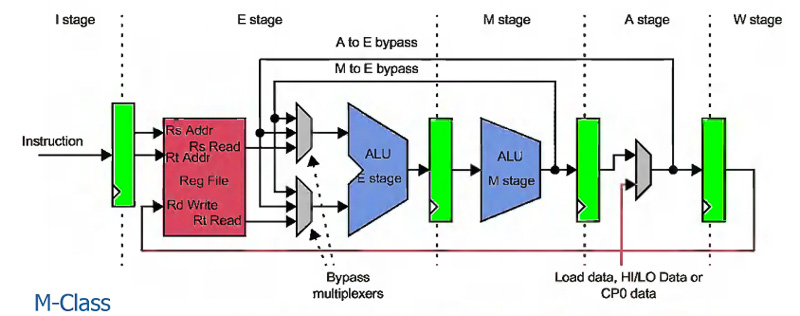

Хотя MIPSfpga считается небольшим экономичным ядром, он в сотни раз больше по количеству строк на верилоге, чем schoolMIPS, реализует полную архитектуру MIPS32 и выполняет инструкции с помощью пятистадийного конвейера с байпасами, включает в себя кэш и устройство управления памятью:

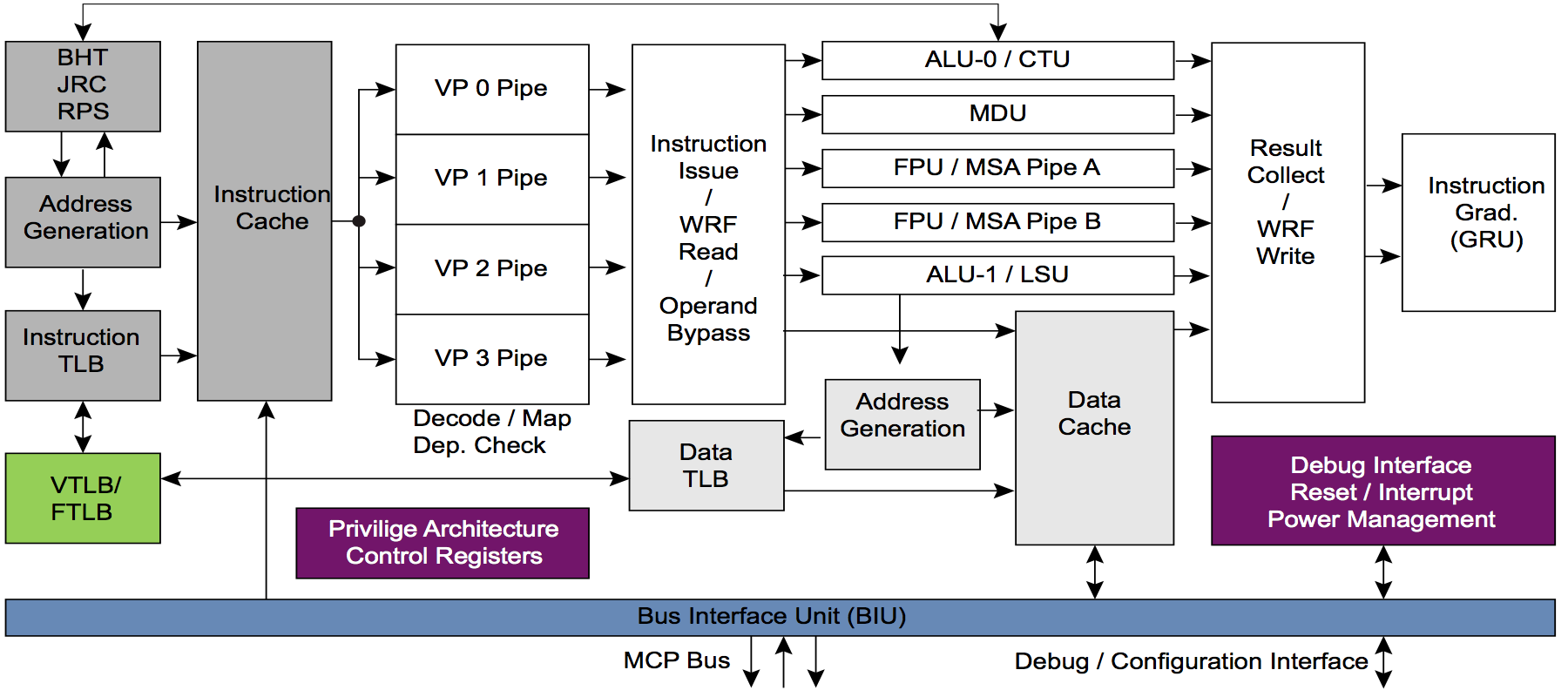

А вот для сравнения конвейер процессорного ядра MIPS I6400, которое содержит еще на порядок больше строк верилога, чем MIPSfpga. 64-битный MIPS I6400 строится вокруг суперскалярного конвейера с аппаратной поддержкой многопоточности и виртуализации, векторными регистрами и интерфейсом с менеджером когерентности, который обеспечивает непротиворечивое состояние кэщей в многоядерной системе.

Вот участники семинара рассказывают про интеграцию schoolMIPS в простейшую систему на кристалле с датчиком освещения:

А вот слева — школьница Даша Криворучко, которая тоже освоила schoolMIPS, а справа — суровая челябинская женщина-химик Катерина Полутина, организаторша конференции:

Вот Даша рассказывает, как она добавила в schoolMIPS инструкцию умножения:

Даша также выступила в томском Лицее номер 8, где рассказала о том, что она делала:

А вот другой школьник, Арсений Чегодаев, показывает свой проект. Он тоже приехал в Томск сделать доклад на специальной секции для школьников, но само видео мы сделали на Летней школе юных программистов в Новосибирске:

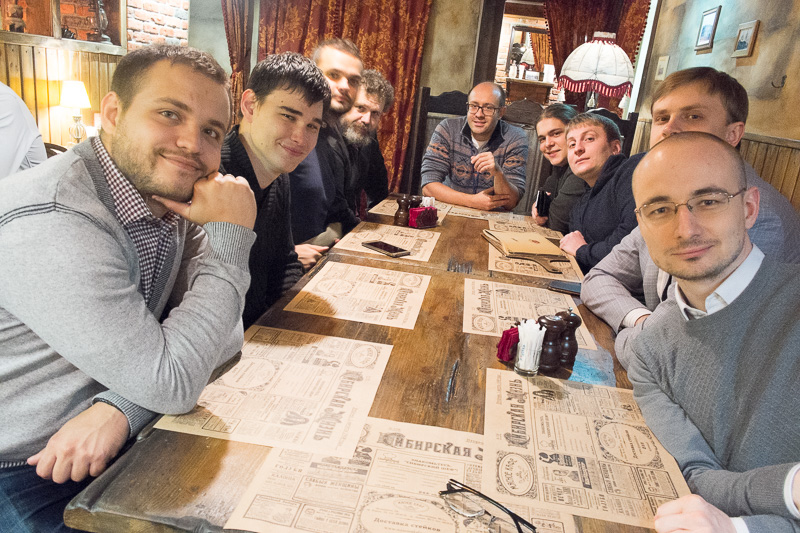

Под конец наша компания докладчиков и преподавателей на семинаре обедала в утонченных ресторанах сибирской кухни:

в которых есть строганая рыба, мороженые таежные ягоды и другие местные деликатесы:

Серия коротких нередактированных видео с телефона совещания и курсов с телефона:

Длинные нередактированные записи всего:

Вердикт: Томск — отличное место для устройства совещаний преподавателей, выездных сессий по мозговому штурму и других подобных мероприятий. Это возможность сменить обстановку для москвичей и питерцев, а коллекция музеев (краеведческий с кулайской культурой, музей ГУЛАГа и другие) интересны в том числе для гостей из Silicon Valley и других далеких мест. Туда хочется вернуться. Серьезный центр разработки микроэлектроники будет в Томске не скоро, но в вузах там уже используют учебник Харрис & Харрис, люди там умные, так что возникновение там такого очага возможно и является вопросом количества приложенных усилий.

Самый крупный пробел в текущих российских программах обучения микроэлектронике, который я заметил — это жесткая нехватка материалов и преподавателей по верификации (unit-level и system-level) с использованием SystemVerilog, coverage-based constrained-random, assertions, formal итд — без этой группы технологий реальных чипов не сделать.

После Томска был Новосибирск, где прошел двухдневный семинар / хакатон учеников десятка (или больше?) новосибирских лицеев под руководством Татьяны Колесниковой, заведующей технопарка для школьников. Сам технопарк находится в здании, которое жители новосибирского академгородка называют «Гуси». Там есть также ресторан «Гуси»:

Вот фото этого здания из ЖЖ (мои фотки этого здания менее впечатляющи):

На входе был плакат с изображением сурового сибирского мужика:

Семинар и хакатон для школьников состоял из двух частей — упражнения с микросхемами малой степени интеграции и упражнения с ПЛИС / FPGA. Для упражнений с ПЛИС в качестве основы использовался вот такой набор.

Микросхемы малой степени интеграции (мы использовали CMOS 4000) — это старый (выпускаются с 1970-х годов), но до сих пор самый наглядный способ показать логические элементы, работу D-триггера и простые счетчики. Это помогает подготовится к работе с ПЛИС и Verilog, так как помогает выстроить в школьника ментальную модель схемы. Иначе школьник отнесется к верилогу как к чему-нибудь типа странной версии Питона, и в результате будет делать неэффективные схемы.

Лекция на семинаре/хакатоне:

Результаты:

- Школьники разобрались с CMOS 4000 менее чем за день, при нехватке времени этот материал можно опустить

- За один день с Verilog можно разобраться только с примером комбинационной логики

- Для последовательностной логики на Verilog нужен второй день или лучше подготовленные примеры

До двухдневного семинара/хакатона в новосибирском академгородске был недельный семинар / хакатон в Киеве и в двухнедельная Летняя школа юных программистов в новосибирской области. Сравнение всех трех семинаров есть в презентации на круглом столе в МГУ, который прошел 8 октября. Вот его материалы. Этот круглый стол организовало eNano, образовательное отделение РОСНАНО.

Следущей остановкой после Новосибирска был Назарбаевский университет в Астане, Республика Казахстан. С главного входа университет выглядит так:

Заходим вовнутрь:

Работаем с FPGA платами:

Республика Казахстан — довольно интересное место. С одной стороны, это страна, экономика которой построена на природных ресурсах (руды, газ, нефть, уран). С другой стороны, общество Казахстана очень похоже на российское, как в организации государства, так и в уважении к культуре — в Казахстане например хорошие музеи. Вот например в Абу-Даби (через который я летел из Казахстана) общество богаче, но музеи построили (точнее купили) совсем недавно.

Тимур Палташев (который из AMD) рассказывал мне, что в 1970-е годы в казахском политехе были лабораторные работы с созданием микрокода для EC ЭВМ (IBM 360/370), а ближе к современности знакомый Джолдас Джурунтаев (справа) написал приличный курс основ цифровой схемотехники, правда покрывающий только часть области, что сейчас недостаточно:

Но Казахстан сейчас конечно находится на очень ранней стадии развития экосистемы в микроэлектронной области. Менеджмент Назарбаевского университета (в котором есть люди из МФТИ) и другие казахские организации сейчас ломают голову, как бы оптимизировать развитие. Они пригласили нескольких преподавателей из-за рубежа, которые знакомы с тематикой VLSI. Преподаватели ввели курс по VHDL и сейчас начинают вводить лабы на FPGA. Они живут в качественном квартирном комлексе при университете, который похож на отель долговременного проживания Marriott Residence Inn.

В Назарбаевском университете была девушка (жаль, что я забыл ее сфотографировать) которая делает прибор для сбора информации с телескопа с использованием обработки информации на ПЛИС / FPGA.

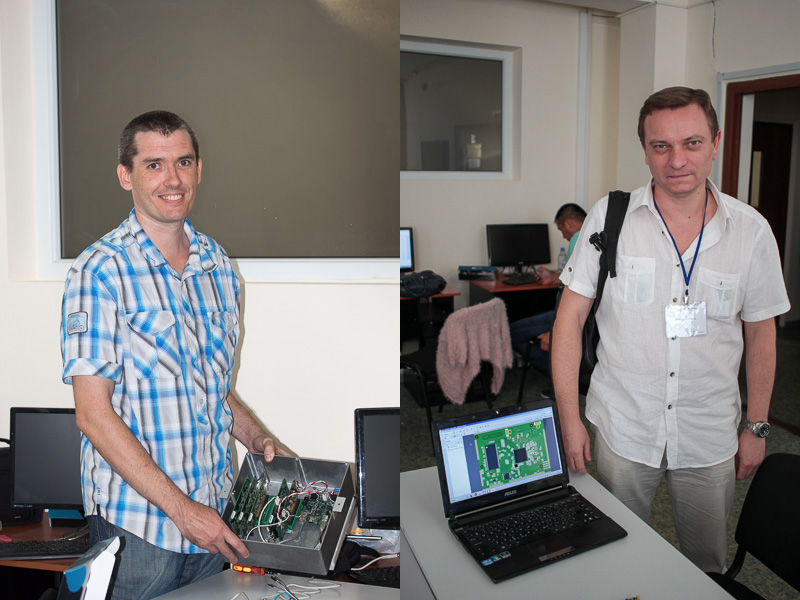

В университете также пытаются распостранить культуру мейкерства среди жителей Казахстана и думают, как наладить кооперацию с местными казахскими компаниями. Такие компании есть. Например есть производитель коммутаторов Элтекс Алатау, или вот эти два джентельмена: слева Константин Малишич с спроектированным в Казахстане сейсмоанализаторе, на основе нескольких микроконтроллеров и встроенных процессоров, а справа Владимир Махонин — разработчик сети устройств, которые носят казахские шахтеры. У Владимира Махонина есть идея сделать первый в Казахстане ASIC (в сотрудничестве с российскими коллегами в Зеленограде):

Под конец, для закрепления материала, покажу еще два слайда с теорией — из презентации Амира Аюпова, российского инженера, который работает в Интеле в Санта-Клара, Калифорния, где занимается моделированием микроархитектуры интеловских процессоров и анализом их производительности. В октябре мы с Амиром сделали совместную лекцию по скайпу для повышения боевого духа студентов Самарского университета, по просьбе их декана Ильи Кудрявцева, одного из участников семинара в Томске. Лекция со всеми слайдами двух презентаций и звуком лежит здесь. Эти слайды Амир взял из презентации его коллеги, преподавателя МФТИ Павла Крюкова:

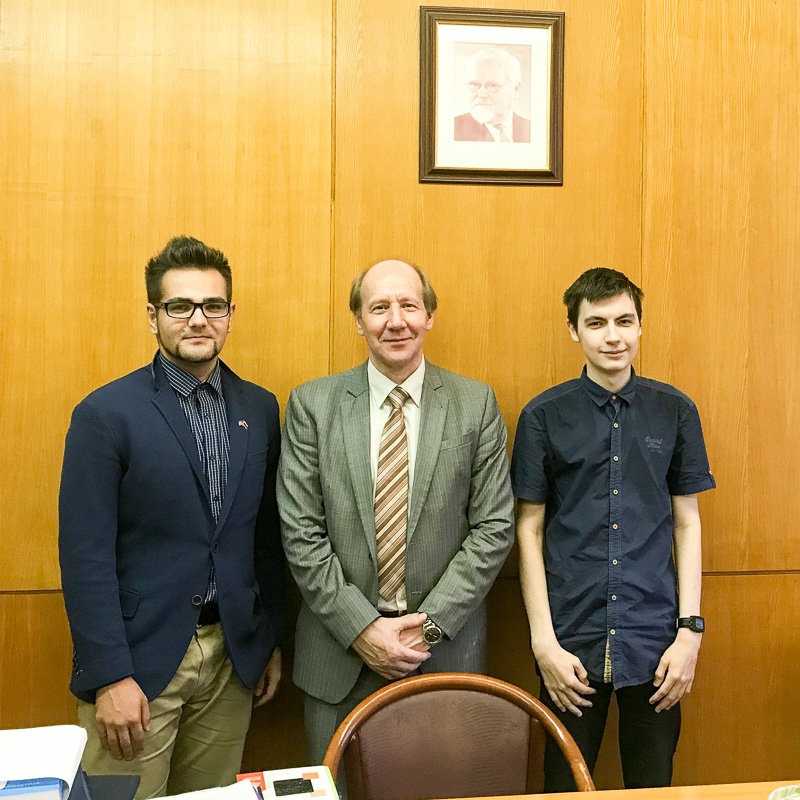

В сентябре Амир заходил в ВМК МГУ, где сейчас быстро развивают лабы с Verilog и FPGA даже спроектровали свое небольшое MIPS-совместимое процессорное ядро для образовательных целей. Вот Амир (слева) вместе с замдекана ВМК МГУ Сергеем Ложкиным и студентом ВМК Владимиром Жуковым.

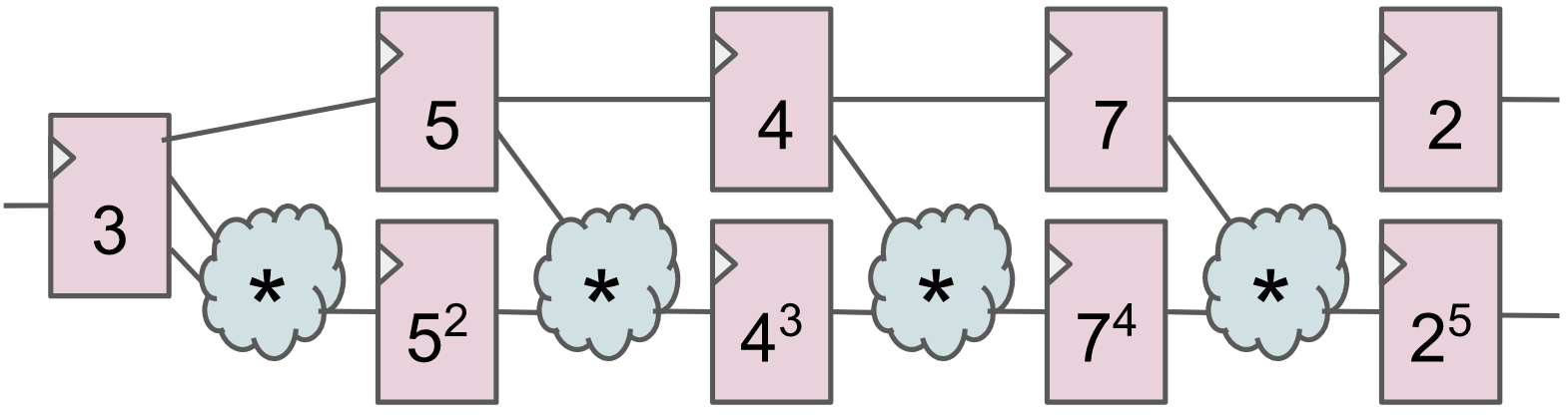

К чему я привел Амира и сотрудников ВМК МГУ: мы с ними, а также с участниками семинара в Томске, все совместно работаем над методическими пособиями по Verilog и FPGA, с целью сделать пособие, превосходящее например материалы курса из MIT. По этому поводу мы будем встречаться в этот понедельник 25 января в МГУ, потом возможно будет еще одна встреча в Питере, тоже во время предновогодней недели. Впереди новогодние каникулы, во время которых многие участники данного проекта будут писать эти лабы. Вот картинка из лабы по принципам конвейерной обработки, код для которой мы держим на гитхабе (но не текст — текст появится, когда все все напишут и начнется бета-тестирование курса):

Резюме: Следующий этап развития экосистемы электроники — расширение. Для России недостаточно иметь всего несколько команд по разработке специализированных микросхем для внутреннего рынка. Чтобы все стало как в Silicon Valley, университетам необходимо выпускать на порядок больше молодых инженеров, которые бы владели навыками разработки логических блоков на языках описания аппаратуры Verilog и VHDL, использования софтвера для физического проектирования типа Synopsys IC Compiler и Cadence Innovus, знанием алгоритмов для создания собственных российских программ для автоматизации проектирования микросхем и т.д. Первые шаги в область проектирования умных чипов с помощью методологии регистровых передач (register transfer level — RTL) могут делать уже продвинутые ученики физматшкол, с помощью проектов с изменяемым железом на основе микросхем ПЛИС / FPGA (Field Programmable Gate Arrays).

После встреч в Москве и Питере — продолжение следует.

Автор: Юрий Панчул