Linux Foundation займется open source чипами

Linux Foundation открыли новое направление — CHIPS Alliance. В рамках этого проекта организация будет развивать свободную систему команд RISC-V и технологии для создания процессоров на её основе. Расскажем подробнее, что происходит в этой сфере.

[1]

[1]

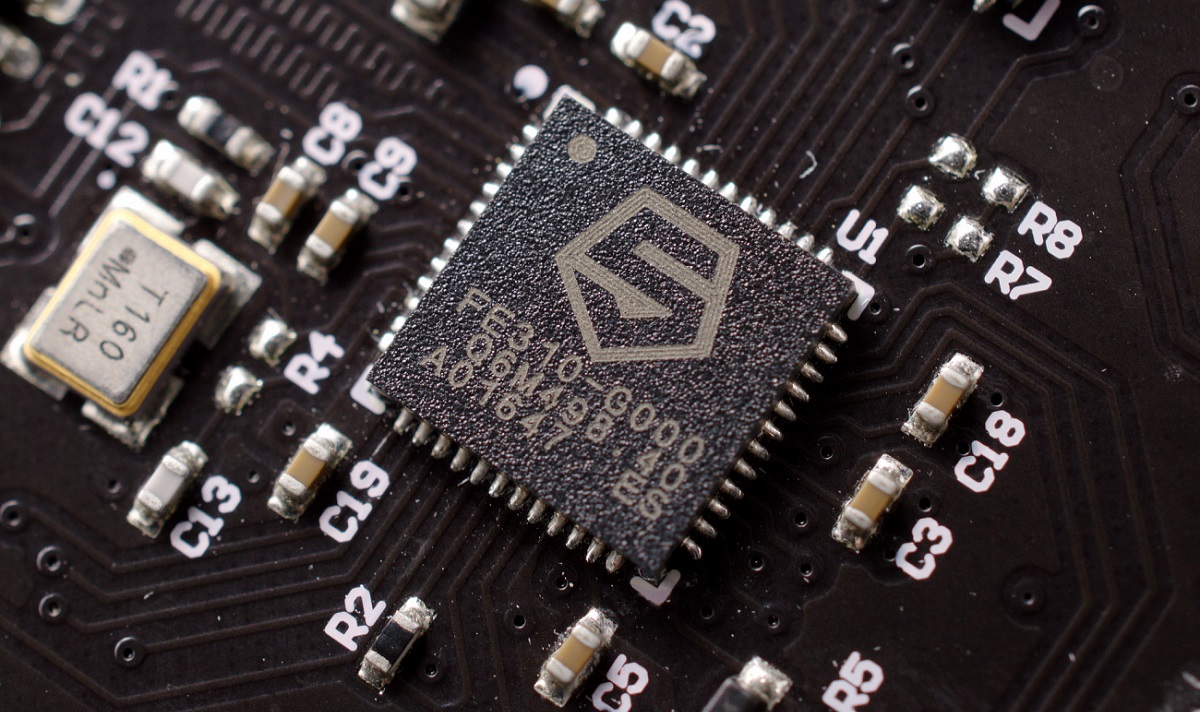

/ фото Gareth Halfacree [2] CC BY-SA [3]

Почему появился CHIPS Alliance

Патчи, защищающие от Meltdown и Spectre, в некоторых случаях снижают производительность [4] серверов на 50%. При этом все еще появляются новые вариации уязвимостей, связанные со спекулятивным выполнением команд. Об одной из них стало известно в начале марта [5] — специалисты по ИБ окрестили её Spoiler. Эта ситуация влияет на обсуждение [6] необходимости пересмотра существующих аппаратных решений и подходов к их разработке. В частности, Intel уже готовят [7] новую архитектуру для своих процессоров, не подверженную Meltdown и Spectre.

Не остались в стороне и в Linux Foundation. Организация запустила собственную инициативу — CHIPS Alliance — участники которой займутся развитием процессоров на базе RISC-V.

Какие проекты уже разрабатывают

В списке участников CHIPS Alliance — Google, Western Digital (WD) и SiFive. Каждая из них представила свои собственные разработки. Расскажем о некоторых из них.

RISCV-DV

Поисковый ИТ-гигант передал в open source платформу для тестирования процессоров на базе RISC-V. Решение случайным образом генерирует [8] команды, которые позволяют [9] проверить работоспособность устройства: тестируют процессы перехода, стека вызовов, CSR [10]-регистры и др.

Например, вот так выглядит класс [11], отвечающий за проведение простого теста арифметических инструкций:

class riscv_arithmetic_basic_test extends riscv_instr_base_test;

`uvm_component_utils(riscv_arithmetic_basic_test)

`uvm_component_new

virtual function void randomize_cfg();

cfg.instr_cnt = 10000;

cfg.num_of_sub_program = 0;

cfg.no_fence = 1;

cfg.no_data_page = 1'b1;

cfg.no_branch_jump = 1'b1;

`DV_CHECK_RANDOMIZE_WITH_FATAL(cfg,

init_privileged_mode == MACHINE_MODE;

max_nested_loop == 0;)

`uvm_info(`gfn, $sformatf("riscv_instr_gen_config is randomized:n%0s",

cfg.sprint()), UVM_LOW)

endfunction

endclass

По словам [9] разработчиков, платформа отличается от аналогов тем, что позволяет последовательно проверить все компоненты чипа, включая блок памяти.

Протокол OmniXtend

Это сетевой протокол от WD, обеспечивающий когерентность кэша при передаче данных поверх Ethernet. OmniXtend [12] позволяет обмениваться сообщениями напрямую с кэшем процессора и используется для подключения разного рода ускорителей: GPU или FPGA. Он также подходит для создания систем на базе нескольких чипов RISC-V.

Протокол уже поддерживается чипами SweRV [13], ориентированными на обработку данных в дата-центрах. SweRV — это 32-разрядный двухконвейерный суперскалярный процессор, выполненный по 28-нанометровому техпроцессу. Каждый конвейер имеет девять уровней, что дает возможность загружать и исполнять несколько команд одновременно. Устройство работает на частоте 1,8 ГГц.

Генератор Rocket Chip

Решение от компании SiFive, которую основали разработчики технологии RISC-V. Rocket Chip [14] — это генератор ядер процессора RISC-V на языке Chisel. Он представляет собой [15] набор параметризованных библиотек, которые используются для создания SoC [16].

Что касается Chisel [17], то это язык описания аппаратуры, основанный на Scala. Он генерирует низкоуровневый код на Verilog, который подходит [18] для обработки на ASIC и FPGA. Таким образом, он позволяет использовать принципы ООП при разработке RTL [19].

Перспективы альянса

Эксперты говорят, что инициатива Linux Foundation сделает рынок процессоров более демократичным и открытым для новых игроков. В IDC отмечают [20], что рост популярности таких проектов положительно скажется на развитии технологий машинного обучения и систем ИИ в целом.

/ фото Fritzchens Fritz [21] PD

Развитие open source процессоров также позволит снизить стоимость проектирования кастомных чипов. Однако это произойдет только в том случае, если сообществу Linux Foundation удастся привлечь достаточное количество разработчиков.

Аналогичные проекты

Разработкой проектов, связанной с открытым аппаратным обеспечением, занимаются и другие организации. Примером может быть консорциум CXL, представивший в середине марта стандарт Compute Express Link. Технология является аналогом OmniXtend и также связывает CPU, GPU, FPGA. Для обмена данными стандарт использует шину PCIe 5.0.

Еще один проект, занимающейся развитием процессорных технологий, — MIPS Open, который появился в декабре 2018 года. Инициативу создал стартап Wave Computing. Разработчики планируют открыть [22] для ИТ-сообщества доступ последним 32- и 64-разрядным наборам команд MIPS. Старт проекта ожидается [23] в ближайшие месяцы.

В целом open source подход становится общепринятым не только для ПО, но и для железа. Подобные проекты поддерживают крупные компании. Поэтому можно ожидать, что уже в ближайшем будущем на рынке появится больше устройств, в основе которых лежат открытые аппаратные стандарты.

Свежие посты из нашего корпоративного блога:

- Что нужно знать о PCI DSS: обзор стандарта [24]

- Мир до и после. Как изменилась жизнь с наступлением DNS Flag Day [25]

- Послеаварийное восстановление как услуга: что нужно знать [26]

Посты из нашего Telegram-канала:

- Как управлять железом в дата-центре — две новые технологии [27]

- Как IaaS-провайдер защищает данные клиентов [28]

- Зачем VMware vSphere понадобился HTML5-клиент? [29]

Автор: ИТ-ГРАДовец

Источник [30]

Сайт-источник PVSM.RU: https://www.pvsm.ru

Путь до страницы источника: https://www.pvsm.ru/open-source/312248

Ссылки в тексте:

[1] Image: https://habr.com/ru/company/it-grad/blog/444664/

[2] Gareth Halfacree: https://www.flickr.com/photos/120586634@N05/32418936265/

[3] CC BY-SA: https://creativecommons.org/licenses/by-sa/2.0/

[4] снижают производительность: https://www.tomshardware.com/news/linux-spectre-patch-50-percent-performance-penalty,38099.html

[5] стало известно в начале марта: https://arxiv.org/pdf/1903.00446.pdf

[6] обсуждение: https://www.pcworld.com/article/3299477/solving-spectre-and-meltdown-may-ultimately-require-an-entirely-new-type-of-processor.html

[7] уже готовят: https://hackaday.com/2018/12/12/intel-announces-faster-processor-patched-for-meltdown-and-spectre/

[8] генерирует: https://github.com/google/riscv-dv

[9] позволяют: https://content.riscv.org/wp-content/uploads/2018/12/14.25-Tao-Liu-Richard-Ho-UVM-based-RISC-V-Processor-Verification-Platform.pdf

[10] CSR: https://en.wikipedia.org/wiki/Control/Status_Register

[11] вот так выглядит класс: https://github.com/google/riscv-dv/blob/master/test/riscv_instr_test_lib.sv

[12] OmniXtend: https://github.com/westerndigitalcorporation/omnixtend

[13] чипами SweRV: https://github.com/westerndigitalcorporation/swerv_eh1

[14] Rocket Chip: https://github.com/freechipsproject/rocket-chip

[15] представляет собой: https://www2.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-17.pdf

[16] SoC: https://ru.wikipedia.org/wiki/%D0%A1%D0%B8%D1%81%D1%82%D0%B5%D0%BC%D0%B0_%D0%BD%D0%B0_%D0%BA%D1%80%D0%B8%D1%81%D1%82%D0%B0%D0%BB%D0%BB%D0%B5

[17] Chisel: https://github.com/freechipsproject/chisel3/

[18] подходит: https://chisel.eecs.berkeley.edu/

[19] RTL: https://ru.wikipedia.org/wiki/%D0%A3%D1%80%D0%BE%D0%B2%D0%B5%D0%BD%D1%8C_%D1%80%D0%B5%D0%B3%D0%B8%D1%81%D1%82%D1%80%D0%BE%D0%B2%D1%8B%D1%85_%D0%BF%D0%B5%D1%80%D0%B5%D0%B4%D0%B0%D1%87

[20] отмечают: https://devops.com/linux-foundation-to-host-chips-alliance-project-to-propel-industry-innovation-through-open-source-cpu-chip-and-soc-design/

[21] Fritzchens Fritz: https://www.flickr.com/photos/130561288@N04/46764481872

[22] открыть: https://wavecomp.ai/mips-open/

[23] ожидается: https://www.sensorsmag.com/embedded/mips-open-advisory-board-open-for-biz

[24] Что нужно знать о PCI DSS: обзор стандарта: https://iaas-blog.it-grad.ru/novosti/chto-nuzhno-znat-o-pci-dss-obzor-standarta/

[25] Мир до и после. Как изменилась жизнь с наступлением DNS Flag Day: https://iaas-blog.it-grad.ru/tendencii/mir-do-i-posle-kak-izmenilas-zhizn-s-nastupleniem-dns-flag-day/

[26] Послеаварийное восстановление как услуга: что нужно знать: https://iaas-blog.it-grad.ru/funkcionalnost/posleavarijnoe-vosstanovlenie-kak-usluga-disaster-recovery-as-a-service/

[27] Как управлять железом в дата-центре — две новые технологии: https://t.me/iaasblog/201

[28] Как IaaS-провайдер защищает данные клиентов: https://t.me/iaasblog/194

[29] Зачем VMware vSphere понадобился HTML5-клиент?: https://t.me/iaasblog/190

[30] Источник: https://habr.com/ru/post/444664/?utm_source=habrahabr&utm_medium=rss&utm_campaign=444664

Нажмите здесь для печати.