Генерация и тестирование ядра RISC-V

Как я писал в прошлом посте [1], название моего проекта на GSoC-2016 — «порт RISC-V на Parallella», и первая вещь, которую я должен был сделать, это познакомиться с экосистемой RISC-V. Один из лучших способов это сделать, — посмотреть видео с презентации первого воркшопа RISC-V на Youtube. Для того, чтобы понять самые важные концепции, я рекомендую следующие презентации:

- Введение (Krste Asanović) видео [2]слайды [3]

- Тулчейн RISC-V (Andrew Waterman) видео [4]слайды [5]

- SoC-генератор RISC-V “Rocket Chip” в Chisel (Yunsup Lee) видео [6] слайды [7]

- Структура программного стека RISC-V (Sagar Karandikar) видео [8]слайды [9]

- Отладка на RISC-V (Albert Ou) видео [10]слайды [11]

- Портирование нового кода на RISC-V с OpenEmbedded (Martin Maas) видео [12] слайды [13]

- Окружение тестирования RISC-V (Stephen Twigg) видео [14] слайды [15]

Ещё одна ссылка [16], если вы интересуетесь Chisel, языком, основанным на Scala, который используется для описания текущей аппаратной реализации ядра RISC-V (ядро Rocket имеет in-order конвейер, BOOM — out-of-order), и любых будущих реализаций.

Краткое руководство по Chisel (Jonathan Bachrach) видео [17]слайды [15]

Работа с Rocket Chip, добавление расширений, инфраструктура ASIC и FPGA (Colin Schmidt) видео [18]слайды [19]

Если вы глубоко заинтересованы в RISC-V и развитии сообщества, я предлагаю вам принять участие в воркшопах [20].

Наш порт RISC-V на Parallella будет использовать совершенно стандартное ядро, сгенерированное с помощью Rocket Chip из исходников на Chisel (в статье [21]даётся очень хорошее введение). Конечным результатом будет Verilog RTL (в нечитаемом виде, только исходники на Chisel читаемы), который мы можем включить в наш проект FPGA для Parallella, который доступен в репозитории [22]Parallella OH (Open Hardware). Однако я не буду вдаваться в подробности сейчас, всё это будет рассмотрено в следующих постах.

Для того, чтобы компилировать ПО для этого ядра, вы можете использовать тулчейн RISC-V GNU, который можно взять здесь [23]. Есть два варианта компиляции: либо с библиотекой Newlib C, которая используется для программ, работающих на прокси-ядре [24] (proxy kernel, pk) либо компилируете с библиотекой GNU C library (glibc), для компиляции Linux и программ под Linux. Я скомпилировал обе версии, (ядро Linux [25], релиз 4.1), используя прилагаемые инструкции, и всё заработало, как ожидалось, при симуляции в Spike [26], референсном симуляторе RISC-V ISA.

Главный репозиторий [27]Rocket Chip связан путём использования субмодулей Git со всеми репозиториями, содержащими исходники (главным образом, Chisel), которые нужны для правильной генерации с использованием своих файлов-обёрток, расположенных в src/main/scala/. Каждый субмодуль связан с определённым комитом, заведомо рабочим, в результате сорка получается стабильной. Лично я не встретил никаких ошибок при генерации дефолтного ядра RV64G (64 бита, [I]nteger, [M]ultiply / Division, [A]tomic, [F] Single Floating, [D]ouble Floating), сокращение IMAFD сокращается до G (General), содержащего L1-кэши инструкций и данных, TLB и FPU с интерфейсами MemIO и HostIO для связи с внешним миром.

В типичной FPGA-системе (как показано на диаграмме из презентации [6]Y.Lee по Rocket Chip), эти два интерфейса нужны для доступа к основной памяти и для загрузки ядра RISC-V (бутстрап). Последний используется для управления CSR (control-status registers) и поддержки системных вызовов (для операций ввода-вывода) из целевой машины (на которой запущено прокси-ядро или ядро Linux) в хост-машину (т.е. в двухядерный процессор ARM в Zynq FPGA), на которой запущен инстанс riscv-fesvr [28] (front end server) для диспетчеризации системных вызовов в операционную систему (т.е. ARM Linux).

Для конфигурирования ядра вы можете также изменить значения внутри файла Config.scala [29]. Этот файл содержит набор конфигураций для различных применений (модель C++, FPGA обычного размера, маленькая FPGA, VLSI, и т.д.). Всё, что делает скрипт, принимающий переменную CONFIG=XXX (т.е. DefaultFPGAConfig), это устанавливает требуемую конфигурацию, используемую для сборки симулятора C++ либо Verilog RTL для FPGA или VLSI. Это очень полезная вещь, если вы хотите экспериментировать с разными доступными опциями, быстро генерировать и тестировать их в программном либо аппаратном виде.

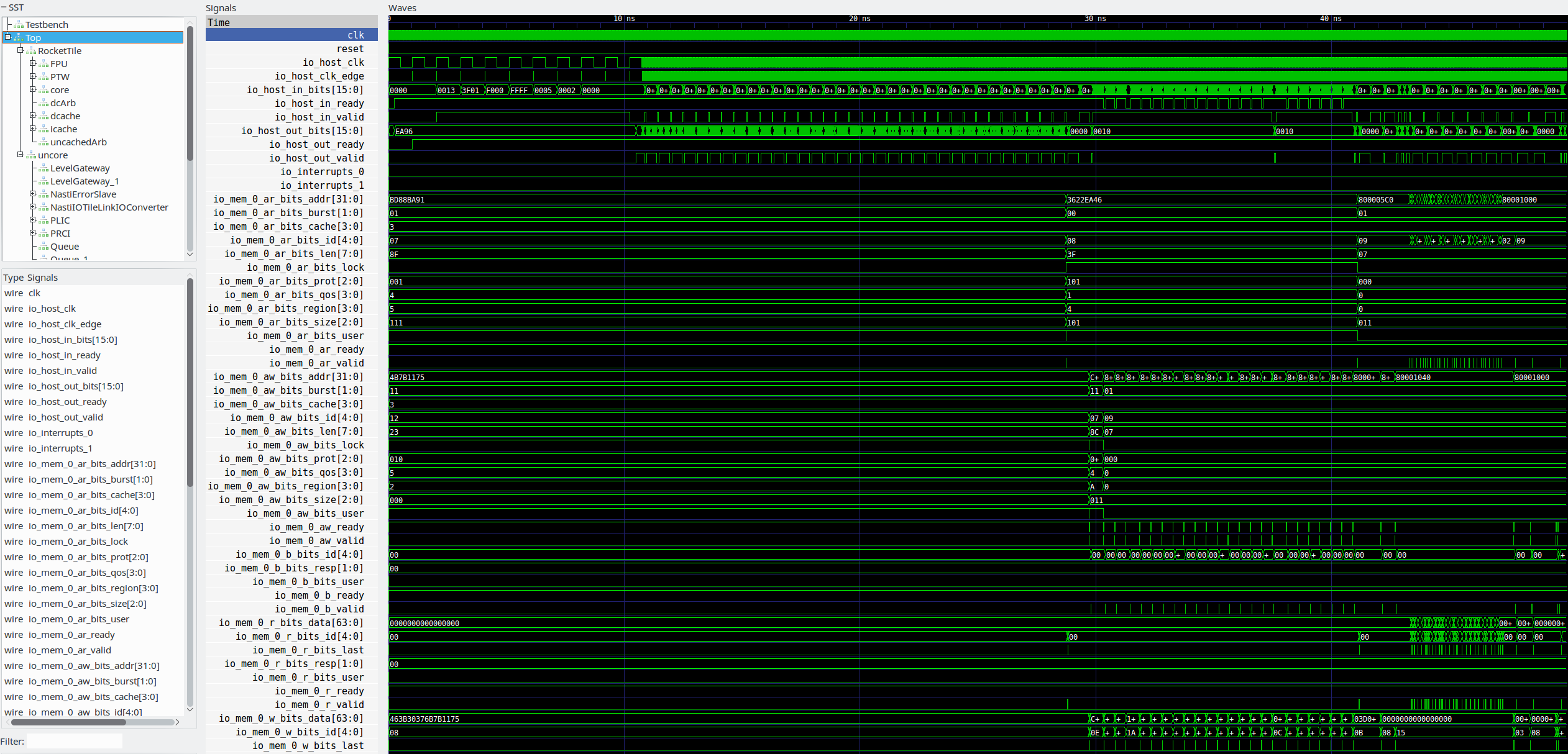

Хорошей идеей является скомпилировать тулчейн (с Newlib лучше всего), прежде чем генерировать любые ядра, так как вам нужно компилировать и запускать тесты для верификации вашего ядра с помощью симулятора C++ или Synopsys VCS. К сожалению, я смог использовать только первый, но не последний. Вы не можете использовать любой симулятор Verilog (например, Verilator, Icarus Verilog, Modelsim, QuestSim), так как тестбенч использует функции DirectC (связывающие тестбенчи Verilog и произвольный код C/C++). К счастью, симулятор С++ обеспечивает вывод VCD и я смог использовать GTKWave для просмотра сгенерированных временных диаграмм тестов.

Я также добавил сессию с простыми командами, нужными для сборки тулчейна RISC-V и генерации ядра RV64G для FPGA. Эти команды будут добавлены в финальный скрипт компиляции, который я разрабатываю для полной автоматизации всего необходимого для того, чтобы получить рабочее ядро RISC-V внутри чипа Zynq на Parallella.

# Скачиваем и инициализируем репозиторий Rocket Chip

git clone https://github.com/ucb-bar/rocket-chip.git

cd rocket-chip

git submodule update --init

export TOP=$(pwd)

# Устанавливаем необходимые пакеты (Ubuntu)

sudo apt-get install autoconf automake autotools-dev curl

libmpc-dev libmpfr-dev libgmp-dev gawk build-essential bison flex

texinfo gperf libtool patchutils bc

# Компилируем тулчейн RISC-V (используется Newlibдля работы без ОС)

export RISCV=$TOP/riscv-tools

# Добавляем всё, что будет скомпилировано, в пути)

export PATH=$PATH:$RISCV/bin

cd $RISCV

git submodule update --init --recursive

# Редактируем файл build.common

# JOBS = Количество ядер / потоков, которые поддерживает ваша машина

./build.sh

# Тестируем тулчейн RISC-V, скомпилировав простую программу

# и запускаем её на Spike (симулятор ISA)

# с использованием имеющегося прокси-ядра (pk)

cd $TOP

echo -e '#include <stdio.h>n int main(void)

{ printf("Hello world!\n"); return 0; }' > hello.c

riscv64-unknown-elf-gcc -o hello hello.c

spike pk hello

# Опционально: компилируем эмулятор Rocket Chip

# Заменить -j8 на -jN (количество ядер/потоков на вашей машине)

cd $TOP/emulator

make

# Запускаем тесты (внимание: это может занять некоторое время)

# make -j8 run-asm-tests

# make -j8 run-bmark-tests

# лучше просто запустить конкретный тест:

make output/rv64ui-p-add.out

# Опционально: компилируем эмулятор Rocket Chip с выводом VCD

# Меняем -j8 на -jN

cd $TOP/emulator

# Если у вас нет утилиты vcd2vpd, открываем src/main/scala/Testing.scala

# файл и меняем все .vpd на .vcd (6 раз)

make debug

# Запускаем тесты (внимание: это может занять время и место на диске)

# make -j8 run-asm-tests-debug

# make -j8 run-bmark-tests-debug

# запускаем определённые тесты и тогда нам не нужен приведённый выше

# хак при отсутствии утилиты vcd2vpd:

make output/rv64ui-p-add.vcd

# Генерируем Rocket Chip Verilog RTL для FPGAs (в fsim/generated-src/)

# Дефолтная конфигурация "DefaultFPGAConfig", но вы не можете её изменить

# например, на "SmallFPGAConfig" если дефолтная реализация с FPU

# не влезает в ваше устройство. Используем make CONFIG=ConfigName verilog для установки

# желаемой конфигурации из числа доступных (src/main/scala/Configs.scala)

# Финальный вывод Verilog RTL называется Top.ConfigName.v

cd $TOP/fsim

make verilogВ следующем посте мы рассмотрим, как получить IP-блок из сгенерированного ядра RV64G для того, чтобы его можно было легко подключать к проектам, для тестирования на Zedboard или для использования в большом проекте на Parallella.

Автор: Владимир

Источник [31]

Сайт-источник PVSM.RU: https://www.pvsm.ru

Путь до страницы источника: https://www.pvsm.ru/open-source/277465

Ссылки в тексте:

[1] прошлом посте: http://eliaskousk.teamdac.com/entry/welcome

[2] видео : https://www.youtube.com/watch?v=A5kpo_ff98M&feature=youtu.be

[3] слайды: https://riscv.org/wp-content/uploads/2015/01/riscv-intro-workshop-jan2015.pdf

[4] видео : https://www.youtube.com/watch?v=XSyH9T-Cj4w&feature=youtu.be

[5] слайды: https://riscv.org/wp-content/uploads/2015/01/riscv-software-toolchain-workshop-jan2015.pdf

[6] видео: https://www.youtube.com/watch?v=Ir3h3qWcNlg&feature=youtu.be

[7] слайды: https://riscv.org/wp-content/uploads/2015/01/riscv-rocket-chip-generator-workshop-jan2015.pdf

[8] видео : https://www.youtube.com/watch?v=2T3eRndwcr0&feature=youtu.be

[9] слайды: https://riscv.org/wp-content/uploads/2015/01/riscv-software-stack-bootcamp-jan2015.pdf

[10] видео : https://www.youtube.com/watch?v=sIfG4C936rA&feature=youtu.be

[11] слайды: https://riscv.org/wp-content/uploads/2015/01/riscv-debugging-bootcamp-jan2015.pdf

[12] видео: https://www.youtube.com/watch?v=0xfDcckQfGM&feature=youtu.be

[13] слайды: https://riscv.org/wp-content/uploads/2015/01/riscv-poky-bootcamp-jan2015.pdf

[14] видео: https://www.youtube.com/watch?v=mbyb7BgYyXg&feature=youtu.be

[15] слайды: https://riscv.org/wp-content/uploads/2015/01/riscv-testing-frameworks-bootcamp-jan2015.pdf

[16] ссылка: https://chisel.eecs.berkeley.edu/

[17] видео : https://www.youtube.com/watch?v=pfM1WUWbfBs&feature=youtu.be

[18] видео : https://www.youtube.com/watch?v=64nsYJJqNvI&feature=youtu.be

[19] слайды: https://riscv.org/wp-content/uploads/2015/01/riscv-rocket-chip-tutorial-bootcamp-jan2015.pdf

[20] воркшопах: https://riscv.org/workshops/

[21] статье : https://www2.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-17.html

[22] репозитории : https://github.com/parallella/oh

[23] здесь: https://github.com/riscv/riscv-tools

[24] прокси-ядре: https://github.com/riscv/riscv-pk

[25] ядро Linux: https://github.com/riscv/riscv-linux

[26] Spike: https://github.com/riscv/riscv-isa-sim

[27] репозиторий : https://github.com/freechipsproject/rocket-chip

[28] riscv-fesvr: https://github.com/riscv/riscv-fesvr

[29] Config.scala: https://github.com/freechipsproject/rocket-chip/blob/master/src/main/scala/config/Config.scala

[30] Image: https://habrastorage.org/webt/si/xd/q7/sixdq7bmjtwepsfgp54pb5bztz8.png

[31] Источник: https://habrahabr.ru/post/352928/?utm_source=habrahabr&utm_medium=rss&utm_campaign=352928

Нажмите здесь для печати.