Аппаратные закладки под микроскопом. Обнаружение

Дисклеймер. Много лет в сообществе технических специалистов идёт дискуссия [1] о возможности внедрения троянов в популярные коммерческие микросхемы. К сожалению, в этот чисто технический вопрос вмешиваются политические аргументы: мол, давайте переходить на российские процессоры, потому что в западных чипах закладки! Такой типичный FUD (см. контрпропаганду [2] на Хабре). Кстати, американские коллеги используют такие же аргументы, но против китайских микрочипов. Похоже, политики любят использовать «пугалки» для принятия выгодных решений, ведь искусство политики древнее самого человечества [3].

Хотим ещё раз подчеркнуть: мы исследуем эту тему исключительно в общемировом контексте как важную область микроэлектроники и информационной безопасности. А как используют данные факты ангажированные представители индустрии и политики — пусть останется на их совести.

В прошлой статье [1] мы подробно обсудили классификацию аппаратных бэкдоров и методы их закладки.

Если вкратце, ввести аппаратный бэкдор можно на любом этапе производственного цикла: от проектирования до корпусировки. По мнению некоторых исследователей, самым рискованным является именно этап проектирования (см. статью Hardware Trojans in Chips: A Survey for Detection and Prevention [4], doi: 10.3390/s20185165), а не производства. Дело в том, что внешнему подрядчику (производственной фабрике) не так легко внести изменения в готовый проект, присланный заказчиком. Гораздо легче разместить закладку самому разработчику микросхемы на этапе проектирования, когда проект открыт на экране компьютера в инструменте EDA.

Более того, в таком случае закладку можно внедрить гораздо более скрытно. После скандала с Meltdown и Spectre появилось мнение, что именно на таком уровне мы увидим следующую волну атак. То есть даже после обнаружения бэкдора останется сомнение, а это действительно бэкдор или просто случайная ошибка разработчиков?

▍ Обнаружение

В 2022 году вышло наиболее полное исследование [5], которое суммирует существующие практические данные по реальному обнаружению аппаратных троянов. Если свести к сухому остатку, то обнаружение осуществляется тремя методами:

- тесты формы волны (waveform tests);

- тесты на задержку прохождения сигнала (delay tests);

- проверки на пустоты «заполненной» матрицы.

Так называемые «тесты формы волны» предполагают проверку неизменности сигнала на всех возможных входных и выходных значениях. Вероятно, эту процедуру можно автоматизировать.

Сравнение сигнала до и после внедрения аппаратной закладки (код Verilog [6] дизайна с закладкой и без, проверить можно в EDA Playgrounds [7])

Тесты на задержку работают, потому что каждый логический гейт даёт некоторую произвольную, но известную задержку, так что вставка неавторизованного гейта в проект увеличивает эту задержку настолько, что её можно обнаружить (в определённых границах).

Наконец, тесты на пустоты матрицы исходят из того, что реальные гейты должны находиться в строго определённых областях, чтобы не вносить задержку или не увеличивать энергопотребление.

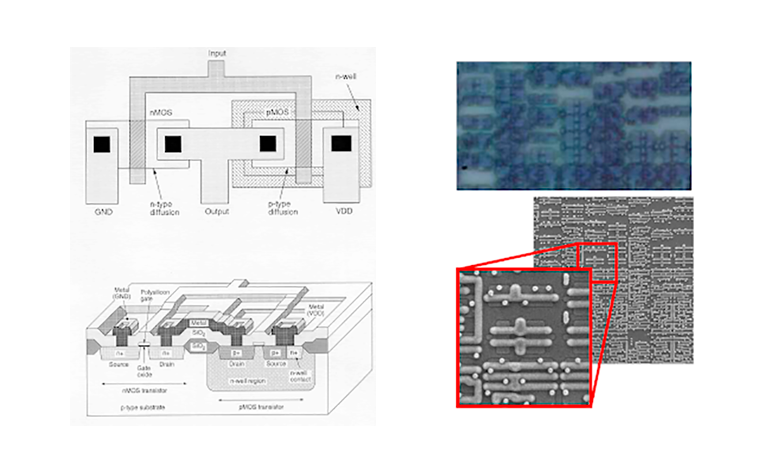

Как мы уже упоминали [1], в качестве защитной меры можно провести полный реверс-инжиниринг, то есть обратную разработку микросхем, анализировать их функциональность, по возможности сравнив с образцом:

Но для сравнения образцов не обязательно выполнять полный реверс-инжиниринг. В некоторых случаях может быть эффективна быстрая проверка с помощью сканирующего туннельного микроскопа.

▍ Сравнение образцов под микроскопом

В 2018 году было опубликовано исследование [8], посвящённое физическим методам выявления аппаратных бэкдоров, то есть с помощью физического осмотра (под микроскопом). Для обнаружения аномалий исследователи применили продвинутые алгоритмы машинного зрения. А непосредственно сканирование выполнялось на сканирующем электронном микроскопе Variomill [9].

Внешний вид установки Variomill

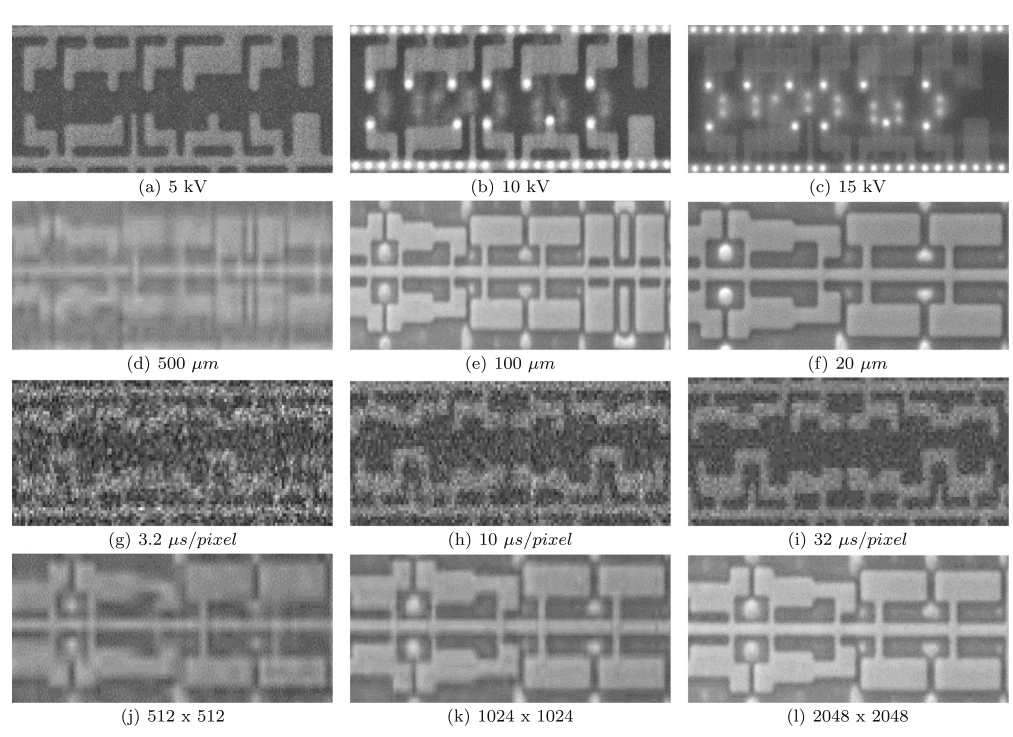

Например, так выглядят элементы микросхемы в установке Variomill с энергией сканирующего луча 5, 10 и 15 кВ (верхний ряд), полем зрения 500, 100 и 20 мкм (второй ряд), скоростью сканирования 3,2 мкм/пиксель, 10 мкм/пиксель и 32 мкм/пиксель (третий ряд), а также с разным разрешением (четвёртый ряд).

Для уточнения заметим, что объектом сканирования выступает микросхема RFID со старой смарт-карты, какие часто производятся по техпроцессу 90–180 нм.

В рамках эксперимента учёные сначала аккуратно модифицировали изображение. Они добавили туда четыре аппаратные закладки. Две из них — путём изменения стандартной цифровой логики в слое легирования, а ещё две — путём добавления абсолютно новых элементов на микросхеме.

Одна из двух закладок, сделанных путём изменения в цифровой логике (NAND → NOR)

Четыре установленных бэкдора (зелёные и синие квадраты). Красным цветом обозначены пустые области на микросхеме

Исследователи проверили, насколько распознаются такие бэкдоры с помощью электронного микроскопа и системы машинного зрения. Обработка изображений начинается с выравнивания, регистрации и очистки от высокочастотного шума (фильтр FFT). Затем повышается контрастность, чтобы лучше выделить детали в области легирования (верхний слой), где находятся значимые признаки, на тёмном фоне подложки. На каждом сегменте изображения приходится адаптивно изменять настройки контрастности и яркости для достижения наилучшего результата. Результатом такой обработки становится чёрно-белое изображение, где чёрный фон — это подложка, а белые цвета — элементы в области легирования, с резкими краями. Неровности сглаживаются гауссовым фильтром, а артефакты шума в виде белых точек просто заливаются чёрным цветом, чтобы не создавать ложных срабатываний во время последующей работы алгоритма машинного зрения.

Затем выполняется сравнение изображений по структурному сходству [10] (SSIM). Индекс SSIM — метрика, которая сравнивает пиксели по трём характеристикам: яркость, контраст и структура (отношение ковариаций между образцами).

Вот схематично процесс обработки:

Слева направо: фото оригинала (golden IC); фото с фабричного образца c выделенными изменениями по сравнению с оригиналом; изображение после бинаризации и гауссова фильтра; наиболее подозрительные области, выделенные алгоритмом SSIM

Автоматическое сравнение образцов на сканирующем электронном микроскопе — это «лайтовая», более быстрая версия стандартного реверс-инжиниринга. По мнению исследователей, она позволяет сократить время сканирования с нескольких месяцев до нескольких часов.

Ни один из этих методов не способен обнаружить саботажа в производстве изделия путём ухудшения его физических свойств с запланированным устареванием, усиленной деградацией или быстрым выходом из строя. Дело в том, что такие акты саботажа не изменяют слой легирования, а меняют характеристики, например, покрытия или подложки (так называемая «параметрическая» закладка).

Кроме того, сканер закладок не обнаруживает изменение толщины межсоединений, например, линий питания, что тоже является одним из видов производственного саботажа.

| Реверс-инжиниринг | Сканер закладок | |

|---|---|---|

| Количество необходимых образцов | 50–100 | 1 |

| Обнаружено закладок | Все (кроме саботажа по надёжности) | Все (кроме саботажа по надёжности и межсоединений) |

| Время выполнения | Месяцы | Часы |

| Обработка изображений (отдельно) | Требуется | Не требуется |

| Выделение полигонов | Требуется | Не требуется |

Если сравнивать такой сканер с электрическими тестами, то он обеспечивает более надёжный результат:

| Тип закладки | Логический тест | Тест питания | Тест на задержку | Время выполнения | Сканер закладок |

|---|---|---|---|---|---|

| Функциональная | Возможно | Возможно | Возможно | Возможно | Да |

| Параметрическая | Нет | Да | Да | Нет | В будущем |

| Большая | Возможно | Да | Возможно | Да | Да |

| Маленькая | Да | Нет | Да | Возможно | Да |

| Конкретная | Да | Да | Да | Возможно | Да |

| Нечёткая | Да | Возможно | Да | Возможно | Да |

В упомянутой научной работе исследователи искали изменения, якобы внесённые нечистоплотным подрядчиком (полупроводниковой фабрикой) в оригинальные шаблоны. Но ранее уже отмечалось, что некоторые считают самым рискованным именно этап проектирования, а не производства. Что делать, если нечистоплотным выступит не подрядчик, а разработчик микросхемы — это риторический вопрос. Возможно, никакие микроскопы тут не помогут.

По мнению безопасников [11], бэкдоры в микросхемах — это «не проблема, которую можно решить, а скорее условие, в котором мы существуем». Такой подход к жизни — часть философии стоицизма. Это не значит, что мы обязаны бездействовать. Просто если жизнь не очень приятная, то это принимается спокойно, без истерики.

Автор: Анатолий Ализар

Источник [12]

Сайт-источник PVSM.RU: https://www.pvsm.ru

Путь до страницы источника: https://www.pvsm.ru/informatsionnaya-bezopasnost/383709

Ссылки в тексте:

[1] идёт дискуссия: https://habr.com/ru/company/ruvds/blog/687758/

[2] контрпропаганду: https://habr.com/ru/post/678022/

[3] древнее самого человечества: https://www.labirint.ru/books/678101/

[4] Hardware Trojans in Chips: A Survey for Detection and Prevention: https://www.ncbi.nlm.nih.gov/pmc/articles/PMC7570641/

[5] исследование: https://ryancor.medium.com/hardware-trojans-under-a-microscope-bf542acbcc29

[6] код Verilog: https://github.com/ryancor/HWT-Verilog/tree/main/RTL/source

[7] EDA Playgrounds: https://www.edaplayground.com/

[8] исследование: https://link.springer.com/article/10.1007/s41635-018-0055-0

[9] Variomill: https://www.varioscale.com/variomill

[10] сравнение изображений по структурному сходству: https://ieeexplore.ieee.org/document/1284395

[11] мнению безопасников: https://www.wired.com/2011/08/problem-from-hell/

[12] Источник: https://habr.com/ru/post/724340/?utm_source=habrahabr&utm_medium=rss&utm_campaign=724340

Нажмите здесь для печати.