Статья посвящена актуальной задаче деления тактовых частот, стоящей перед разработчиками широкого спектра цифровых устройств на основе ПЛИС. Предложенные технические решения могут оказаться полезными при проектировании заказных и серийных СБИС. Рассмотрены два примера технической реализации делителей частоты с дробными коэффициентами деления 3:2 и 5:2. Оба варианта делителей описаны в виде поведенческих моделей на языке Verilog, что позволяет реализовать данные функциональные узлы в объёме ПЛИС различных архитектур и производителей.

Читать полностью »

Рубрика «xilinx» - 5

Организация делителя частоты с дробным коэффициентом деления в объёме ПЛИС

2016-07-21 в 11:58, admin, рубрики: asic, cpld, fpga, xilinxСеминары по введению во всё: от верилога и цифровой логики до микроархитектуры встроенных процессоров и RTOS-ов

2016-07-03 в 6:30, admin, рубрики: almaty management university, Altera, amd, computer architecture, fpga, gdsii, imagination technologies, microarchitecture, Microchip Technology, PIC32MZ, register transfer level, SystemVerilog, Verilog, vhdl, xilinx, Казахстан, параллельное программирование, ПЛИС, программирование микроконтроллеров, Промышленное программирование, Россия, семинары, УкраинаГоспода! Мы с Тимуром Палташевым из AMD в Саннивейл, Калифорния, а также с несколькими соратниками из России, Украины и Казахстана решили спланировать несколько семинаров разных форматов, которые покрывают темы на стыке хардвера и софтвера: цифровая логика, Verilog, правила RTL (Register Transfer Level), введение в микроахитектуру (строение конвейера) процессоров, низкоуровневое программирование на ассемблере, использование микроконтроллеров, особенности чипов для интернета вещей, введение в RTOS-ы, лабы на ПЛИС-ах / FPGA, а также (для части аудитории, которая интересуется производством чипов) физические аспекты проектирования и производства на фабрике (для последнего мы решили привлечь материалы от преподавателя курса в Университете Калифорнии Санта Круз, отделение в Silicon Valley).

Цель этого поста — обсудить кому что нравится на основе детального плана первого из таких семинаров, который будет в Казахстане. Идея данного семинара в том, чтобы пригласить некоторое преподавателей казахстанских вузов и сделать для них обзор, чтобы помочь им сориентироваться, в каких местах можно повысить качество их программ в программировании встроенных систем, электронике, а также затронуть связанные области типа интернета вещей и роботики.

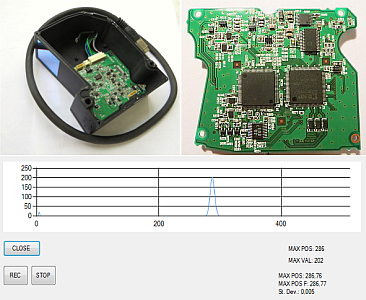

Реверс-инжиниринг лазерного датчика расстояния

2016-04-04 в 5:36, admin, рубрики: fpga, Keyence, Spartan, xilinx, лазерный дальномер, ПЛИС, программирование микроконтроллеров, реверс-инжиниринг

Однажды ко мне попал нерабочий лазерный датчик расстояния Keyence LK-G407. Мало того, что он был нерабочий, так его еще и нельзя было использовать без специального управляющего блока. Но ведь у датчика такие интересные характеристики: измерение расстояния с точностью до единиц микрон, и скорость работы — 50 килоизмерений/с. Так что, чтобы запустить его, придется заметно поковыряться в самом датчике, заодно и ценный опыт получить.

Читать полностью »

Custom floating point format on FPGA

2016-03-14 в 17:00, admin, рубрики: Altera, floating point, fpga, fpga/asic, open source, vhdl, xilinx, Алгоритмы, математика, программирование микроконтроллеровВсем привет!

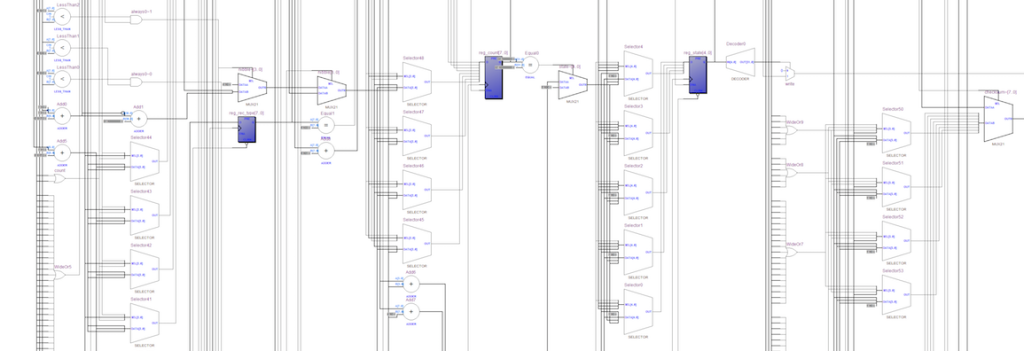

В данной статье речь пойдет о числах в формате с плавающей точкой и в частности о реализации специализированного формата FP23 на программируемых логических интегральных схемах (ПЛИС). В рамках конкретного проекта у меня родилась мысль реализовать оптимальный для определенных нужд формат данных с плавающей точкой. В итоге эта мысль переросла в реальный проект, который впоследствии нашел применение в некоторых интересных задачах цифровой обработки сигналов. В статье рассмотрены основные сложности при реализации формата данных floating point на ПЛИС Xilinx, рассмотрены базовые математические операции в формате FP23. Также в конце статьи вы можете найти исходный код проекта, которой можно свободно использовать в своих задачах или на его основе реализовать похожие форматы данных.

Как делать парсинг текста голым хардвером, без процессора и без софтвера

2016-03-10 в 6:53, admin, рубрики: Altera, altera de0-cv, altera de0-nano, digilent basys 3, digilent nexys 4 ddr, elf, fpga, mips, MIPS microAptiv UP, MIPSfpga, motorola s-records, regular expressions, state machine, turing machine, Verilog, vhdl, xilinx, Анализ и проектирование систем, ненормальное программирование, ПЛИС, программирование микроконтроллеров, Регулярные выраженияКто-то парсирует текстовый файл программой на Питоне, другой пишет скрипт с регулярными выражениями на Перле, Си-программист стыдливо возится с буферами и указателями, иногда применяя Yacc и Lex.

А можно ли парсировать текст голым железом? Вообще без программы?

— А как это?, — спросил меня знакомый, — С помощью Ардуино?

— Внутри Ардуино стоит вполне фон-неймановский процессор и работает программа, — ответил я, — Нет, еще более голое железо.

— А-а-а-а, этот, микрокод?, — догадался мой товарищ и взглянул на меня победно.

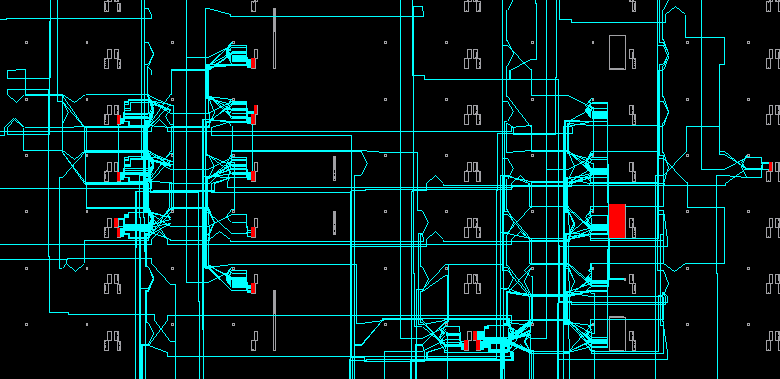

— Нет, термин «микрокод» использовался для специфической организации процессоров в 1970-е годы, потом его использование сошло на нет, — ответил я и добавил, — Правда есть еще микрооперации в интеловских процессорах, в которые перекодируется x86, но это тоже другое. Нет, я имею в виду парсинг текста устройством, состоящим из логических элементов И-ИЛИ-НЕ и Д-триггерами, как на картинке ниже.

— Невозможно! — воскликнул мой приятель, — в таком устройстве где-то сбоку должен сидеть процессор и хитро подмигивать!

— Почему это невозможно?, — парировал я, — Вот машину Тьюринга знаешь? Парсирует текст на ленте, а сбоку никакие интелы и ардуино не подмигивают.

— Нуу, машина Тьюринга, — протянул приятель, — это абстракция, типа Демона Максвелла.

— Никакой абстракции, сейчас увидишь работающую схему, парсирующую текст, — сказал я и прибавил, — но сначала расскажу, зачем мне вообще это понадобилось.

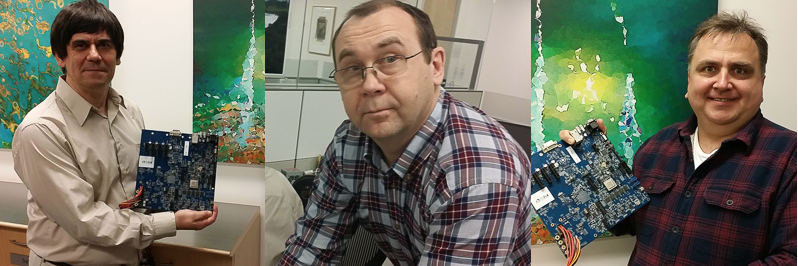

Платы для разработчиков и терминал на основе российского микропроцессора Байкал-Т

2016-02-26 в 9:09, admin, рубрики: Baikal Electronics, baikal-t, cnc machining, CoreMark, cpu, electronic engineering times, imagination technologies, mips, MIPS P5600, multicore, superscalar processors, Synopsys, t-platforms, tavolga, terminal, thin client, TSMC, xilinx, Анализ и проектирование систем, виртуализация, параллельное программирование, Программирование, Промышленное программированиеЗа последние три дня вышло несколько новостей про российский процессор Байкал-Т:

1. Российская компания «Т-Платформы» представила процессорный модуль SF-BT1 с Байкалом-Т, который она собирается распостранять среди разработчиков.

2. Также «Т-Платформы» выпустили на основе Байкала-Т тонкий клиент «Таволга терминал», который может работать не только как терминал, но и как автономной компьютер с Linux Debian 8.

3. Т-Платформы показывали и плату для разрабочиков, и терминал на основе Байкала-Т на выставке Embedded World в Нюренберге, в сотрудничестве с британской компанией Imagination Technologies, которая разработала микропроцессорное ядро MIPS P5600, которое использует Байкал-Т.

Я не буду пересказывать все статьи про Байкал-Т, Т-Платформы и Таволгу. Те разрабочики, кто этим интересуется, могут сами сходить по ссылкам и посмотреть параметры плат. Я добавлю некоего информационного гарнира про процессор, его экосистему и историю.

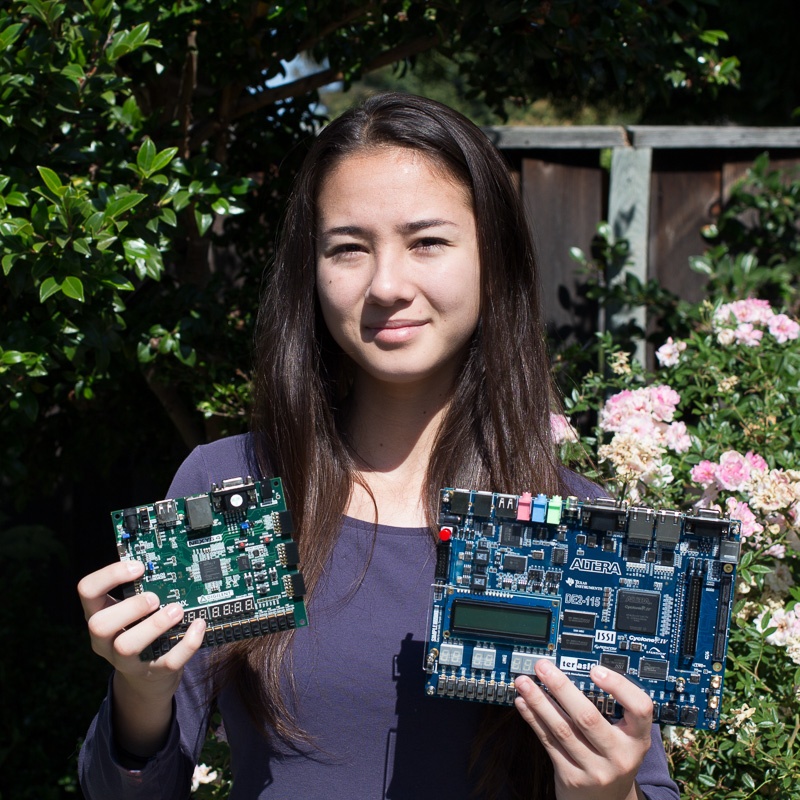

На фотографии ниже — ранние пользователи байкаловских плат. Это инженеры из России, Украины и Казахстана, которые участвуют в разработке микропроцессорного ядра MIPS P5600 и его сотфтверной экосистеме в отделении Imagination Technologies в Санта-Клара, Калифорния: Леонид Егошин (поддержка многоядерности в ядре Линукса), Сергей Вакуленко (симулятор для верификации) и Юрий Панчул (модели интерфейсов шин):

Вообще Байкал-Т — это плод международного сотрудничества, в которон вовлечены в частности:

Читать полностью »

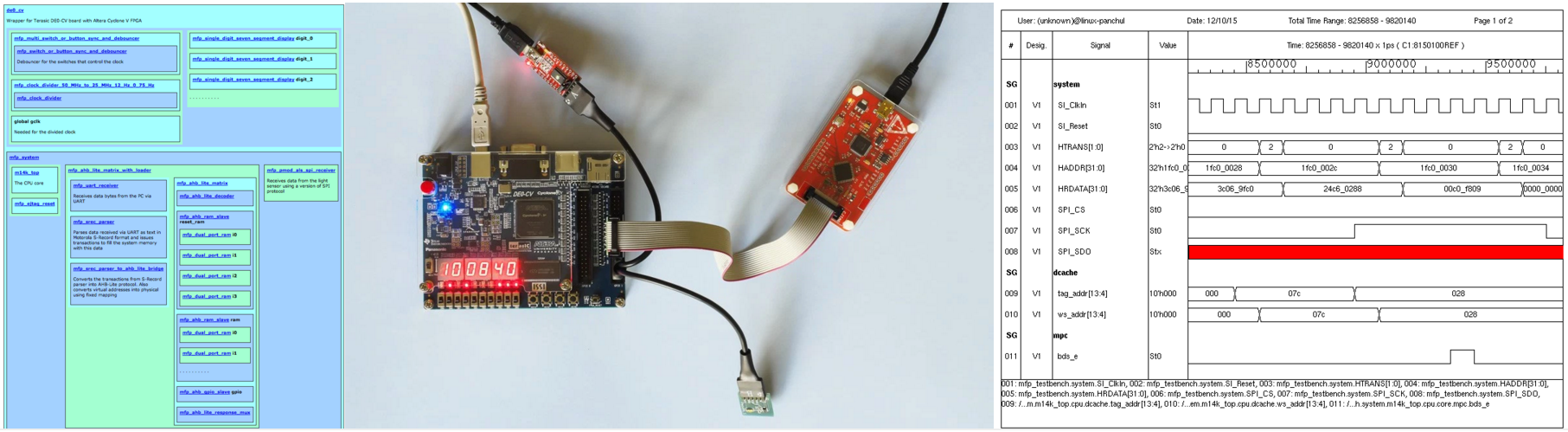

Как начать работать с MIPSfpga

2016-01-16 в 5:59, admin, рубрики: Altera, fpga, imagination technologies, mips, MIPS microAptiv UP, MIPSfpga, SPI, uart, Verilog, vhdl, xilinx, Анализ и проектирование систем, параллельное программирование, ПЛИС, программирование микроконтроллеров, метки: плисMIPSfpga — это пакет, который содержит процессорное ядро в исходниках на Verilog, которое можно менять, добавлять новые инструкции, строить многопроцессорные системы, менять одновременно софтвер и хардвер, симулировать на симуляторе верилога, синтезировать для ПЛИС/FPGA и т.д. Его можно в целях эксперимента например запускать с частотой 1 такт в секунду и выводить наружу информацию о состоянии кэша, конвейера, и любых структур внутри процессора. При этом ядро MIPS microAptiv UP внутри MIPSfpga — это то же ядро которое например используется в платформе IoT Samsung Artik 1 и Microchip PIC32MZ, т.е. студенты получают возможность работать с тем же кодом, с которым работают инженеры в Samsung и Microchip.

MIPSfpga не предназначен для введения в предмет с абсолютного нуля. Для его плодотворного использования нужно чтобы студент или исследователь уже знал основы цифровой схемотехники, умел бы программировать на Си и на ассемблере, а также представлял бы концепции микроархитектуры — конвейера, конфликтов конвейера и т.д. Желательно, чтобы до работы с MIPSfpga студент уже бы построил собственный простой процессор с нуля и мог бы сравнивать свой простой процессор с процессором, используемым в промышленности и совместимым с развитой экосистемой разработки.

Генераторы хаоса на ПЛИС

2015-12-28 в 10:20, admin, рубрики: fpga, fpga/asic, github, Matlab, open source, RTL, vhdl, xilinx, Алгоритмы, Лоренц, математика, ПЛИС, программирование микроконтроллеров, хаосВсем привет!

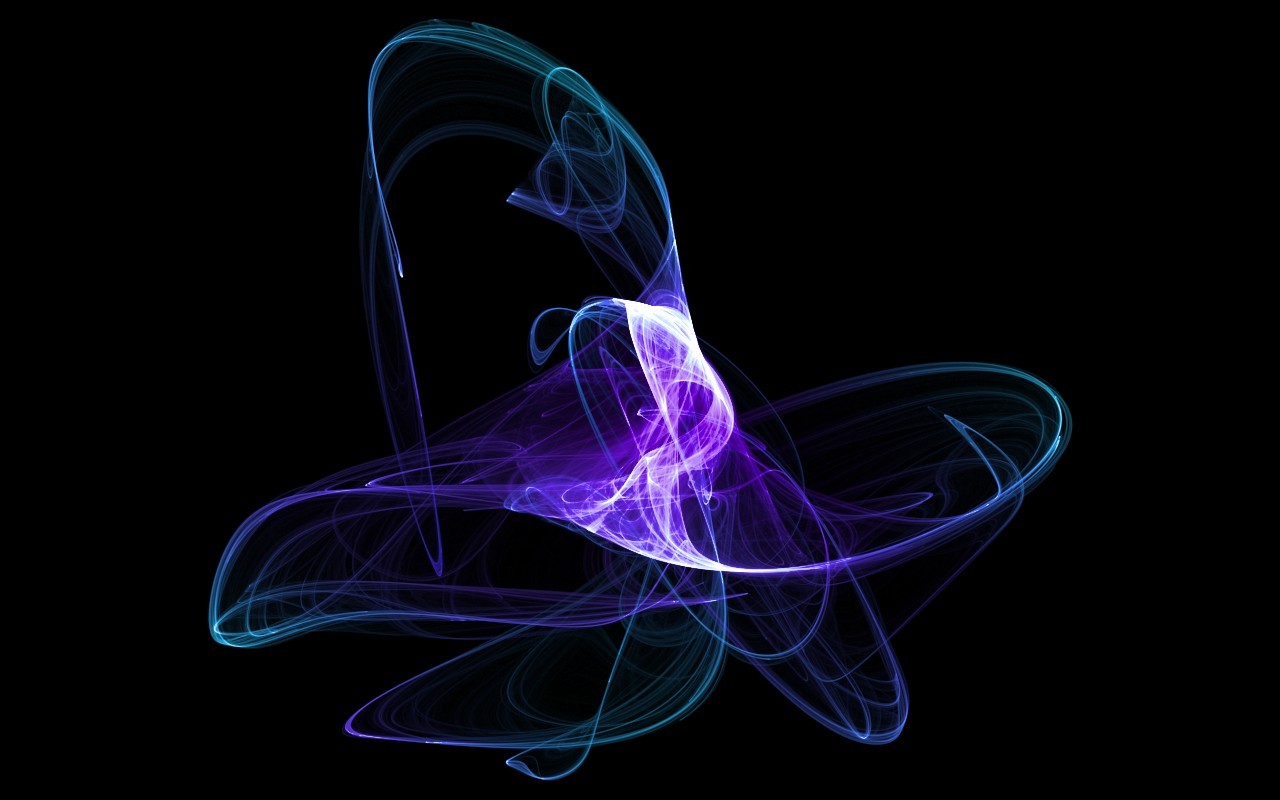

Эта статья посвящается удивительным особенностям в мире хаоса. Я постараюсь рассказать о том, как обуздать такую странную и сложную вещь, как хаотический процесс и научиться создавать собственные простейшие генераторы хаоса. Вместе с вами мы пройдем путь от сухой теории до прекрасной визуализации хаотических процессов в пространстве. В частности, на примере известных хаотических аттракторов, я покажу как создавать динамические системы и использовать их в задачах, связанных с программируемыми логическими интегральными схемами (ПЛИС).

Прототипирование ASIC на FPGA

2015-12-08 в 12:58, admin, рубрики: Aldec, Altera, asic, cadence, fpga, Synopsys, xilinx, МЦСТ, Научно-популярное, Процессоры, Электроника для начинающих Разработка микросхем дело сложное, дорогое и долгое. И цена любой ошибки крайне велика. После изготовления кристалла патчами и обновлениями уже ничего не исправить. Поэтому к проверке проектируемых схем на этапе разработки подходят особенно скрупулёзно. Для каждого функционального блока пишутся блочные тесты во всех рабочих и не рабочих режимах. После интеграции блока в общую схему проводятся системные тесты, как этот блок работает составе системы. Все тесты постоянно крутятся в регрессионном тестировании. Даже есть неформальный признак более менее приемлемого уровня тестирования – когда объем кода тестов в 10 раз больше объема кода тестируемого блока. Но все эти тесты не дают ощущения, что схема жизнеспособна, так как любое моделирование это поведение схемы на протяжении сотен миллисекунд максимум. А в жизни схема должна отработать сотни тысяч часов. Однажды я искал сбой, когда на 1 Гбайт переданной информации терялись 1 или 2 байта и никакие функциональные тесты эту проблему не обнаруживали. И проявлялась эта ошибка только на FPGA прототипе будущей микросхемы. О том какие прототипы делали мы и что вообще твориться в мире расскажет эта статья.

Читать полностью »

Цифровая фильтрация на ПЛИС – Часть 1

2015-12-03 в 16:02, admin, рубрики: Altera, CIC, dsp, FIR, fpga, open source, tutorial, xilinx, ПЛИС, программирование микроконтроллеров, Электроника для начинающихВсем привет!

Давно хотел начать цикл статей, посвященных цифровой обработке сигналов на ПЛИС, но по разным причинам так и не мог к этому приступить. К счастью, в распоряжении появилось немного свободного времени, поэтому периодически я буду публиковать материалы, в которых отражены различные аспекты, связанные с ЦОС на ПЛИС. В этих статьях я постараюсь минимизировать теоретическое описание тех или иных алгоритмов и большую часть материала посвятить практическим тонкостям, с которыми столкнулся лично я и мои коллеги, и знакомые, так или иначе связанные с разработкой на ПЛИС. Надеюсь, данный цикл статей принесет пользу, как начинающим инженерам, так и матёрым разработчикам.

Читать полностью »