В последние семь лет ко мне неоднократно обращались преподаватели детских кружков с вопросом, что бы такое придумать для детей в области электроники, чтобы было 1) интересно 2) конвертировалось бы в будущую специальность и 3) давало бы что-нибудь качественно другое, чем уже устоявшиеся среди преподавателей лего-ардуины-и-разберри-паи.

Подход, который я хотел бы предложить в этой заметке — это конструирование устройств на основе макентной платы, используя примитивы разных уровней абстракции. Прежде чем описать суть предложения, я приведу аналогию. Допустим, нам нужно исследовать местность между городом A и городом B. Из A в B можно проехать на автомашине, рассматривая окрестности дороги. Но еще лучше — проехать не только на автомашине, но и потом проплыть тот же маршрут на подводной лодке, пролететь его на самолете, походить в некоторых местах пешком, а также прорубить кусок шахты на участке между городами на проходческом комбайне. По ходу дела ученик получит не только опыт вождения автомобиля, но и представление о структуре недр, морской экосистеме, нравах жителей и общей карте местности.

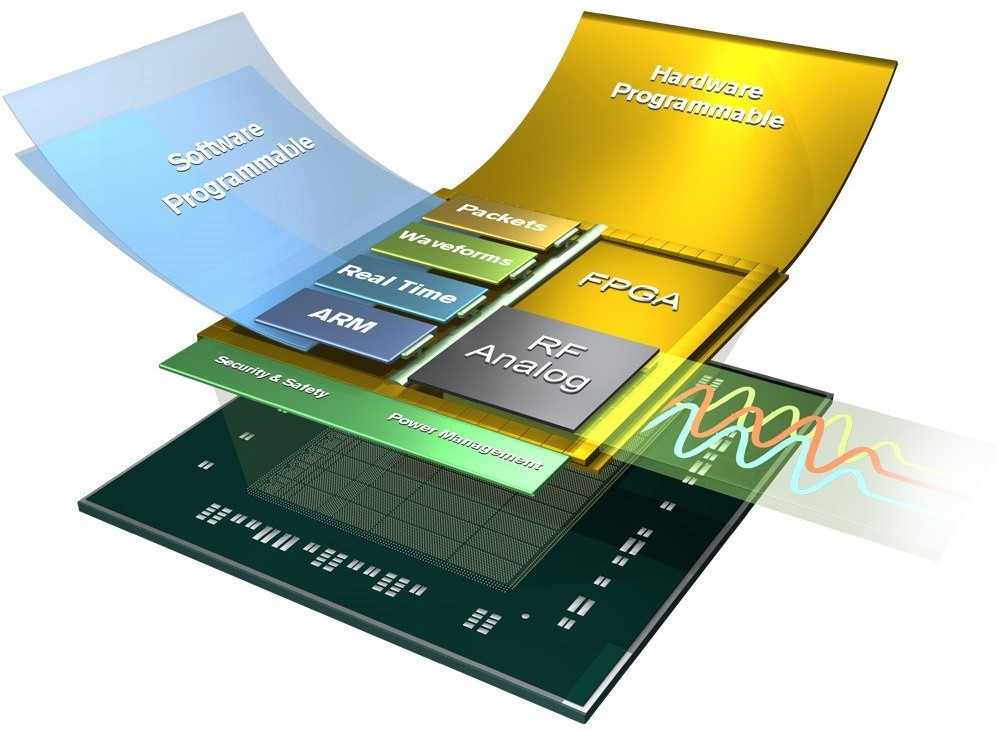

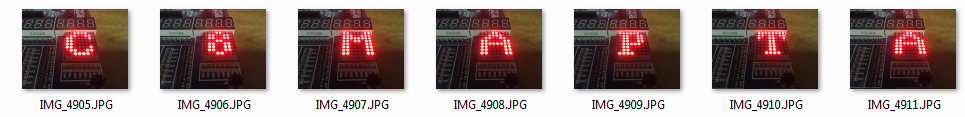

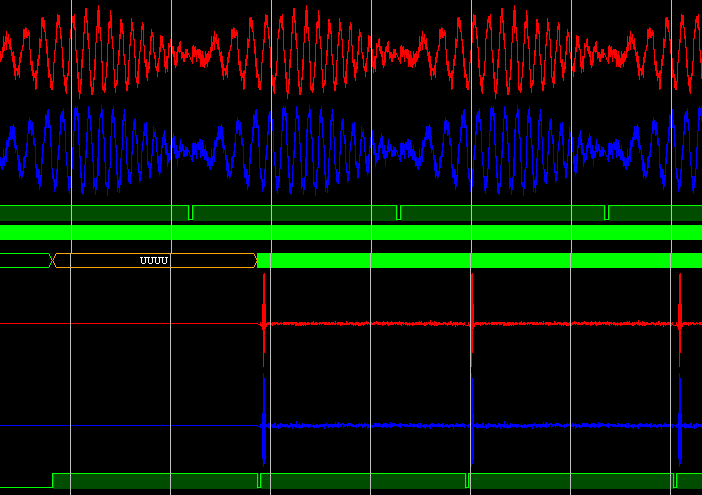

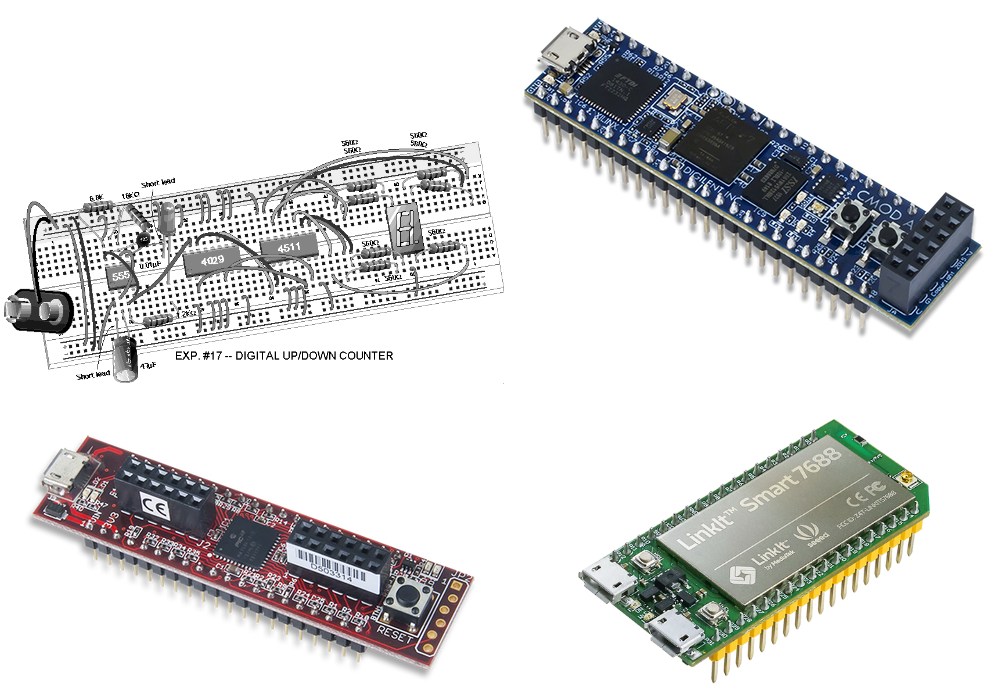

Теперь суть предложения. Ученик за несколько дней выполняет серию простых электронных проектов, которые имеют сходную функциональность, но используют в качестве строительных кубиков разные объекты, в том числе:

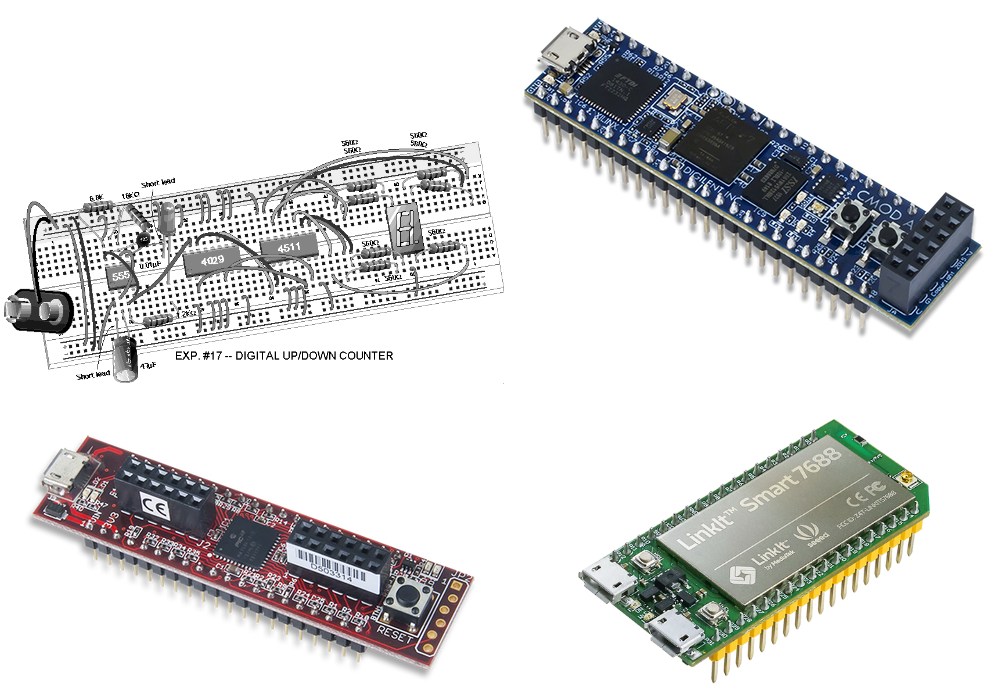

1. Микросхемы малой степени интеграции, по несколько логических элементов в каждой

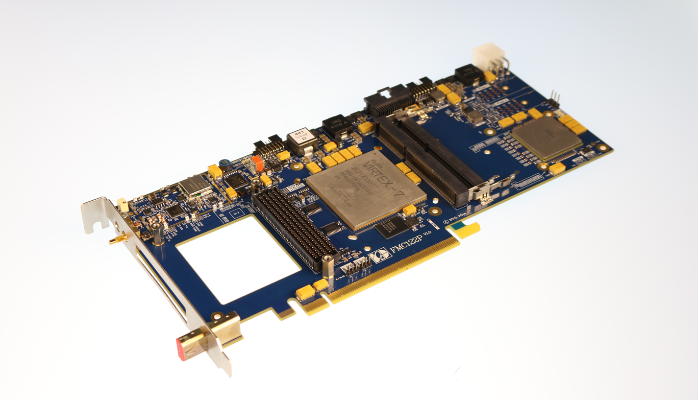

2. Программируемые логические интегральные схемы, десятки тысяч ячеек с изменяемой логической функцией

3. Микроконтроллеры

4. Встраиваемые процессоры

Читать полностью »