Год 2017 стал годом больших изменений в зарождающейся экосистеме российской микроэлектроники. Эти изменения заметило даже ранее безразличное к российскому железу общество. Российский чип ELISE для умных камер от ЭЛВИС-НеоТек вышел на удобной плате для разработчиков. Эту плату показали по Первому каналу российского телевидения. C российским процессором Байкалом-Т теперь может поработать любой программист через доступ к серверам удаленной лаборатории, которую байкаловцы создали вместе с МГУ. Российские процессоры от НИИСИ стали использовать для телекоммуникационного оборудования.

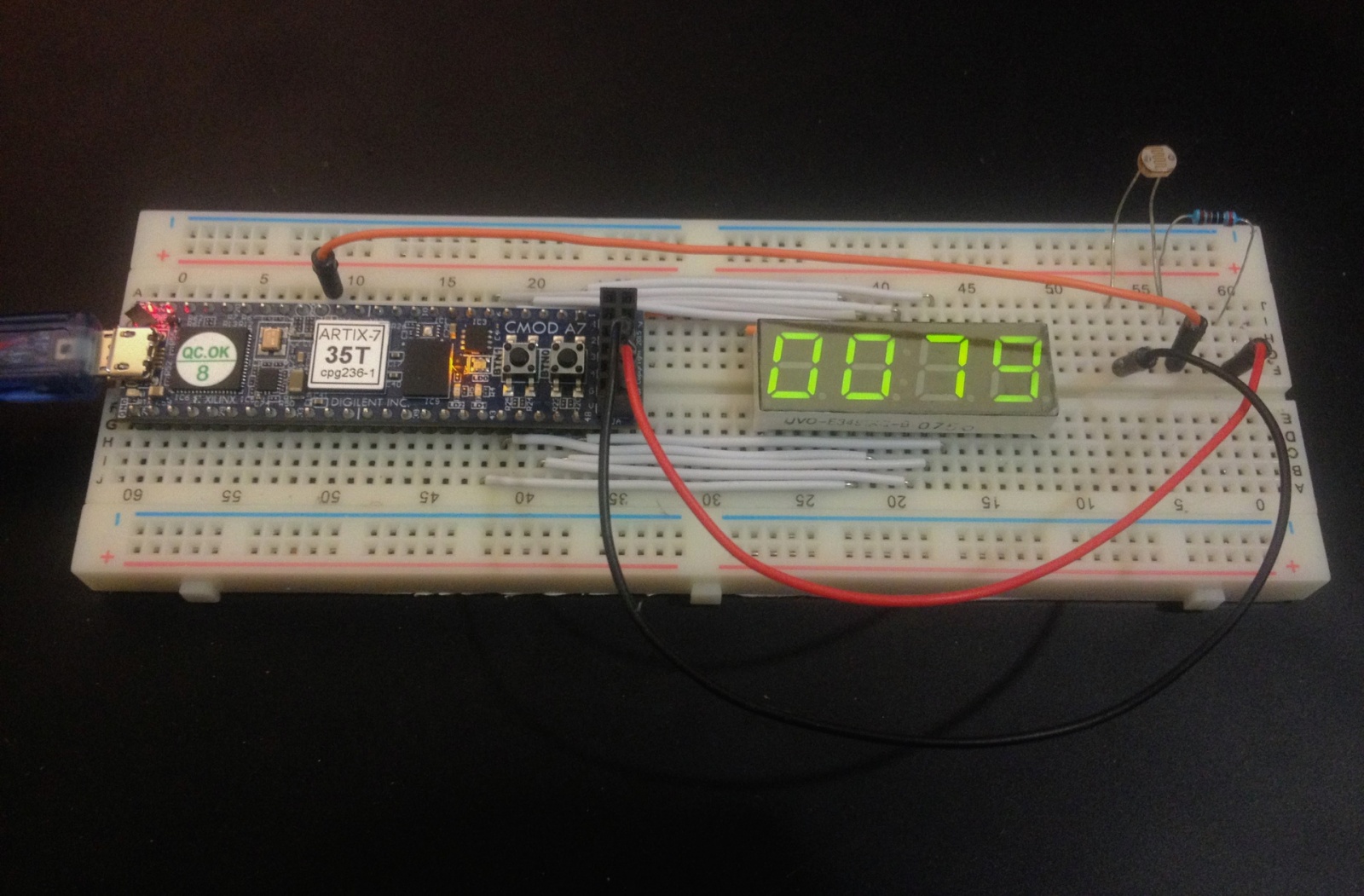

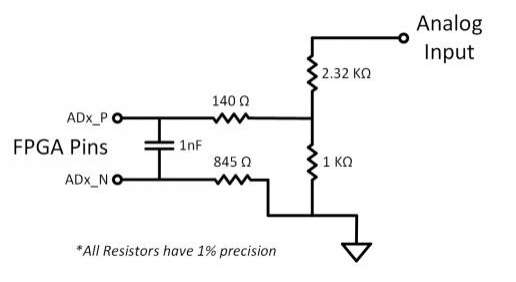

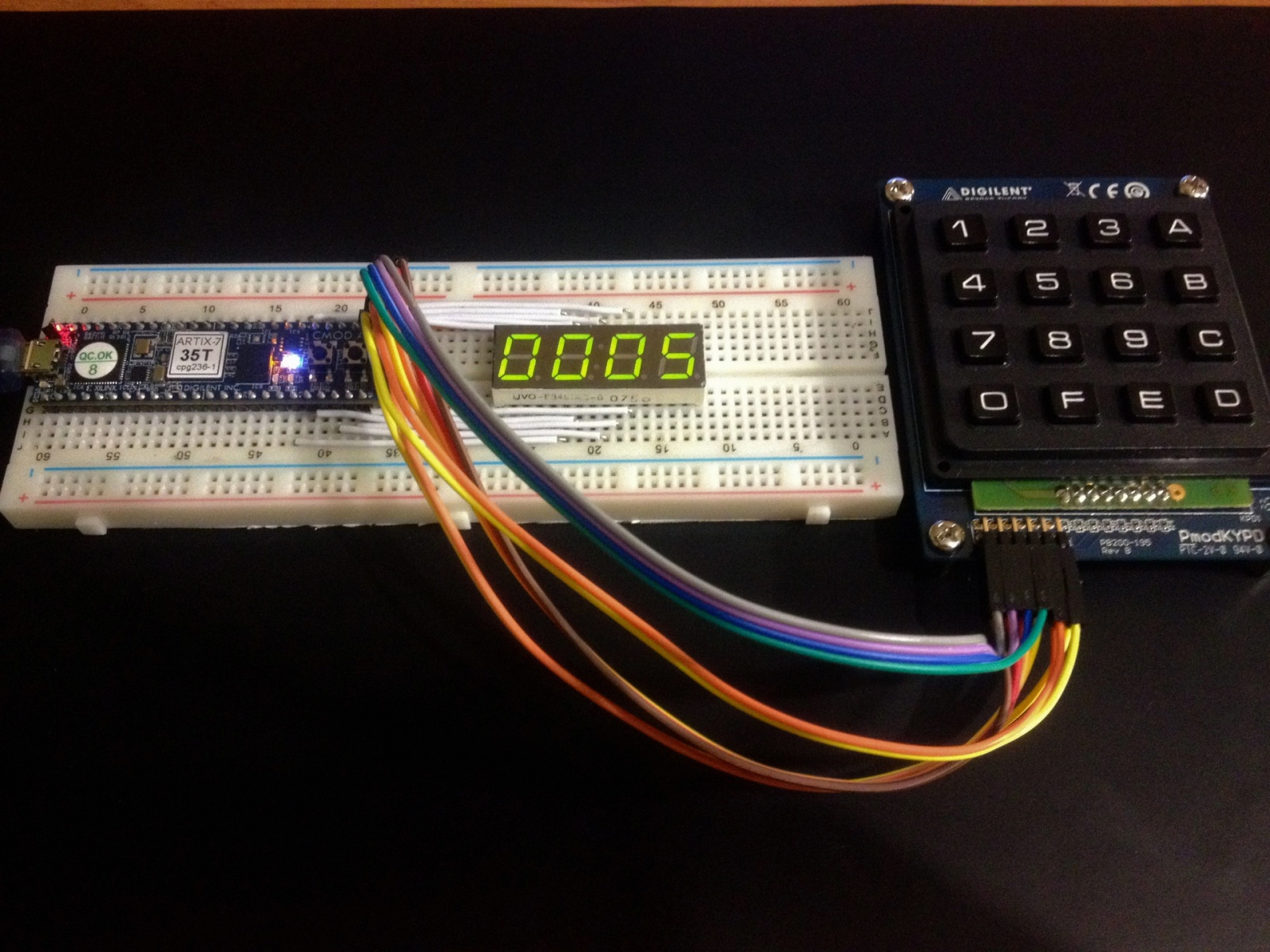

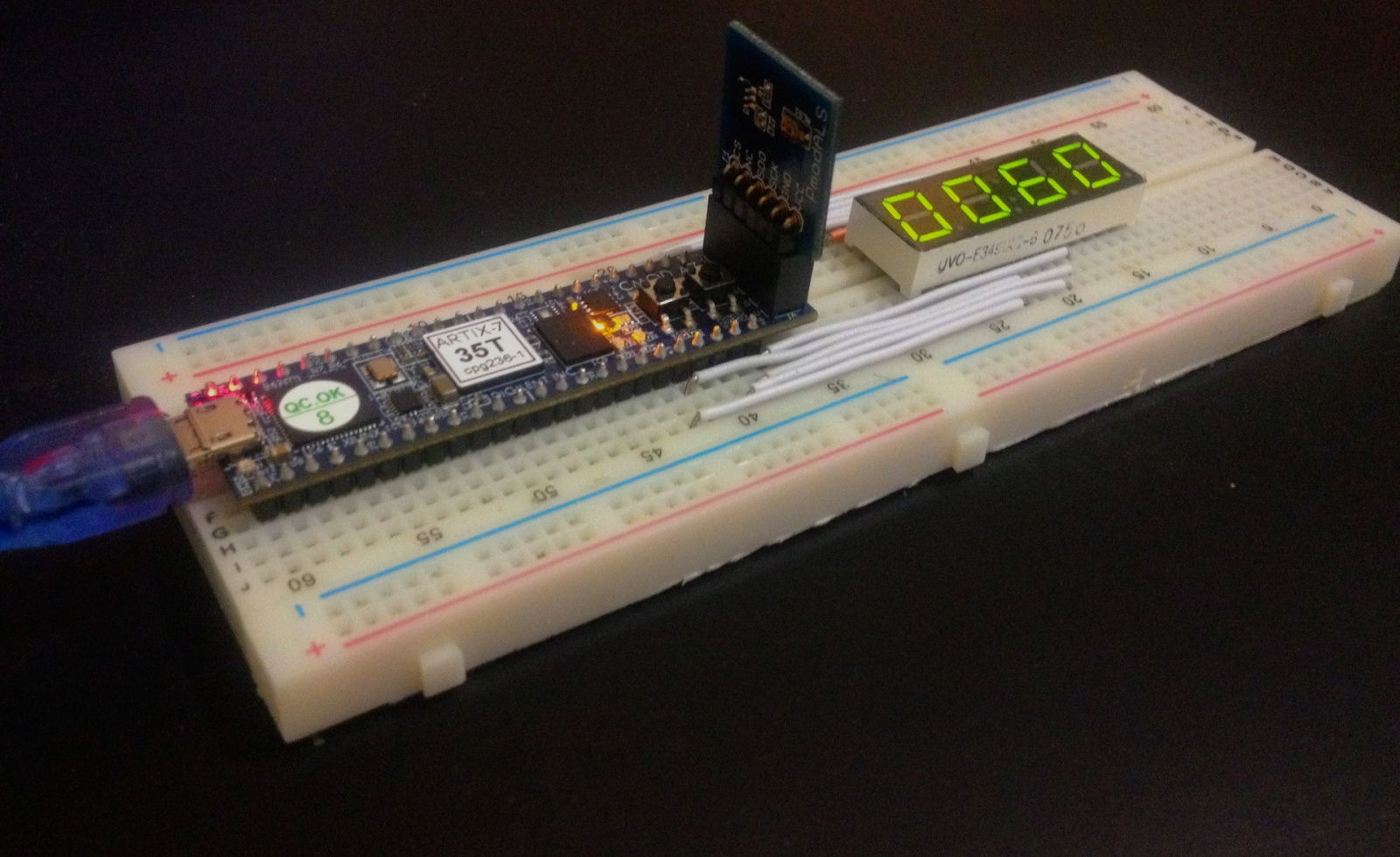

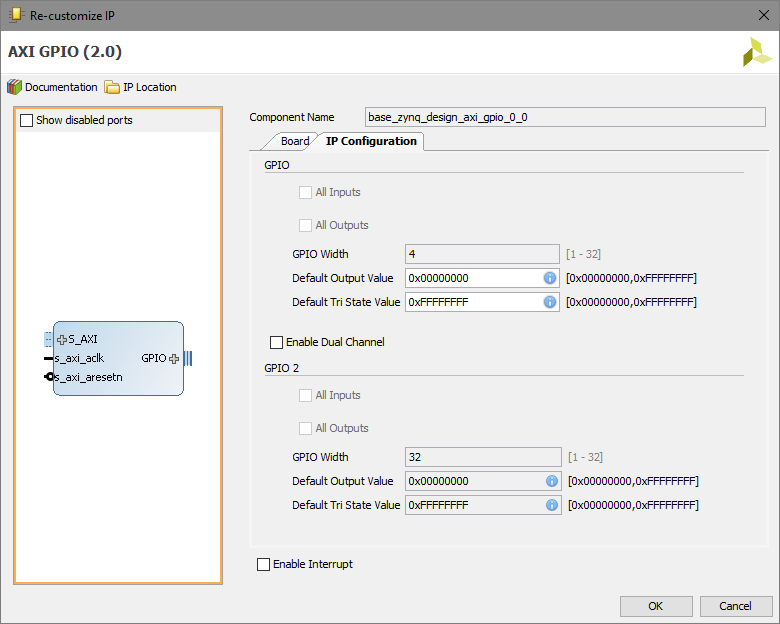

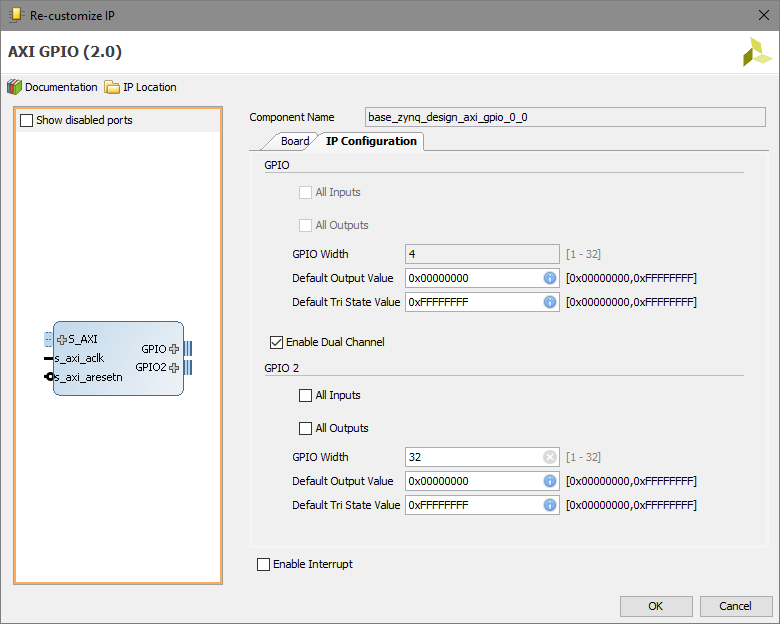

Для перехода от единичных успехов к развитой экосистеме необходимо подкрутить образование. В сентябре в Томске прошло совещание, на котором преподаватели и инженеры из Москвы, Сибири, Поволжья, Калифорнии и других мест обменялись опытом в преподавании микроэлектроники. Одновременно там же прошел учебный семинар по SystemVerilog, VHDL, FPGA, CPU IP, на который пришли не только россияне, но и студенты из Китая и Вьетнама, среди которых быстро распостранилась информация, что рядом учат чему-то полезному для их карьеры. Под катом — отчет об этом и сопутствующих событиях. Действующие лица: томские и новосибирские университеты, московские МГУ, МФТИ и МИЭТ, новосибирские лицеи, российская компания МЦСТ, американские MIPS, AMD и National Instruments, британская Imagination и казахский Назарбаевский Университет.