Рубрика «vivado»

Zynq 7000. Обмен информацией между PS и PL

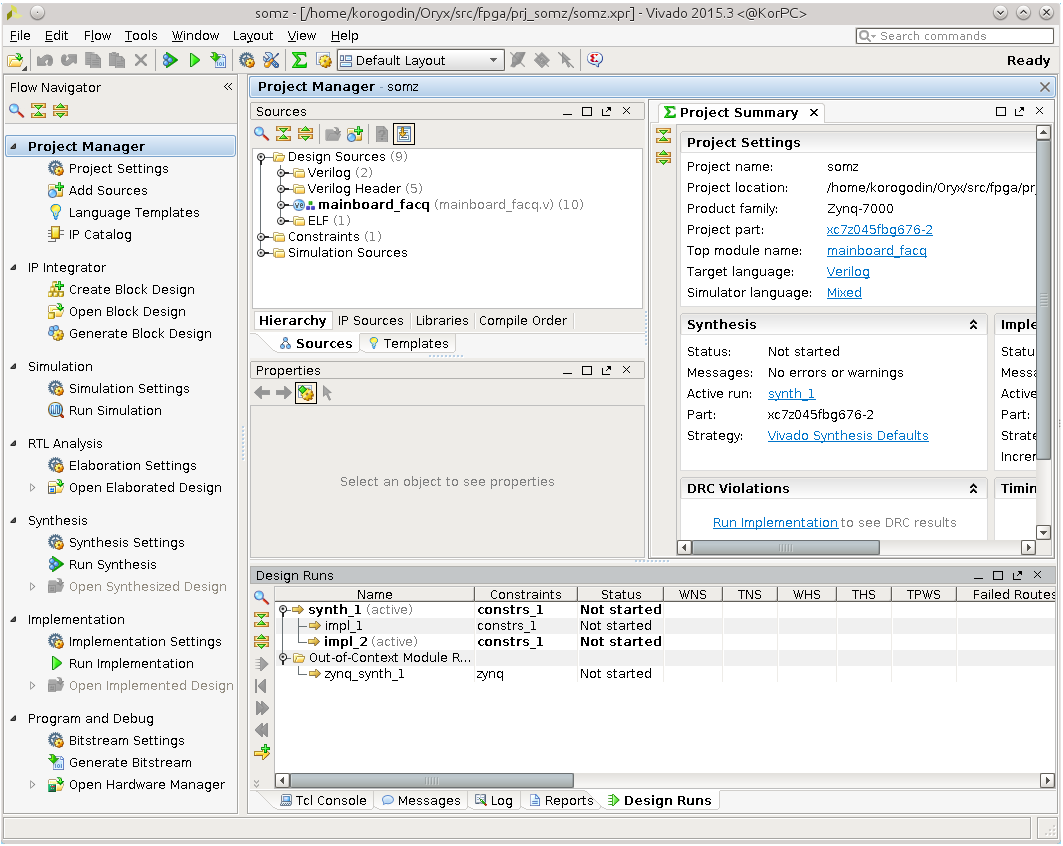

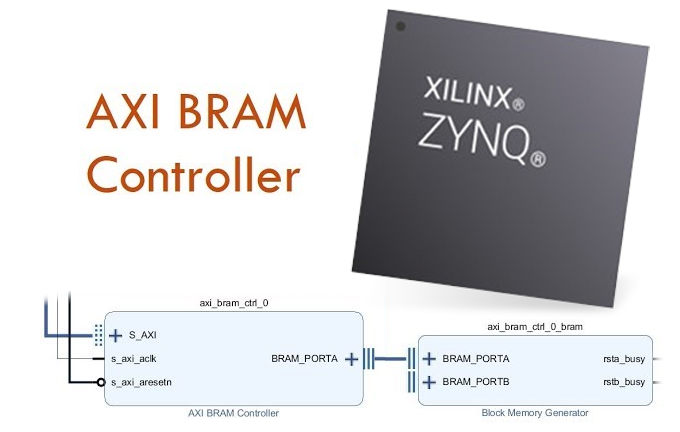

2021-08-15 в 20:28, admin, рубрики: AXI, bram, diy или сделай сам, fpga, howto, linux, qmtech, SDK, vivado, xilinx, zynq, Процессоры, Электроника для начинающихПродолжаю повествование о том, как проходит мое изучение возможностей отладочной платы с SoC Zynq 7000 на базе отладочной платы QMTech. В этой статье я опишу то, как я решал задачу примитивного обмена данными между PS и PL с использованием baremetal application и при использовании Linux. Всем интересующимся добро пожаловать под кат!

Дисклеймер

SP701 + PCAM-5C + 15 Минут+ VITIS = Easy MIPI на FPGA

2019-11-20 в 16:45, admin, рубрики: fpga, mipi, pcam, sp701, spartan 7, vitis, vivado, xilinxАннотация

Интерфейс MIPI сегодня становится всё более популярным интерфейсом для подключения камер и дисплеев. По этой причине всё больше отладочных комплектов на основе FPGA содержат на борту соединители интерфейса MIPI – как для подключения камер(ы) и дисплея(ев). Для того чтобы начать работать с новой технологией или просто посмотреть что она собой представляет разработчики пытаются отыскать на просторах интернета подходящее руководство, в котором были бы описаны соответствующие нюансы работы. С одной стороны тестовый пример должен достаточно просто подниматься на отладочном комплекте, а с другой стороны давать достаточно простое и широкое понимание происходящего в этом тестовом примере.

Цель статьи – показать, как начать работать с интерфейсом MIPI используя одну из новейших отладок от Xilinx – SP701, камеру с интерфейсом MIPI от компании Digilent PCAM-5C и среду разработки Vivado+VITIS(SDK) от компании Xilinx

Простая реализация небольших CAM на ПЛИС

2019-10-09 в 21:52, admin, рубрики: cam, fpga, ISE, RTL, vhdl, vivado, xilinx, XSTВведение

Как-то раз мне потребовалось по работе реализовать небольшой блок ассоциативной памяти. Почитав, как это делается у Xilinx на BlockRAM (BRAM) или на SRL16, я несколько опечалился, так как их реализации занимали довольно много места. Решил попробовать сделать его самостоятельно. Первым вариантом стала реализация в лоб. Забегая вперед, она практически сходу мне и подошла, благо, целевая частота для дизайна была всего 125 МГц.

Особенности оконной фильтрации на ПЛИС

2018-10-23 в 10:56, admin, рубрики: Altera, c++, cordic, fpga, Matlab, Verilog, vhdl, vivado, vivado hls, windows, xilinx, Алгоритмы, математика, ПЛИС, программирование микроконтроллеровВсем привет!

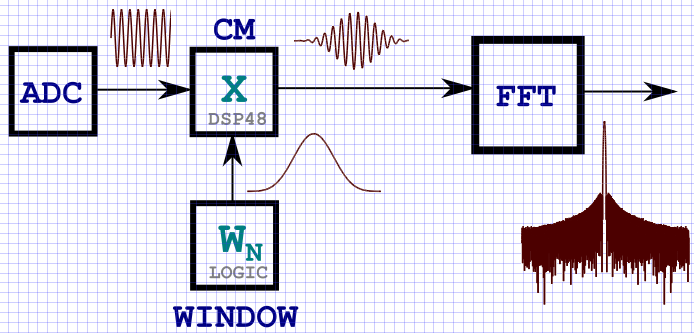

В этой статье речь пойдет об одной важной части цифровой обработки сигналов — оконной фильтрации сигналов, в частности на ПЛИС. В статье будут показаны способы проектирования классических окон стандартной длины и «длинных» окон от 64K до 16M+ отсчетов. Основной язык разработки — VHDL, элементная база — современные кристаллы FPGA Xilinx последних семейств: это Ultrascale, Ultrascale+, 7-series. В статье будет показана реализация CORDIC — базового ядра для конфигурации оконных функций любой длительности, а также основных оконных функций. В статье рассмотрен метод проектирования с помощью языков высокого уровня С/C++ в Vivado HLS. Как обычно, в конце статьи вы найдете ссылку на исходные коды проекта.

КДПВ: типичная схема прохождения сигнала через узлы ЦОС для задач анализа спектра.

Читать полностью »

Странности синтеза при работе с FPGA

2018-06-02 в 12:29, admin, рубрики: fpga, Libero SoC, Quartus, Verilog, vivadoНа сегодняшний день существует два наиболее распространённых языка описания аппаратуры: Verilog/SystemVerilog и VHDL. Сами языки описания аппаратуры являются достаточно универсальными средствами, но всегда ли это так? И от чего может зависеть «не универсальность» языка описания аппаратуры?

Идея написания данной статьи возникла при синтезе одного проекта в разных средах разработки, в результате чего были получены отличные друг от друга результаты. Так как исходный модуль является достаточно объёмным, то для демонстрации полученных результатов был написан тестовый модуль меньшего объёма, но синтез которого вызывал те же предупреждения/ошибки. В качестве тестового модуля был использован 4-х битный регистр с асинхронным сбросом, а в качестве сред разработки были выбраны Libero SoC 18.1, Quartus Prime 17.1, Vivado 2017.4.1.

Читать полностью »

SDAccel – первое знакомство

2017-04-16 в 21:10, admin, рубрики: c++, fpfftk, fpga, gpgpu, opencl, sdaccel, vivado, vivado hls, xilinx, параллельное программирование, ПЛИС

SDAccel это система программирования на OpenCL для ПЛИС фирмы Xilinx. В настоящее время всё более обостряется проблема разработки проектов для ПЛИС на традиционных языках описания аппаратуры, таких как VHDL/Verilog. Одним из методов решения проблемы является применение языка C++. OpenCL это один из вариантов применения языка С++ для разработки прошивок ПЛИС.

Читать полностью »

Реализация узла БПФ с плавающей точкой на ПЛИС

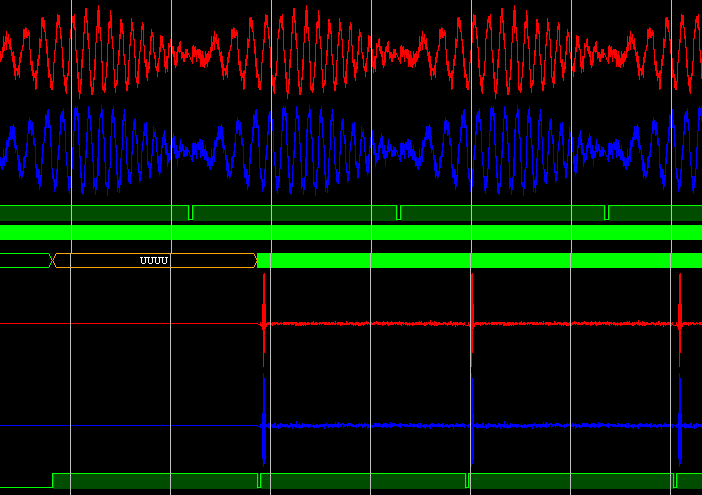

2017-02-27 в 15:11, admin, рубрики: c++, fft, fpga, Matlab, octave, open source, vhdl, vivado, xilinx, Алгоритмы, бпф, математика, ПЛИС, программирование микроконтроллеровВсем привет! В этой статье речь пойдет о реализации быстрого преобразования Фурье в формате с плавающей точкой на ПЛИС. Будут показаны основные особенности разработки ядра от самой первой стадии до готового конфигурируемого IP-ядра. В частности, будет проведено сравнение с готовыми ядрами фирмы Xilinx, показаны преимущества и недостатки тех или иных вариантов реализации. В статье будет рассказано о главной особенности ядра БПФ и ОБПФ — об отсутствии необходимости переводить данные в натуральный порядок после БПФ и ОБПФ для их совместной связки. В этой статье я постараюсь отразить всё тонкости реализации проекта под названием FP23FFTK, приведу реальные примеры использования готового ядра. Проект написан на языке VHDL и заточен под FPGA фирмы Xilinx последних семейств.

Использование TCL в разработке на FPGA

2016-08-31 в 17:02, admin, рубрики: fpga, fpga/asic, tcl, tcl/tk, vivado, xilinx, Алгоритмы, высокая производительность, ПЛИС, программирование микроконтроллеров, функциональное программированиеВсем привет! Давно не писал статьи на любимую тематику и наконец-то созрел на что-то более-менее приличное и стоящее. В этой статье речь пойдет об очень интересной задаче, с которой инженер-разработчик сталкивается чуть ли не каждый день. Предлагаю вам посмотреть, каким образом можно использовать всю мощь и простоту TCL скриптов для проектирования на FPGA. В данной статье описание базируется на ПЛИС фирмы Xilinx, но это не отменяет возможностей TCL скриптов для кристаллов ПЛИС других производителей.

Интересно? Поехали…

Читать полностью »