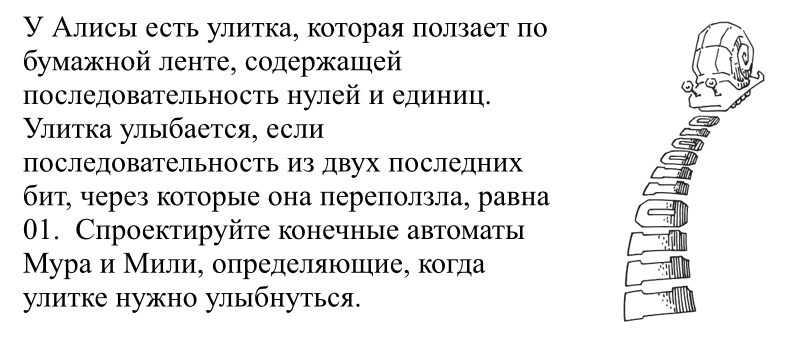

Господа! Сегодня на 1 сентября, в День Знаний, группа из украинских преподавателей вузов, их аспирантов, а также российских инженеров, решили, по согласованию с британскими издателями Elsevier через компанию Imagination Technologies, сделать небольшой подарок всем учителям компьютерной архитектуры и цифровой схемотехники, особенно тем, которые используют популярный учебник Дэвида Харриса и Сары Харрис.

Просто нажмите вот на эту ссылку и вы получите zip-файл со слайдами для чтения лекций по этому учебнику на русском языке. Причем без регистрации, которая требуется для загрузки учебника как такового.

Слайды могут быть полезны не только учителям, но и любым интересующимся, кто хочет узнать, как своими руками построить микропроцессор, но не хочет пробиваться через 1600 планшетных страниц книги.

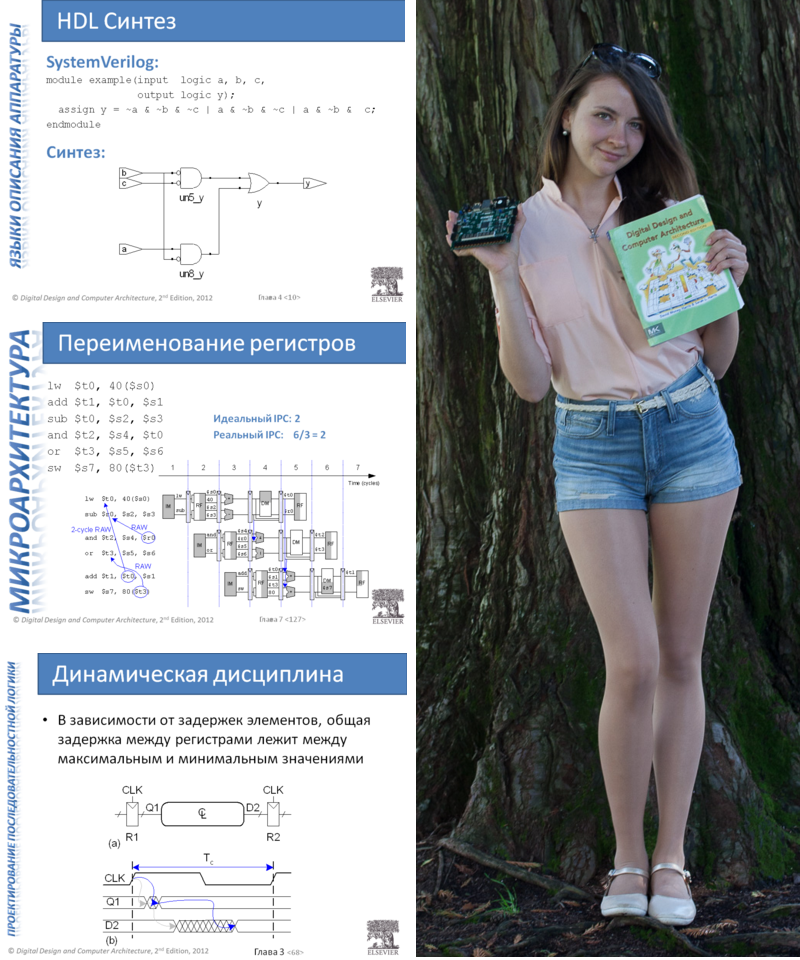

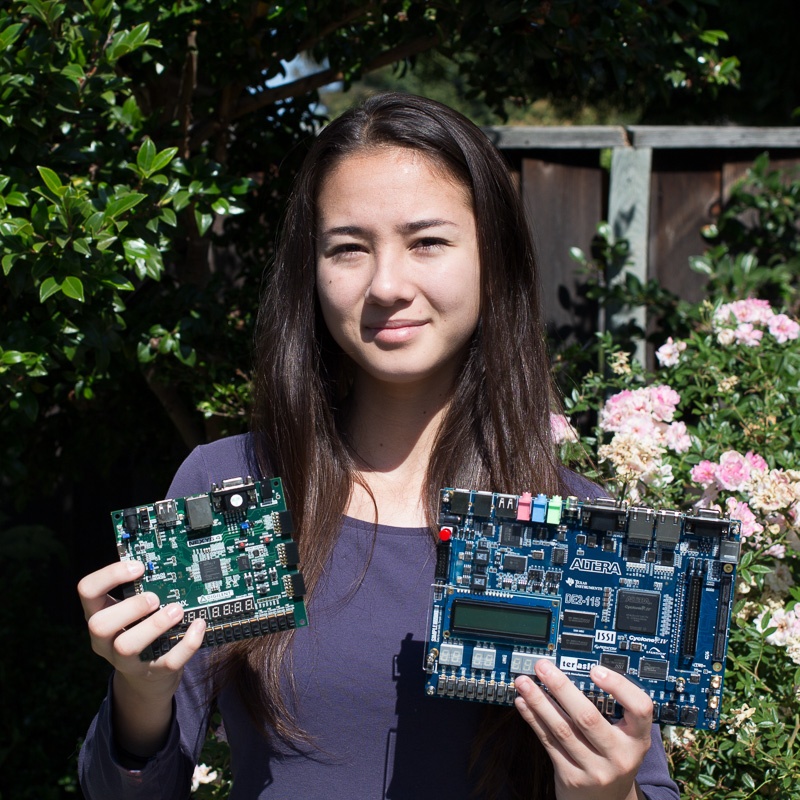

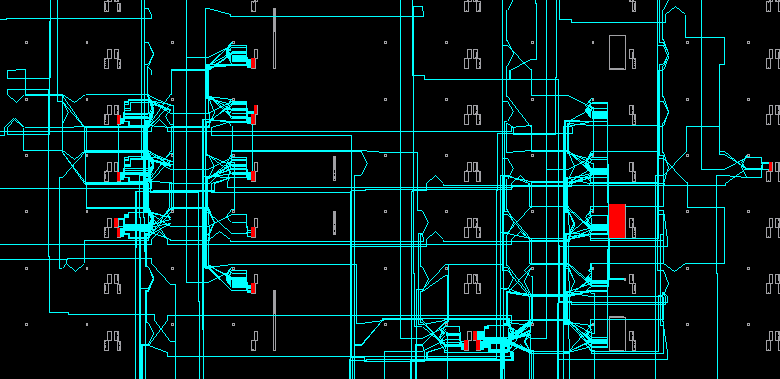

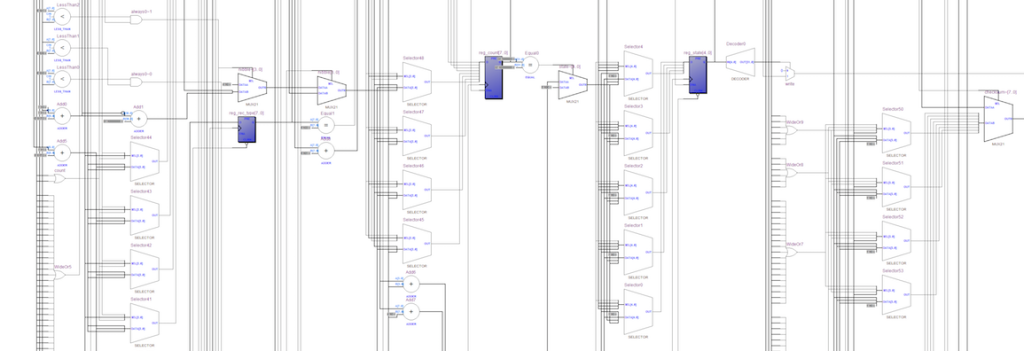

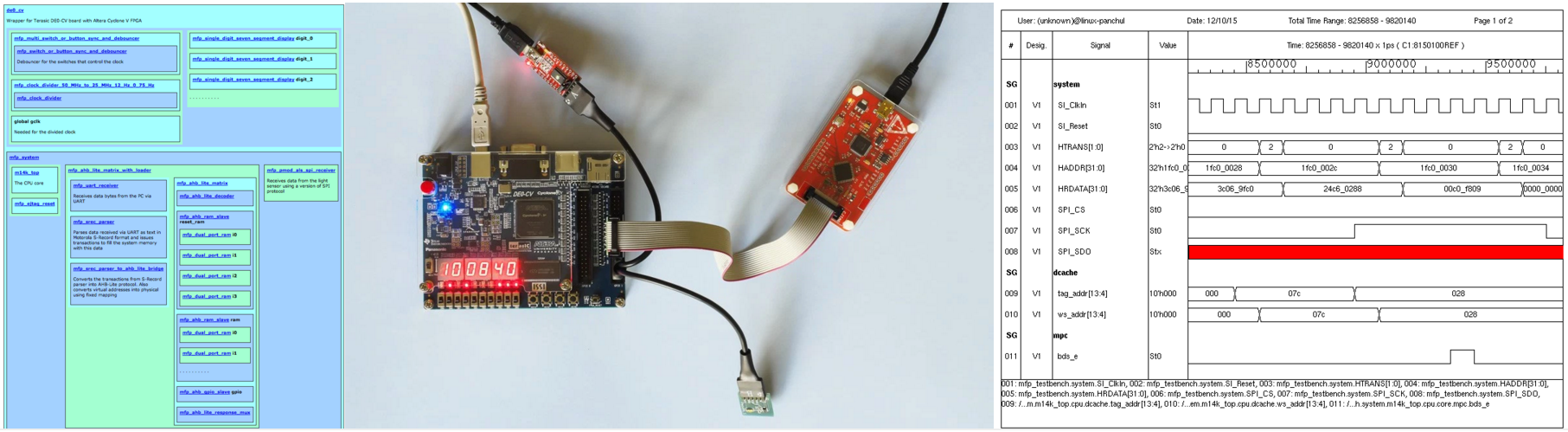

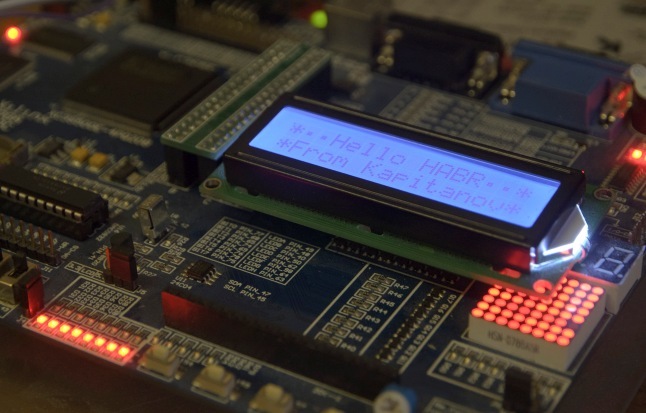

Итого, вырезка из слайдов, чтобы вы поняли, о чем идет речь:

Читать полностью »